(54) ЭЛЕМЕНТ С ТРЕМЯ СОСТОЯНИЯМИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель-формирователь | 1982 |

|

SU1065883A1 |

| Усилитель-формирователь импульсов | 1980 |

|

SU944110A1 |

| Преобразователь уровней напряжения | 1984 |

|

SU1167725A1 |

| Элемент с тремя состояниями | 1978 |

|

SU725235A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Элемент с тремя состояниями | 1978 |

|

SU743200A1 |

| Триггер на взаимодополняющих мдп-транзисторах | 1980 |

|

SU875596A1 |

| Реверсивный счетчик на мдп-транзисторах | 1977 |

|

SU711690A1 |

| Выходное устройство | 1978 |

|

SU771874A1 |

| Устройство формирования импульсов на МДП-транзисторах | 1986 |

|

SU1345339A1 |

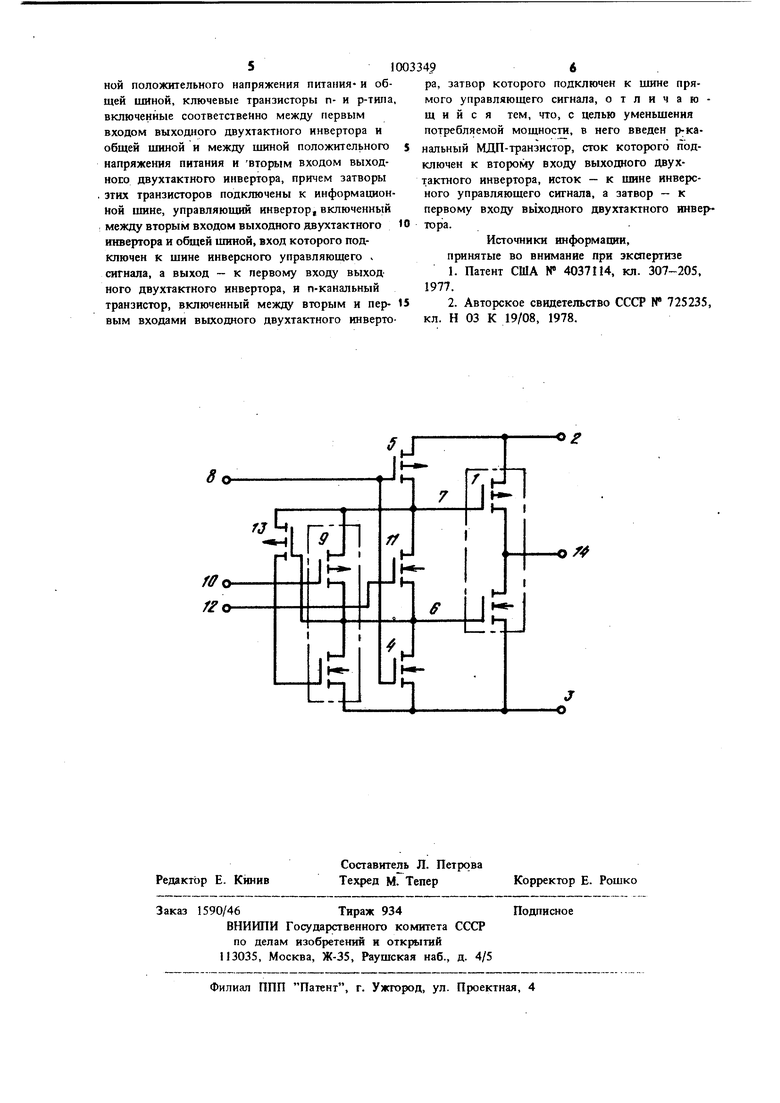

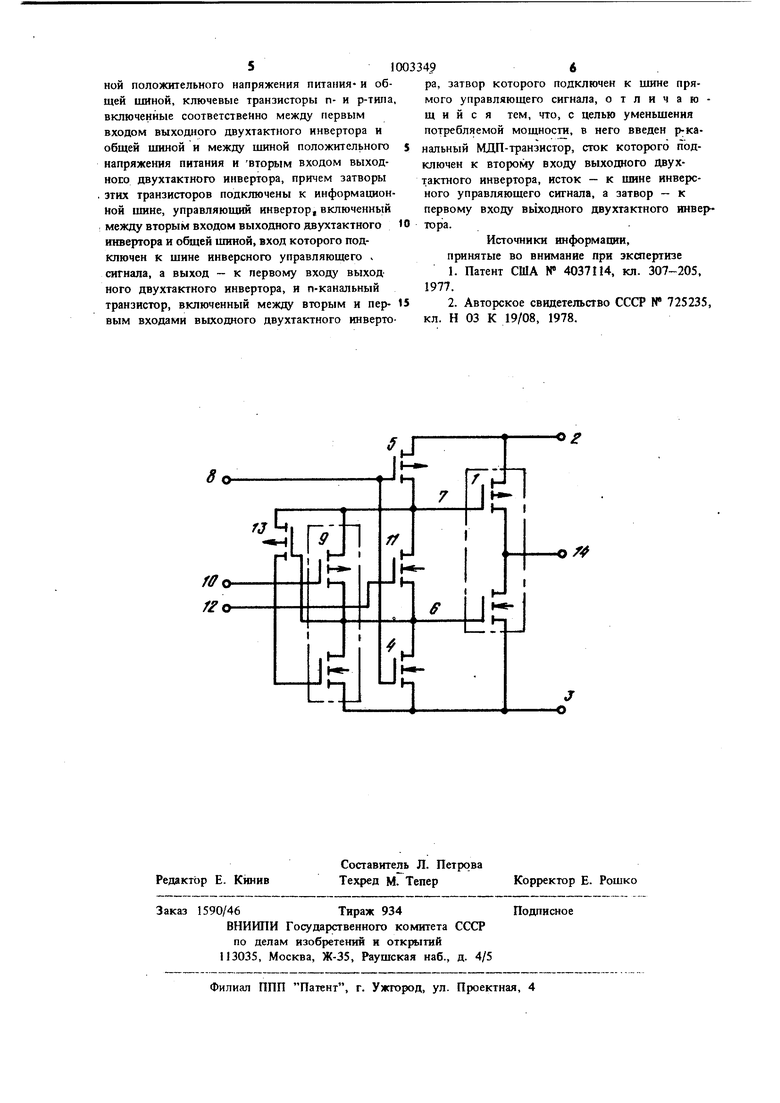

Изобретение относится к вычислительной те)шике и электронике и может быть исполь зовано при создании интегральных схем на МДП-транзисторах в устройствах вывода информации ЗУ, БИС сбора и преобразования информации и БИС мйкропроцессорюв. . Известен элемент с тремя устойчивыми состояниями на дополняющих МДП-транзисторах, содержащий двухтактный выходной каскад и схему управления 1. Недостатком такого элемента является значительная потребляемая мощность, что связано с наличием сквозных токов через ин верторы в режиме переключения. Известен элемент с тремя устойчивыми состояниями на дополняющих МДП-транзисторах, содержащий выходной двухтактный инвертор, включенный между щиной положительного напряжения питания и общей щиной ключевые транзисторы п- и р-типа, включенны соответственно, между первым входом выход ного двухтактного инвертора и общей щиной и между шиной положительного напряжения питания и вюрым входом выходного двухтактного инвертора, причем затворы этих транзисторов подволочены к информационной щине, первый инвертор, включенный между щиной положительного напряжения питания и первь1м входом выходного двухтактного инвертора, второй инвертор, включенный между вторым входом выходного двухтактного инвертора и общей щиной, причем, вход первого инвертора подключён к щине прямого управляющего сигнала, а его выход - к второму входу выходного двухтактного инвертора, вход второго инвертора подключен к щине инверсного управляющего сигнала, а выход - к первому входу выходного двухтактного инвертора {2, Недостатком известного элемента также является значительное потребление мощности, связанное с наличием сквозных токов через первый и второй инверторы при переходе из режима высокого выходного сопротивления в режим передачи информации, независимо от сигнала на информационной щине. Цель изобретения - уменьшение потребляемой мощности. 310 Для досчижения поставленной цели в элемент с тремя состояниями на догюлняющих МДП-1ранзис1орах, содержащий выходной двухтактный инвертор, включенный между шиной положительного напряжения питания и общей шиной, ключевые транзисторы п-и р-типа, вклю ченные соответственно между первым входом выходного двухтактного инвертора и общей щиной и между щиной положительного напряжения питания и вторым входом выходного двухтактного инвертора, причем затворы этих транзисторов подключены к информационной ижне, управляющий инвертор, включенный между вторым входом выходного двухтактного инвертора и общей шиной, вход которого подключен к щине инверсного управляющего сигнала, а выход - к первому входу выходного двухтактного инвертора и п-канальный транзистор, включенный между вторым и первым входами выходного двухтактного инвертора, затвор KOToppiro подключен к щине 1 рямого управляющего сигнала, введен р-канальный МДП-транзистор, сток которого подключен к второму входу выходного двухтактного инвертора, исток к шине инверсного управляющего сигнала, а затвор - к первому входу выходного двухтактного инвертора. На чертеже представлена электрическая принципиальная схема элемента с тремя состояниями на дополняющих МДП-транзисторах. . В элементе выходной двухтактный инвертор 1 включен между щиной 2 положительного напряжения питания и о.бщей щиной 3, . ключевые транзисторы п - и р-типа 4 и 5 подключены соответственно между первым входом 6 выходного двухтактного инвертора 1 и общей щиной 3 и между щиной 2 положительного напряжения питания и вторым входом 7 выходного двухтактного инвертора 1, затворы ключевых транзисторов 4 и 5 подключены к информационной шине 8, управляющий инвертор 9 включен между вторым входом 7 выходного инвертора 1 и общей щиной 3, его .вход подключен к щине 10 инверсного управ ляющего сигнала, а выход - к первому входу 6 выходного инвертора 1, истоке и сток п-канального транзистора И подключены соответственно к первому 6 и второму 7 входам выходного двухтактного инвертора 1, а его затвор подключен к шине прямого управляющего сигнала 12, исток и сток р-канального транзистора 13 подключены соответственно к щине инверсного управляющего сигнала 10 и второму входу 7 выходного двухтактного инвертора 1, а затвор - к выходу управляющего инвертора 9. Вьпсод инвертора I подключен к выходной шине 14. 9 Элемент работает следующим образом. В исходном состоянии (высокое выходное сопротивление), на щины прямого 12 и инверсного 10 управляющих сигналов поступают соответственно логические О и 1 (уровню логического О соответствует потенциал общей щины, а уровню логической 1 - уровень положительного напряжения питания). В результате, на выходе управляющего инвертора 9 устанавливается напряжение уровня логического О, запирающее п-канальный транзистор выходного двухтактного инвертора 1, а р-канальный транзистор выходного двухтактного инвертора 1 запирается напряжением логической , поступающим на его затвор через открытый р-канальный транзистор 13. Тогда пра логическом О на цшне прямого управляющего сигнала и логической 1 на шине инверсного управляющего сигнала, состояние высо ого выходного сопротивления на щине 14 сохраняется, независимо от значения сигнала на информационной шине 8. В режиме передачи информации, на шины 12 и 10 поступают соответственно, логическая 1 и логический О, в результате чего р-канальный транзистор управляющего инвертора 9 и п-канальный транзистор И открываются. При поступлении на информационную шину логической 1 ключевой транзистор 4 открывается, что приводит к Запиранию п-канального и отпиранию р-канального транзисторов выходного двухтактного инвертора 1 и лоявлению на шине 14 уровня напряжения логической 1. При поступлении на информационную ишну уровня напряжения логического О, ключевой дранзистор 5 открывается, а ключевой транзистор 4 закрывается, что приводит к запиранию р-канального и отпиранию п-канального транзисторов выходного двухтактного инвертора 1 и появлению на щине 14 уровня напряжения логического О. Р-канальный транзистор 13 при этом заперт положительным потенциалом на его затворе и стоке относительно истока. При логической 1 на информационной щине 8, изменение сигнала на щинах 10 и 12 (перевод элемента из режима высокого выход.ного сопротивления в режим передачи информации или наоборот), не приводит к протеканию сквозных токов, что обеспечивает более низкую потребляемую мощность по сравнению с известным устройством. Формула изобретения Элемент с тремя состояниями на дополняющих. МДП-транзисторах, содержащий выходной двухтактный инвертор, включенный между щиной положительного напряжения питания- и общей шнной, ключевые транзисторы п- и р-типа включенные соответственно между первым входом выходного двухтактного инвертора и общей щиной и между щиной положительного напряжения питания и вторым входом выходного двухтактного инвертора, причем затворы этих транзисторов подключены к информационной шине, управляющий инвертор, включенный : между вторым входом выходного двухтактного инвертора и общей шиной, вход которого подключен к шине инверсного управляющего . сигнала, а выход к первому входу выход ного двухтактного инвертора, и п-канальный транзистор, включенный между вторым и первым входами выходного двухтактного инвертора, затвор которого подключен к щнне прямого управляющего сигнала, отличающийся тем, что, с целью уменьшения потребляемой мощности, в него введен р канальный МДП-транзистор, сток которого подключен к второму входу выходаого двухтактного инвертора, исток - к шине инверсного управляющего сигнала, а затвор - к первому входу вь{ходного двухтактного инвертора. Источники информации, принятые во внимание при экспертизе 1.Патент США № 4037114, кл. 307-205, 1977. 2.Авторское свидетельство СССР N 725235, кл. Н 03 К 19/08, 1978.

Авторы

Даты

1983-03-07—Публикация

1981-08-31—Подача