1

Изобретение относится к вычислительной технике и может быть использовано при разработке универсальных и специализированных вычислительных машин.

Известен логический элемент исключающее ИЛИ , содержащий восемь МДП-транзисторов, образующих две параллельные ветви. В каждой ветви включены последовательно пара р-канальных транзисторови пара п-канальных транзисторов, на затворы которых поступают соответствующие входные сигналы,. средние точки двух ветвей подключены к выходу элемента 1, Недостатком известного элемента является значительное число компонентов.

Известен логический элемент исключающее ИЛИ на КМ.1П-транэисторах, содержащий инвертор, включенный между шиной питания и общей шиной, двунаправленный клю, р-канальный транзистор и два п-канальных транзистора, выход инвертора подключен к затвору п-канального транзистора двунаправленного ключа, а вход к шине первого входного сигнала, к затвору р-канального транзистора двунаправленного ключа, к затвору

первого п-канального транзистора и к истоку р-канального транзистора, сток которого подключен к выходной шине, к стокам транзисторов дву5 направленного ключа ик истоку первого п-канального транзистора, а затвор - к истокам транзисторов двунаправленного ключа, к шине второго входного сигнала и к затвору второго п-канального транзистора, сток которого подключен к истоку первого п-канального транзистора, а исток - к общей шине 21

Недостатком известного устройст 5 ва является также значительноечисло компонентов, что снижает его надежность.

Цель изобретения - упрощение устройства.

20 Для достижения поставленной цели в логическом элементе исключающее ИЛИ на КМДП-транзисторах, содержащем инвертор, включенный между шиной питания и общей шиной,

25 двунаправленный ключ, р-канальный и п-канальный транзисторы, при этом выход инвертора подключен к затвору п-канального транзистора двунап.равленного ключа, а вход - к шине

30 первого входного сигнала, к затвору

р-канального транзистора двунаправленного ключа и к истоку р-канального транзистора, сток которого подключен к выходной шине и к стокам. транзисторов двунаправленного ключа, а затвор - к истокам транзисторов двунаправленного ключа, к затвору п-канального (Транзистора и к шине второго входного сигнала, сток п-канального транзистора подключается к выходной шине, а исток - к выходу инвертора.

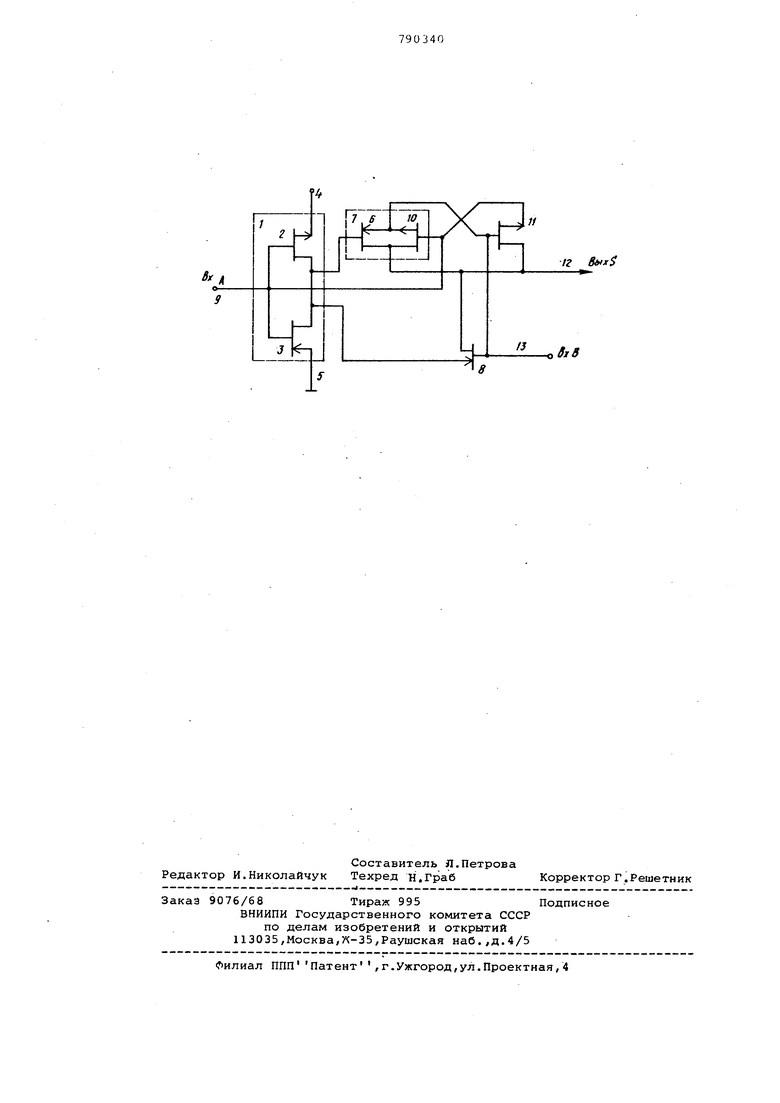

На чертеже представлена электрическая принципиальная схема устройства.

Устройство содержит инвертор 1, образованный р-канальным трназистором 2 и п-канальным тразистором 3 и включенный , между шиной 4 питания и общей шинЪй 5; выход инвертора 1 подключен к затвору п-канального транзистора 6 двунаправленного ключа 7 и к истоку п-канального транзистора 8, а вход - к шине первого входного сигнала А-9, к затвору р канального транзистора 10 двунаправленного ключа 7 и к истоку р-канального транзистора 11, сток которого подключен к выходной шине 12, на которой формируется ВЫХОДНОЙ сигнал S, к стокам транзисторов Ь и 10 и к истоку транзистора8, а затвор - к истокам транзисторов 6 и 10, к затвору транзистора 8 и к шине второго входного сигнала В-13.

Устройство работает следующим об разом.

Если на шине 9 первый входной сигнал Л имеет значение логического О , то транзисторы 2,6 и 10 открыты и на выходной, шине 12 формируетс сигнал, соответствующий значению второго входного сигнала В на шине 13. При этом, если сигнал В имеет значение логического О , то транзистор 11 открыт,(на его истоке и стоке - одинаковый потенциал),а транзистор 6 закрыт; если сигнал В имеет значение логической , то транзистор 6 открыт (на его стоке и истоке одинаковый потенциал), а транзистор 5 закрыт.

Если на шине 9 первый входной сигнал А имеет значение логической , то транзисторы 2,6 и 10 закрыты. При этом, если на шине 13 второй входной сигнал В имеет значеО

то транзистор

ние логического

11 открыт, а транзистор 8 закрыт, и на выходной шине 12 выходной сигнал S имеет значение логической

если же второй входной сигнал В имеет значение логической

1 , то транзистор 11 закрыт, а транзистор 8 .открыт, и на выходнойшине сигнал S имеет занчение логического О,.

Работа устройства соответствует функциональной таблице.

Б

Уменьшение числа транзисторов и тем самым числа связей в предлагаемом устройстве позволяет обеспечить большую надежность и достич большей степени интеграции.

Оормула изобретения

Логический элемент исключающее ИЛИ на КВДП-транзисторах, содержащий инвертор, включенный между

шиной питания и общей шиной, двунаправленный ключ, р-канальный и п-канальный транзисторы, при этом выход инвертора подключен к затвору п-канального транзистора .двунаправленного ключа, а вход-- к шине первого входногр сигнала, к затвору р-канального транзистора двунаправленного ключа и к истоку р-канального транзистора, сток которого подключен к выходной шине и к стокам транзисторов двунаправленного ключа, а затвор - к истокам транзисторов двунаправленного ключа, к затвору п-канального транзистора и к. . шине второго входного сигнала, о тличающийся тем, что, с целью упрощения, сток п-канального транзистора подключается к выходной шине, а исток - к выходу инвертора.

0

Источники информации, принятые во внимание при экспертизе

1.Валиев К.А., Кармазинский A.M. Цифровые интегральные схемы на ВДПтранзисторах. М., Сов. радио ,

5 1971, с. 274.

2.Патент США 3668425, кл. 3072.16, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Элемент с тремя состояниями | 1982 |

|

SU1051721A1 |

| D-триггер на КМДП-транзисторах | 1990 |

|

SU1728963A1 |

| УСТРОЙСТВО ВОССТАНОВЛЕНИЯ УРОВНЯ СИГНАЛА В СХЕМАХ С ПРОГРАММИРУЕМОЙ КОММУТАЦИЕЙ | 2011 |

|

RU2469472C1 |

| Д-триггер | 1985 |

|

SU1309267A1 |

| Элемент с тремя состояниями | 1978 |

|

SU743200A1 |

| Согласующее устройство на мдптранзисторах | 1976 |

|

SU708512A1 |

| Логический элемент "исключающееНЕ-или" HA Мдп ТРАНзиСТОРАХ | 1979 |

|

SU797074A1 |

| УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ УРОВНЕЙ ЛОГИЧЕСКИХ СИГНАЛОВ НА КМОП-ТРАНЗИСТОРАХ | 1993 |

|

RU2085030C1 |

| Логический элемент Исключающее ИЛИ | 1982 |

|

SU1072264A1 |

| Делитель частоты с дробным коэффициентом деления кратности 0,5 | 1979 |

|

SU788387A1 |

Авторы

Даты

1980-12-23—Публикация

1979-01-10—Подача