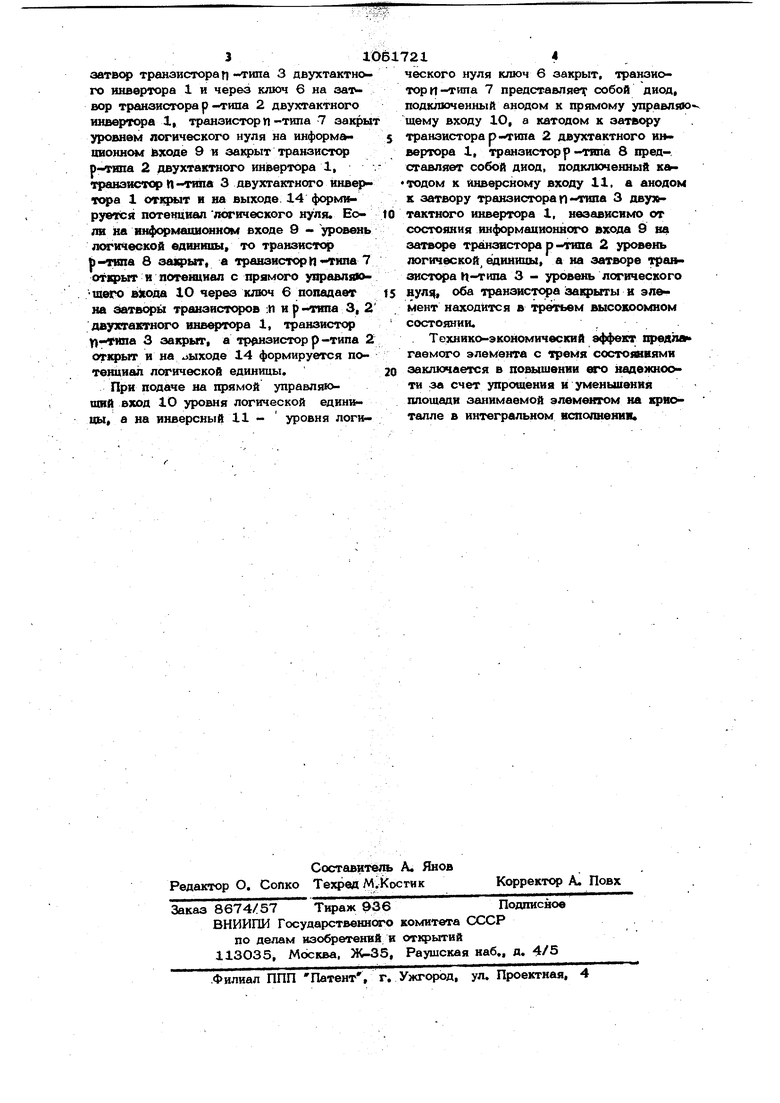

Изобретение относится к вычислител ной технике и электронике и может быт использовано при соаяаят интегральных и дискретных схем на дополняющих МДП транзисторах в качестве выходного ключ усилителя для непосредственного объеди нения с выходными каскадами других схем при организации магистрального обмвтла В частности, элемент может быть использован в устройствах вывода им|юрмааия статических ЗУ и БИО-микропркхкессоров. Известен элемент с тремя состояния ми на дстолняющих МДП-транзисторах, содержащий выходной двухтактный инвер тор, включенный между шиной пиФания и обшей шииоД и симметричную схему управления IX) Недостатком даннсиго элемента является значительная потребляемая моиь кость в режиме третьего состояния. Наиболее близкий i; проалагаекюму п технической суошости является элемент с тремя состояниями на дополняющих МДП-транзисторах, соаержащий дву тактный инвертор на комплиментарной паре МДПигранзисторс, включенный между шиной питания и обшей шиной, .двунахфавленный ключ, включенный, между входами двухтактного инверт чэа, первый и второй МДП-травзистрчры -ти па, первый « второй ЛШП-транзисторы )-.ТИШ1, причем истоки первого и вторся о транзисторов подключены кшине питания, а стоки - к затвору р-транзистора двухтактного инвертфа, истоки первого и второго транзисторов подключены к обшей шине, а сто ки - к затвору П -транзистора двухтактного инвертора, затворы первого транзистора р-типа и первого транзистора Гь-типа соединены и подключены к инфор мационному входу элемента, затвс вто рого транзистора р -типа с оединен с зат вором тран сторап-типа ключа и подключен к прямому управляюшему входу элемента, затвс второго транзистора П-типа соединен с затвором транзистора р-тйпа ключа и подключен к инверсному управляюшему входу элемента, вы ход двухтактного инвертора является выходом элемента 2Q . Однако данный элемент характеризует ся наличием большого количества транзисторов, что 1ФИВОДИТ к снижению надежности. Цель изобретения - повышение наде) ности. 21 Для достижения поставленной цели в элементе с тремя состояниями, содержашем двухтактный инвертер на компл ментарной паре МДГРгранзисторов, включенный между шиной питания и обшей шиной, двунаправленный ключ, включенный меиоду входами двухтактного инвертора и МДП-транэисторы п-типа и ti--THna, затворы которых объединены и подклк чены к информационному входу элемента, затвор МДП-транзистора ключа соединен с { рямым, а затвор МДИ-транзистора h -типа с инверсными у1фавля1ошими входами элемента, исток MHIV ч. транзистора Ц-типа соепинен с его подложкой и с пр$1мым, а- исток МДПтранзистора р-типа соединен с его подложкой и с инверсным управляюшим вхо дом элемента соответственно, стоки . этих транзисторов подключены к затво. рам АШП-транаисторов р- и rf- типа двухтактного инвертора. На чертеже представлена электриче6.« кая принципиальная схема устройства. Устройство содержит двухтактный 1 на комплиментарной паре МДПтранзисторов 2 и 3 включен между ш|ьной 4 питание и хэбшей шиной 5, двун1а1 равленный ключ 6, включен межау входами двутсгактного инвертора 1, эач воры МДП-транзисторов II-типа, 7 и р -типа S соединены и подключены к Информационному входу 9 элемента, исток транзистора il-типа 7 соединен с его подложкой и с прямым ухфавляюшим входом 1О элемента, а его сток - с затвором транзистора р-типа 2 явутбтактного инвертора 1. Исток транзисторар-типа 8 соединен с его подложкой, с инверюным управл5 1Ошим входом 11 элемента и с Транзистора и-типа 12 ключа 6, затвор транзистора р -типа 13 ключа 6 соединен прямым упр«шляюшим входом lOv элемента, выход двухтактного инверто ра 1 подключен к выходу 14 элемента. Элемент с тремя состояниями работает следуюшим образом. При подаче на прямой управлтоший вхоа 1О уровня логического нуля, а на инверсный управляюший вход 11 уровня логической единицы, ключ 6 открыт, так как на затворы его транзисторов 12 и 13 поступают открывающие потенциалы, если на информационном входе эле- Мента 9 - уровень л агического нуля, то открыт транзистор h-типа 8, через него хютенциал логической единицы с инверсное го. управляющего входа 11 попадает на аагвар транзистораn -типа 3 двухтактно го инвертора 1 и через ключ 6 на за-рвор транзистора р -типа 2 двухтактного инвертора 1, транзистор п-типа 7 закры уровнем логического нуля на информационном Ьходе 9 и за1фыт транзистсф 2 двухтактного инвертора 1, оранзистор И -типа 3 двухтактного инвер 1 OTiqfMtiT и на выходе. 14 формируется потенциаллогического иупя. Если на информационном входе 9 - уровень жя ической единицы, то транзистор |)-Т1ша 8 закрыт, а транзистор ц о-типа 7 отцрыт и поте}шиал с прямого управляло щего в)ЕОда Ю через ключ 6 попадает на затворы транзисторов :ii и р -типа 3, 2 двухтактного инвертора 1, транзистор yj-twia 3 закрыт, а трдазистор р -типа 2 ОТ1ФЫТ и на уыходе 14 формируется потенциал логической единицы. При подаче на 1фямой управляющий вход 10 уровня логической единицы, а на инверсный 11 - уровня логического нуля ключ 6 закрыт, транзиоторп- ипа 7 представляет собой диод, подключенный анодом к прямому управляющему входу 1О, а катодом к затвору транзистора р-типа 2 двухтактного HI вертора 1, транзист ч р-типа 8 представляет собой диод, подключенный катодом к инверсному входу 11, а анодом к затвору анзистора п-типа 3 двухтактного инвертора 1, независимо от состояния информационного входа 9 на )е транзистора р-типа 2 уровень логической, единицы, а на затворе транзистора Н-типа 3 - уровень логического нул$, оба транзистора закрыты н элемент находится в третьем высокоомном состоянии. Технико-экономический аффект щюял гаемого элемента с тремя состояниями заключается в повышении «ю надежнооти за счет упрощения и уменьшения площади занимаемой элементом на кристалле в интегральном исполнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Элемент с тремя состояниями | 1981 |

|

SU1003349A1 |

| Элемент с тремя состояниями | 1978 |

|

SU743200A1 |

| Элемент с тремя состояниями | 1978 |

|

SU725235A1 |

| Управляемый мажоритарный элемент | 1981 |

|

SU993479A1 |

| КОМПЛЕМЕНТАРНЫЙ МИКРОЭЛЕКТРОМЕХАНИЧЕСКИЙ ИНВЕРТОР | 2005 |

|

RU2290753C1 |

| @ - @ -Триггер на МДП-транзисторах | 1985 |

|

SU1262697A1 |

| @ -Триггер с предпочтительной установкой в @ -состояние | 1982 |

|

SU1075380A1 |

| Триггер на МПД-транзисторах | 1984 |

|

SU1223349A2 |

| Многоканальный коммутатор | 1984 |

|

SU1220124A1 |

| Управляемый махоритарный элемент на комплементарных МДП-транзисторах | 1982 |

|

SU1034191A1 |

ЭЛЕМЕНТ С ТРЕМЯ СОСТОЯНИЙМИ, содеришший двухтактный инвертор на комплиментарной паре МДП-транзисторов, вкл10 енный между шиной питания и обшей шиной, двунаправленный ключ, включенный между входами двухтактного инвертора и МДП-транзисторы р-тила и П-типа, Затворы которых объединены в подключены к информааи я - ному входу элемента, затвор МДП-тра зистора р-типа ключа соединён с пр$1мым. а затвор МДП-транзистора h -типа с инверсными управляющими входаьт элемента, отличающийся тем, что, с целью повышения надежности, исток МДП-транзистора } -типа соединен с его подложкой и с прямым, а исток МДП-транзистора р-тнпа соединен с его подложкой и с управляющим входом элемента соответственно, стоки этих транзисторов подклю 1ены к затворам МДП-транзист ч ов р- и я - типа двухтактного инвертора. (Л

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Элемент с тремя состояниями | 1978 |

|

SU725235A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

Авторы

Даты

1983-10-30—Публикация

1982-07-28—Подача