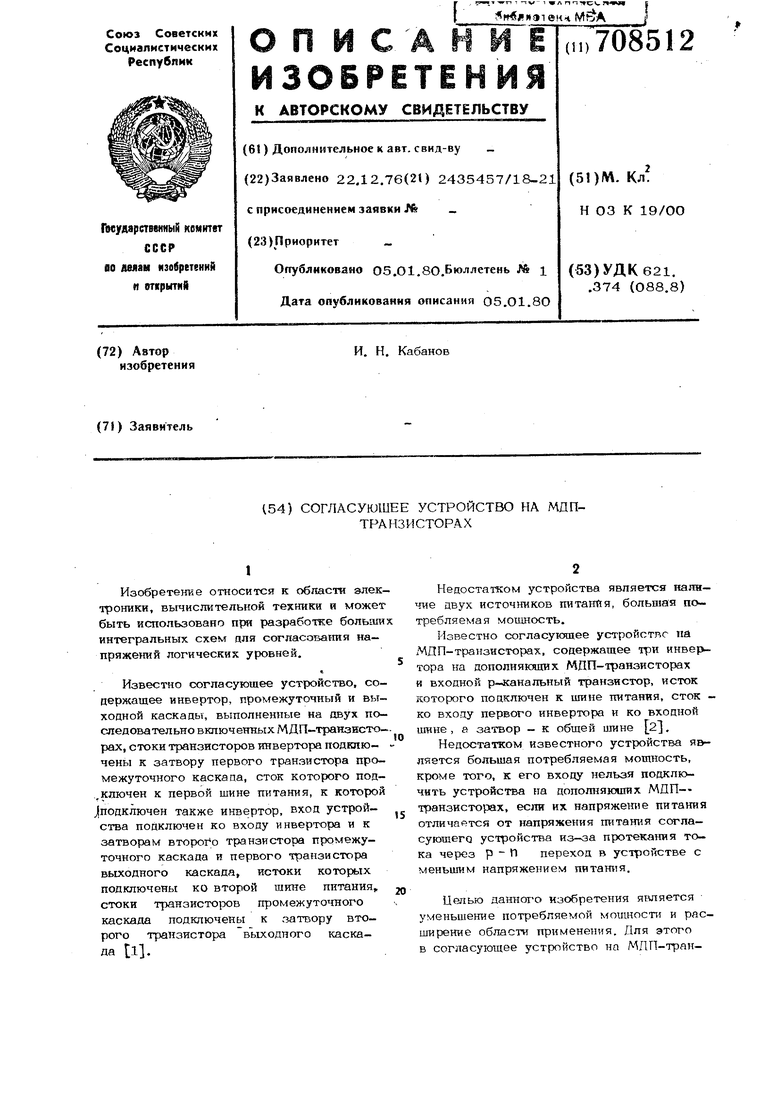

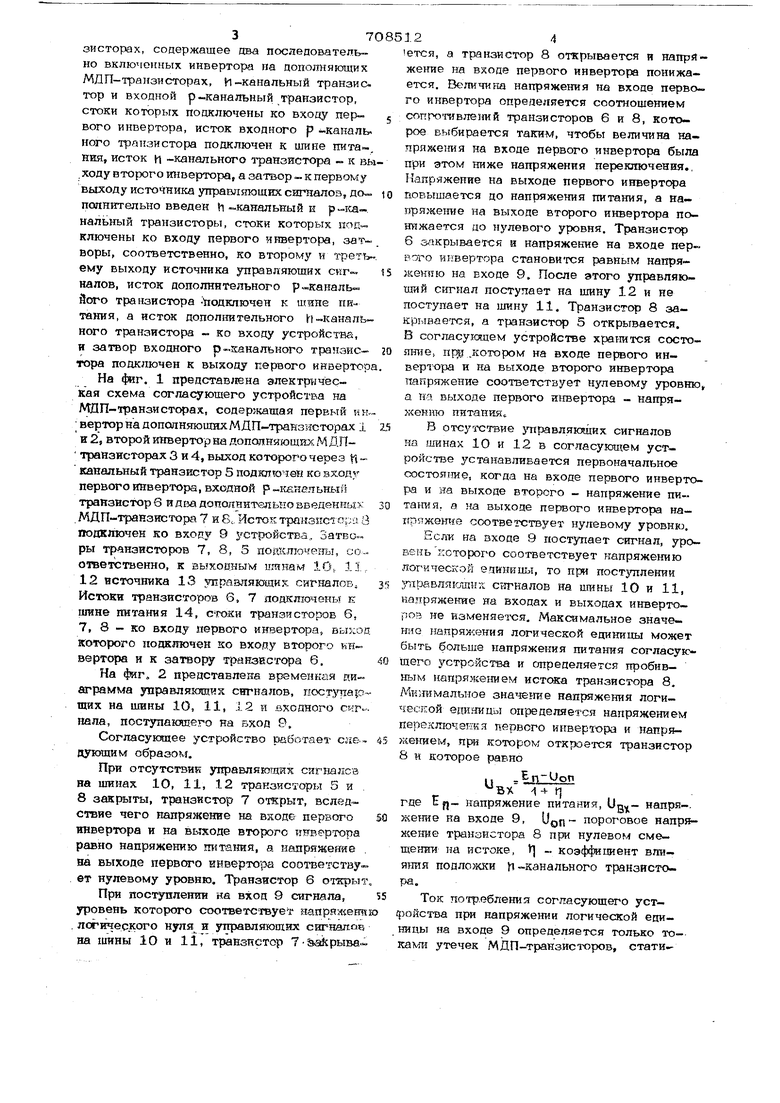

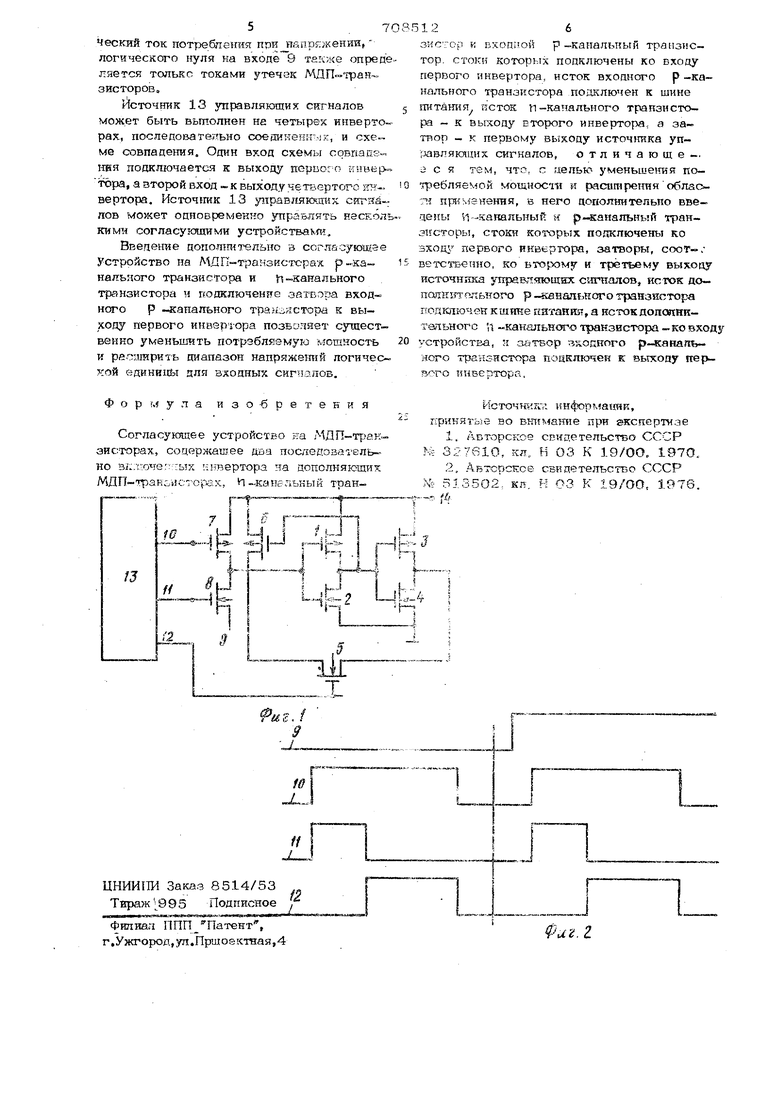

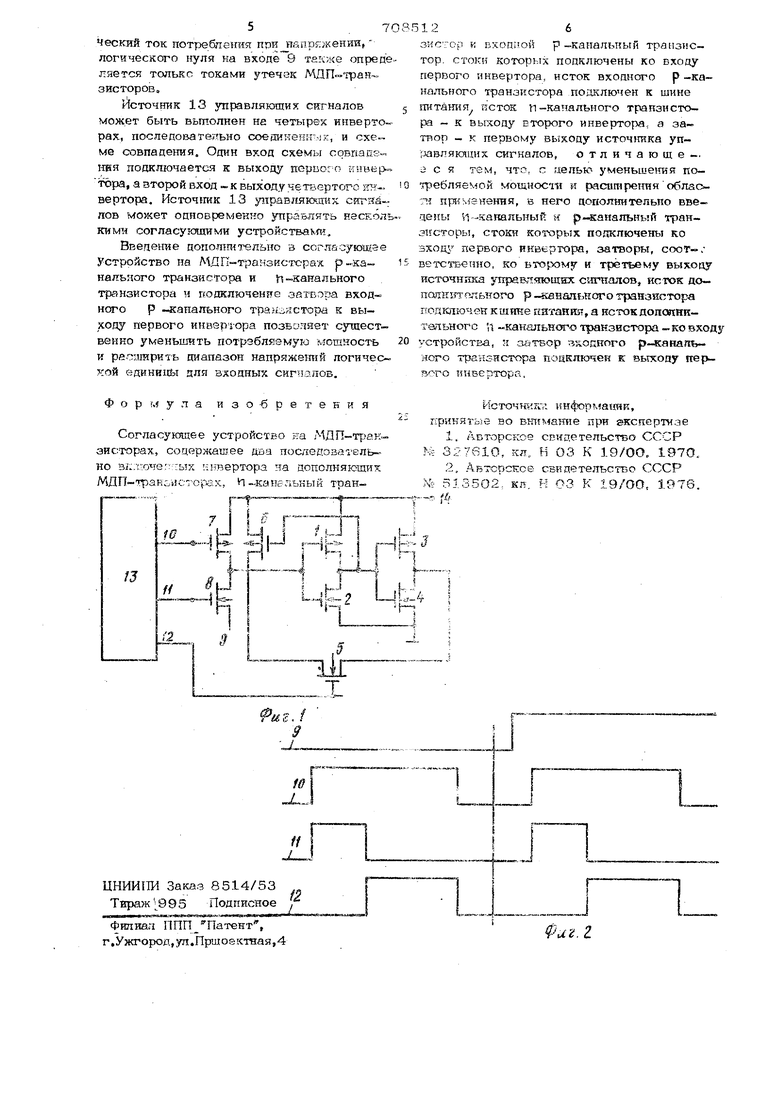

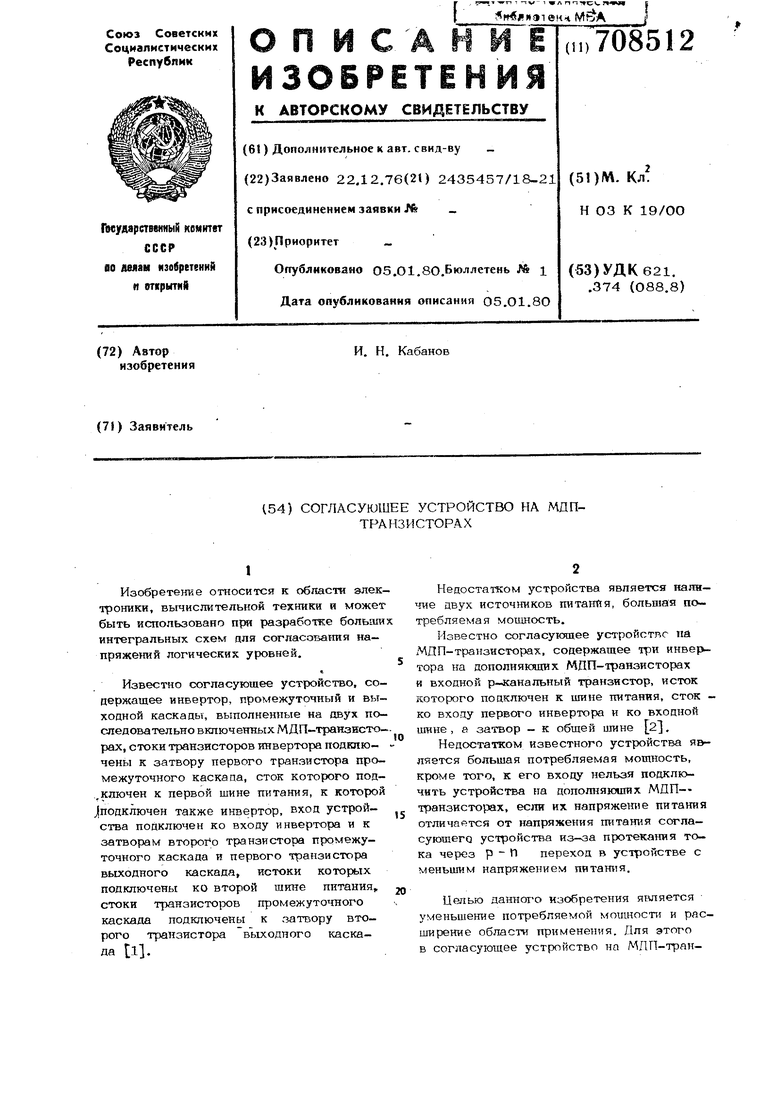

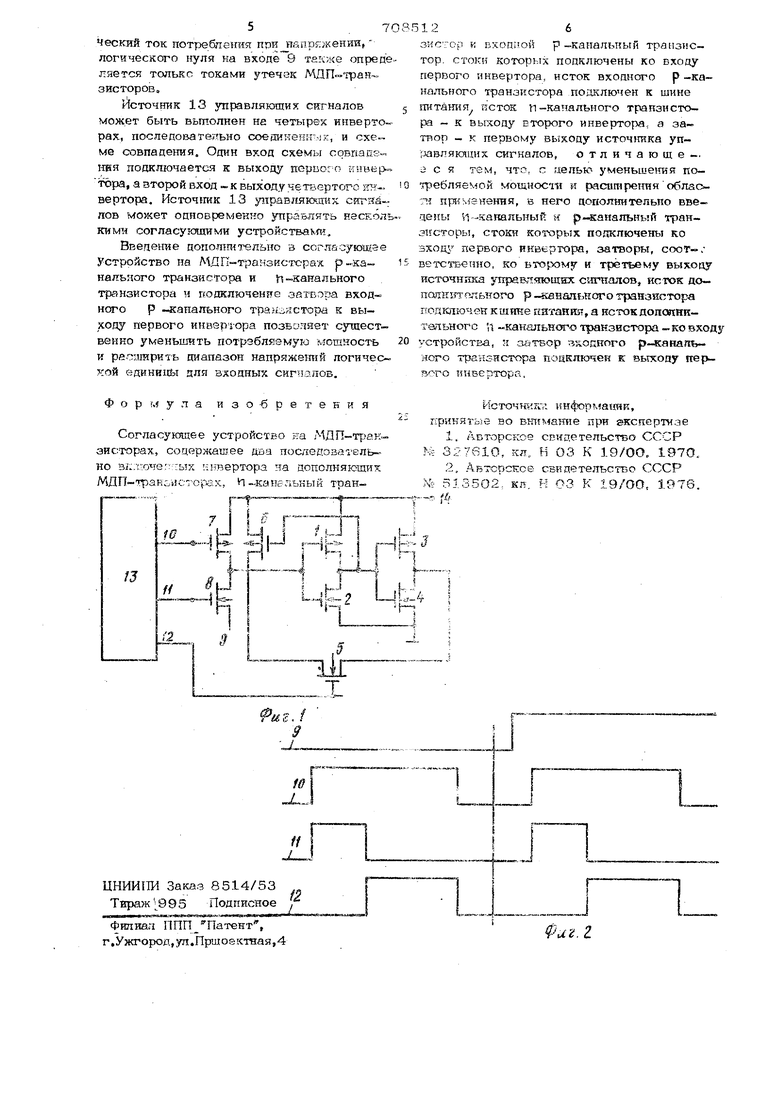

зисторах, содержащее два последовательно включенных инвертора на дополняющих МДП-транзисторах, И-канальный транзис. тор и входной р-канальный транзистор, стоки которых подключены ко входу первого инвертора, исток входного р -каналь. ного трпт зистора подключен к ишне пита, НИН, исток и -канального афанзистора - к вы .ходу второго инвертора, а затвор - к первому выход у источншсауправл тощих сигналов, дополнительно введен И-канальный н р-дШнальный транзисторы, стоки которых поцключены ко входу первого инвертора, затворы, соответственно, ко второму и треть ему выходу источника управляюших сиг налов, исток дополнительного р- аналь його транзистора - тодключен к шине пктания, а исток дополнительного И канального транзистора - ко входу устройства, и затвор входного р-ханального транзнс- тора подключен к выходу первого инвертора На фиг. 1 представлена электрическая схема согласующего устройства на Mnri-ipaHSHстеках, содержащая первый кн вертор на дополняющих М ДП-транзисторах 1 и 2, второй шюертор на допсшняющих М ДП транзисторах 3 и 4, выход которого через Н канальный транзистор S подключен ко входу первого инвертора, входной р-хкнельный файзистор 6 я два допо/шит эльно введенных МДП-транзистор 5 7 и 8с, Исток троизис о;;а в подключен ко входу 9 устройства. Затворы транзисторов 7, 8, 5 поаключезы, соответственно, к выходным итянам 10, 11, 12 источника 13 шравляющик сигналов; Истоки транзисторов 6, 7 подключены к нгане питания 14, стоки транзисторов б, 7, 8 - ко входу первого инвертора, выхов. которого подключен so входу второго инвертора и к затвору транэЕстора 6, На фиг. 2 представлена временная диаграмма управляющих сигналов, nccTynaio щих на шины 10, 11, 12 и входного . нала, поступакяЕбго на вход 9, Согласуияяее устройство работает еле. дующим образом. При отсутствии управляю дяк сягналсв на шинах 10, 11, 12 транзисторы 5 и 8 закрыты, т;к1нзкстор 7 о-трыт, вследствие чего напряжение на входе- первого инвертора и на выходе второго инвертора равно напряжению ггитания, а напряжеяие . на выходе первого ЕНверто эа соответствует нулевому уровню. Транзистор 6 открыт При постуилетга на вход 9 сигнала, уровень которого соответствует напряжени . логического нуля и уттравляюших сйгналор, на шины 10 и 11, транзкетор 7aakpbiBa.ется, а транзистор 8 открывается и напряжение на ВХОДИ первого инвертора понижается. Величигщ напряжения на входе первого инвертора определяется соотношением сопротивлений транзисторов 6 и 8, которое выбирается таким, чтобы величина напряже шя на входе первого инвертора была при этом ниже напряжения переключения., Напряжение на выходе первого инвертора повышается до напряжения питания, а напряжение на выходе второго инвертора понижается до нулевого уровня. Транзистор 6 з-пкрываетсй и напряжение на входе первото инвертора становится равным напряжеыню на входе 9. После этого управляющнй С11гиал поступает на шину 12 и не поступает на цгину 11. Транзистор 8 закрывается, а транзистор 5 открывается. В согласующем устройстве хранится состояние, .котором на входе первого ин- вертора и на выходе второго инвертора напряжение соответствует нзшевому уровто, а на выходе первого инвертора - напряжению питания В отсутствие 5Т1равляющих сигналов на шинах 10 и 12 в согласуюидам устройстве устанавливается первоначальное состояюте, когда на входе первого инвертора и на выходе второго - напряжение питаггая. а на выходе первого инвертора на- ггряжешге соответствует нулевому уровню. Есл-и на входе 9 поступает сигнал, уровень которого соответствует напряжению логической единицы, то яри поступлении ;таравля -ощих Ct-ггналов на иганы 10 и 11, напряжение на входах и выходах инверторов не изменяе1х;я. Максимальное значение напряжения логической единицы может быть больше напряжения питания согласующего устройства и определяется пробивным напряжением истока транзистора 8. Мклвмальное значе гее напряжения логической единицы определяется напряжением перехлючеккя первого инвертора и напряжением, при которо. откроется транзистор 8 и которое равно . ВХ -1-+ t где Ef}- напряжение питания, напря-, же1ше на входе 9, Ugn пороговое напряхдание транзистора 8 при нулевом смешении на истоке, V . коэффициент подложки Ц-канального транзистора. Ток потр.ебления согласующего уст- )ойства при напряжении логической единицы на входе 9 определяется только токами утечек МДП-транзисторов, стати57Ческий ток потребления при напряжении, логического нуля на входе 9 также опрепе ЛЯ8ТСЯ только токами утечак зисторов. Источник 13 управляющих СЕгналов может быть вьтолнен на четырех инвертоpax, последовательно соеаике пг-;к, и схеме coBnaaeirafl. Один вход схемы соБпаце-. нвя подключается к выходу первого кивертора, а второй вход -к выходу четн.ертого ет вертора. Источник 13 управляющих сигяй- ЛОБ может оцновремекно управлять насЕоль кими согласующими устройствакт, Введеьгае попотттепыю в соглаоуюшае Устройство на МДП-тракзистсрах р-канального транзистора и li-канального транзистора и подключение .затвора входного р -канального траызясгора к выхону первого инвертора позволнет сучаественно уменьшить потрэблЕвмую мошность и рйС;.1гарить диапазон напряжет1Й логичес- кой единицЬт для входных сигналов. Формула и 3 о -б р е т 8 н и я Согласуюлиее устройство на МДП-тракзисторах, соцержашее даа поС|1ейоза1ель-. но зк:- очег::гых инвертора на дополняющих МДП-тран;..исторах, И-каИсЛькый транJ( Ц Г /,J 1 .м -J. 1.«-3g:-.-4 --l..-- i/ П H I h i I h , .. .|.««™,-.,K,-...,«™«са™л ;4„™.-.,., iJI |JI LJ I IL.. Ml.;2пр 1-к №

( 1 26 зистор к Бхоц:юй р-канальный транзистор, стоки которых подключены ко входу первого инвертора, исток входного р -канального транзистора подключен к шине питания исток ц-канального транзистора - к выходу второго инвертора, а затвор - к первому выходу источника уп(завпяющих сигналов, отличающе-. э с я тем, что, с целью уменьше1шя потребляемой мотдносш и расигаренияобласп прима нения, в него цогюянительпо введены И-какаяьный и р- анаяьный транзт сторы, стоая коахэрых подключены ко вхощ первого инвертора, затворы, соог-; ветстЕ-еино, ко втором г и третьему выходу источника управляющих сгтгналов, исток до- пшхкитольного р -канального транзистора пояютючен кшике питаниз, а ксток допоянпГэяьного ,1 -канальнсго транзистора - ко входу устройства, ji .затвор зкоккого р-каналь- него транзистора подключен к выходу первого инвертора. ЙС7Х5ЧНИ5.Т. , инятые во BHTTMamie при експертиэе 1,. ABTvOpcKoe свидетельство СССР 327610, кл. Н 03 К 19/ОО. 197О. 2, Авторское свидетельство СССР 5135О2. кл, н ОЗ К 19/00, 1976.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент | 1977 |

|

SU627593A1 |

| Элемент с тремя состояниями | 1978 |

|

SU743200A1 |

| Элемент с тремя состояниями | 1982 |

|

SU1051721A1 |

| Логический элемент | 1977 |

|

SU627594A1 |

| Элемент с тремя состояниями | 1981 |

|

SU1003349A1 |

| Устройство согласования ТТЛ-элементов с МДП-интегральными элементами | 1982 |

|

SU1064469A1 |

| Преобразователь уровней напряжения на дополняющих МДП-транзисторах | 1983 |

|

SU1129739A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

| Тактируемый @ -триггер | 1985 |

|

SU1267590A1 |

| Преобразователь уровней напряжения | 1984 |

|

SU1167725A1 |

Авторы

Даты

1980-01-05—Публикация

1976-12-22—Подача