го соединен с информационным входом второго регистра микрокоманд, вход сброса которого соединен с входом начальной установки второго блока формирования адреса, с входом начальной установки микропроцессора и с входами сброса первого и второго 1К-триггеров блока коррекции фазы, входы синхронизации которых соединены с первыми входами первого и .второго элементов И блока коррекции фазы, с входами синхронизации первого, второго и третьего 1К-триггеров блока формирования временных интервлов и с входом синхронизации микропроцессора, I- и К-входы первого и второго триггеров блока коррек1Ц1И .фазы подключены соответственно к шине единичного потенциала и к выходу первого элемента И блока управления формированием следующего адреса, единичный и нулевой выходы первого 1К-триггера блока коррекции фазы подключены соответственно к первым входам первого и второго сумматоров по модулю два блока коррекции фазы,вторые входы которых соединены с единичным выходом второго 1К-триггера блока коррекции фазы, выход первого сумматора по модулю. два блока коррекции фазы соединен с вторым входом первого элемента И блока коррекции фазы, выход которого соединен с входаь« синхронизации второго регистра микрокоманд и второго блока моди4мкации адреса, выход второго сумматора по модулю два блока коррекции фазы соединен с управляющими входами первого и второго мультиплексоров и с вторым входом второго элемента И блока коррекции фазы, выход которого соединен с входаки синхронизации первого регистра микрокоманд и первого блока модификации адреса, первый, второй и третий управляющие входы которого соединены соответственно с выходами первого элемента ИЛИ блока управления формированием следующего адреса, второго элемента И блока управления формированием следующего адреса и первого Элемента ИЛИ-НЕ блока управления формированием следующего адреса, первый, второй и третий угфавляющие входы второго блока модификации адреса соединены соответственно с вйходами второго, третьего элементов ИЛИ блока управ.ления формированием следующего адреса и второго элемента ИЛИ-НЕ блока управления формированием следующего адреса, первый информационный вход первой группы второго мультиплексора соединен с первым выходом признака перехода первого регистра микрокоманд, с инверсным входом третьего элемента И блока управления формированием следующего адреса, с первым входом четвертого элемента И блока управления формированием следующего адреса и с первым инверсным входом пятого элемента И блока управления фop «poвa шeм следующего ад - реса, выход которого соединен с пер%1ми входами первого элемента ИЛИ блока управления формированием следующего адреса и первого элемента ИЛИ-НЕ блока управления формированием следующего адреса, второй вход которого соединен с вторым входом первого элемента ИЛИ блока управления формированием следующего адреса, с первым входом третьего элемента ИЛИ блока управления формированием следующего и с первым выходом первого дешифратора блока управления формированием следующего адреса, вход которого соединен с вторым входом признака перехода первого регистра микрокоманд и с вторым

;информационным входом первой группы второго культиппекссра, первый- информационный вход второй группы которого соединен с первым выходом признака перехода второго регистра микрокоманд, с первым входом шестого элемента И блока управления формированием следующего адреса и с инверсным входом второго элемента И блока управления формированием следующего адреса, первый вход которого соединен с .Iм входом третье го элемента И блока управления формированием следующего адреса, с выходом седьмого элемента И блока управления формированием следующего адреса и с 1-входом nejpBoro 1К-триггера блока формирования временных интервалов, второй информа1щонный вход второй группы второго мультиплексора соединен с вторым выходом признака перехода второго регистра микрокоманд и с входом, второго деши4ратора блока управления формированием следующего адреса, первый выход которого соединен с первыми входами

второго элемента ИЛИ блока управленн формированием следующего адреса и второго элемента ИЛИ-НЕ блока управлния формированием следующего адреса, второй вход которого соединен с вторым выходом второго дешифратора блока управления формированием следущего адреса, с вторым входом второго элемента ИЖ, блока управления фоформированием следующего адреса и с третьим входом первого элемента ИЛ блока управления формированием следующего адреса, четвертый вход которого соединен с третьим входом первого элемента ИЛИ-НЕ блока управлени форьированием следующего адреса, с выходом четвертого элемента И блока управления формированием следуюп его адреса и с вторым входом третьего элемента ИЛИ блока управления формированием следующего адреса, третий вход которого соединен с третьим входом второго элемента ИЛИ блока управления формированием следующего адреса, с выходом шестого элемента И.блока управления формированием следующего адреса, с третьим входом второго элемента ИЛИ-НЕ блока управления формированиемследующего адреса и с прямым входом восьмого элемента И блока управления формированием следующего адреса, выход которого соединен с пятым входом первого элемента ИЛИ блока управления формированием следующего адреса, шестой вход которого соединен с четвертым входом первого элемента ИЛИНЕ блока управления формированием следукмцего адреса и с вторым выходом первого дешифратора блока управления формированием следукяцего адреса, выход первого 1К-триггера блока формирования временных интервалов соединен с 1-входом второго 1К-триггера блока формирования временных интервалов, с первым входом элемента ИЛИ блока формирования временных интервалов, со стробирующим входом третьего дешифратора блока управления формированием следующего адресате вторыми входами четвертого и шестого элементов И блока управления формированием следующего адреса и с прямым входом пятого элемента И блока управления формированием следующего адреса, второй инверсный вход . которого соединен с инверсным входом восьмого элемента И блока управления формированием следующего адреса, с К-входами первого и второго 1К-триггеров блока формирования временных интервалов и с выходом второго 1К-триггера блока формирования

.временных интервалов, 1-вход третьего 1К-триггера блока формирования временных интервалов соединен с первым выходом третьего дешифратора блока управления формированием следующего адреса, второй выход которого соеданен с первымн входами первого и седьмого элементов И блока управлення фор1Ф1рованием следующего адреса, вторые входы которых соединены соответственно с первым выходом второго мультиплексора и выходом блока проверки условий, второй выход второго мультиплексора соединен с входом третьего дешифратора блока управления формированием следующего адреса, выход третьего элемента И блока управления формированием следующего адреса соединен с четвертым входом третьего элемента ИЛИ блока управления формированием следующего адреса, К-вход и выход третьего IK. триггера.блока формирования временных интервалов соединены с вторым входом элемента ИЖ блока формирования временных интервалов, выход которого соединен с входом останова операционного блока.

2. Микрогфоцессор по п. I, отличающийся тем, что каждый из блоков моди(}икации адреса содержит регистр, сумматор и три мультиплексора, причем группа выходов первого мультиплексора соединена с первой группой входов сумматора и является группой выходов блока, первый информационный вход первого мультиплексора соединен с выходом регистра, информационный вход которого соединен с выходом второго мультиплексора, первый информационный вход которого соединен с выходом сумматора, вторые информационные входы первого и второго мультиплексоров соединены с выходом

третьего мультиплексора, первый и второй информационные входы которого являются соответственно первым и вторым информационным входа и блока, -вход синхронизагц и регистра и вход сброса регистра являются соответственно входом синхронизации

блока и входом начальной установки блока, управляющие входы первого, второго и третьего мультиплексоров являются соответственно первым, вторьм и третьим управлякнцими входами блока, вход младшего разряда второй группы входов сумматора подключен к шине единичного потенциала, остальные входы второй группы сумматора подключены к шине нулевого потенциала,

3. Микропроцессор по пп. 1 и 2, отличающийся тем, что

721

блок проверю условий содержит мультиплексор по модулю два, причем группа информационных входов мультиплексора является группой информационных входов блока, выход мультиплексора соединен с первым входом сумматора по модулю два , выход которого является выходом блока, управляющие входы мультиплексора и второй вход сумма тора по модулю два являются управляющими входами группы блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1984 |

|

SU1257657A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Микропроцессор | 1984 |

|

SU1179363A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропроцессор | 1985 |

|

SU1273939A1 |

| Устройство управления микропроцессором | 1983 |

|

SU1156072A1 |

| Микропрограммный процессор | 1982 |

|

SU1037264A1 |

| Устройство для контроля хода микропрограмм | 1987 |

|

SU1430959A1 |

| Микропроцессор | 1982 |

|

SU1037263A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1179339A1 |

I . МИКРОПРОЦЕССОР, содержащий операционный блок, первый блок модис кации адреса, первый регистр шкрокоманд и первый блок памяти микрокоманд, причем группа выходов первого блока модификации адреса соединена с группой адресных входов первого блока памя1ти микрокоманд, выход которого соединен с информационным входом первого реги-. стра микрокоманд, вход сброса которого соеданен с входом начальной установки первого блока модификации адреса и с входом начальной установки микропроцессора, вход синхронизации операционного блока соединен с входом синхронизации микропроцессора, информационный вход мкpoпpoцeccopa подключен к информационному входу операционного блока, адресный и информационный выходы которого являются соответственно адресным и информационным выходами микропроцессора, о т л ичающий ся тем, что, с целью повьшения производительности, он содержит второй блок модификации адреса, второй блок памяти микрокоманд, второй регистр микрокоматщ, блок проверки условий, первый и второй мультиплексоры, блок формирования вреиенных интервалов, содержащий три 1К-триггера и Элемент ИЛИ, блок коррекции фазы, содержащий два IK-триггера, два сумматора по модулю два и два элемента И, блок управления формированием следующего адреса, содержащий три дешифратора, восемь элементов И, два элемента ИЛИ-НЕ и три элемента ИЛИ, причем выход поля адреса первого (О регистра микрокоманд соединен с первыми информационными входами с jnepBoro и второго блоков модификации адреса, вторые информационные входы которых-соединены с выходом поля адреса второго регистра микрокоманд, выходы поля операции первого и второго регистров микрокоманд соединены соответственно с первым и вторым информационными входами первого мультиплексора, первая, вторая и третья группы выходов коЮ торого подключены соответственно к группе управляюпщх выходов микроПроцессора, к группе входов кода операции операционного блока и к группе управляющих входов блока проверки условий, группа информационных входов которого соединена с группой выходов признаков операционного блока, группа выходов второго блока модификации адреса соединена с группой адресных входов второго блока памяти микрокоманд, выход которо

Изобретение относится к вычислительной технике и может быть ис-польэовано для обработки данных в системах управления. Известен микропроцессор, содержа щий центральный блок обработки данных, блок микропрограммного управления, блок памяти и конвейерный регистр И. Недостатком этого микропроцессора конвейерного типа является низ кая производительность, обусловленная неоптимальным циклом ь«крокоманды, а также непроизводательной затратой времени при выполнении каж дого условного перехода. Наиболее близким к предлагаемому является микропроцессор, содержащий операционный блок, блок модификации адреса, регистр микрокоманд и блок памяти микрокоманд, причем гру па выходов блока модификации адреса соединена с группой адресных вхо дов блока памяти микрокоманд, выход которого соединен с информационным входом регастра микрокоманд, вход сброса которого соединен с входом начальной установки блока модификации адреса и с входом начальной установки микропроцессора, вход синхронизации операционного блока соединен с входом синхронизации микропроцессора, информационный вход мик ропроцессора подключен к информационному входу операционного блока, адресный и информационн1ый выходы которого являются соответственно ад ресным и информационным выходами NMKponponeccopa 2 , Недостатком данного 1«кропроцессора также является низкая производительность, ,обусловленная слеующими факторами. Цикл ьмкрокоманды в данном микропроцессоре выбирается из расчета максимальной длительности цикла работы либо операционного блока, либо управляющей части (генератор последовательности адресов, блок памяти микрокоманд): г-тах То„-,Т,рр где с - длительность цикла микрокоманды ; Тд„ - цикл работы операционного блока; Ти„р- цикл работы управляющей части микрокоманды. При построении 1« кропроцессора на злементной базе одной и той же технологии перечисленные компоненты имеют соизмериг4 1е значения быстродействия и . В результате этого цикл микрокоман;ф1 оказывается длиннее оптимального значения, равного Т . Кроме того, при конвейерном принципе выполнения микрокоманд выборка микрокоманды опережает на цикп.ее вьтолнения, в результате чего при выполнении условных переходов следующая после условного перехода микрокоманда выбирается раньше, чем формируется логическоеус-лоэие, определяющее направление перехода. Поэтому при каждом условном переходе в микропрограмме предусматривается холостая микрокоманда, выполняющая функцию задерж ки на один цикл. Таким образом, выполнение каждой микрокоманды условного перехода осуществляется за два цикла кмкрокоманды.

Целью изобретения является повышёние производительности ьикропроцессора.

Поставленная цель достигается там, что в микропроцессор, содержащий операционный блок, первый блок модификации адреса, первый регистр микрокоманд и первый блок памяти микрокомайд, причем группа выходов первого блока модификации адреса соединена с группой адресных вхо- дов первого блока памяти микрокоманд, выход которого соединен с информационным входом лервого регистра микрокоманд, вход сброса которого соединен с входом начальной установки первого блока модификации адреса и с входом начальной установки микропроцессора, вход синхронизации операционного блока соединен с входом синхронизации микропроцессора, информационный вход микропроцессора подключен к информационному входу операционного блока, адресный и информационный выходы которого являются соответственно адресным и информационным выходами ьмкропроцессора, введены второй блок модификации адреса, второй блок памяти микрокоманд, второй регистр микрокоманд, блок проверки условий, первый и второй мультиплексоры, блок формирования временных интервалов, содержащий три IK-rтриггера и элемент ИЛИ, блок коррекции фазы, содержащий два IKтриггера, два сумматора по модулю два и два элемента И, блок управления формированием гледующего адреса, содержащий три дешифратора, восемь элементов И, два элемента ЙЛИ-НЕ и три элемента ИЛИ, причем выход поля адреса первого регистра микрокоманд соединен с первыки информационными входами первого и второго блоков модификации адреса, вторые информационные входы которых соединены с выходом поля адреса второго регистра микрокоманд, выходы поля операции первого и второго регистров микрокоманд соединены соответственно с первым и

вторым информационными входами первого мультиплексора, первая, втораяИ третья группы выходов которого подключены соответственно к группе управляющих выходов NMKропроцессора, к группе входов кода операции операционного блока и к группе управляющих входов блока проверки условий, группа информационных входов которого соединена с

группой выходов признаков операционного блока, группа выходов второго блока модификации адреса соединена .группой адресных входов второго блока памяти гмкрокоманд, выход которого соединен с информационным входом второго регистра микрокоманд, вход сброса которого.-, соединен с входом начальной установки второго блока формирования адеса, с входом начальной устанрвки №1кропроцессора и с входами сброса первого и второго 1К-триггеров блока коррекции фазы, входы синхронизации которых соединены с первыми

ходами первого и второго элементов И блока коррекции фазы, .с входа1-и синхронизации первого, второго и третьего 1К-триггеров блока формирования временных интервалов и с

35 входом синхронизации микропроцессора, I- и К-входы первого и второго 1К-триггеров блока коррекции фазы подключены соответственно к шине единичного потенциала и к выходу

40 первого элемента И блока управления формированием следующего адреса, единичный и нулевой выходы первого 1К-триггера блока коррекции фазы подключены соответственно к пер45 вым входам первого и второго сумматоров по модулю два блока коррекции фазы, вторые входы которых соединены с единичным выходом второго 1К-триггер а блока коррекции

50 фазы, выход первого сумматора по модулю два блока коррекции фазы соединен с вторым входом первого элемента И Йлока коррекции фазы, выход которого соединен с входами сйнх55 ронизации второго регистра микрокоманд и второгоблока модификации . адреса, выход второго сумматора пс модулю два блока коррекции фазы соединен с управляюи ими-входами пер вого и второго мультиплексоров и с вторым входом второго элемента И блока коррекции фазы, выход которого соединен с входами синхро шзации первого регистра микрокоманд и первого блока модификации ад реса, первый, второй и третий управ ляюпие входы которого соединены соответственно с выходами первого элемента ИЛИ блока/управления форми рованием следующего адреса, второго элемента И блока управления формированием следующего адреса и первого элемента ШШ-НЕ блока управления формированием следующего адреса, пе вый, второй и третий управляющие входы второго блока модификации ад- реса соединены соответственно с выходами второго, третьего элементов ИЛИ блока управления формированием следующего адреса и второго элемента ИЛИ-НЕ блока управления формированием следующего адреса, первый ин формационный вход первой группы второго мультиплексора соединен с первым выходом признака перехода первого регистра микрокоманд, с инверсным входом третьего элемента И блока управления формированием сл дующего адреса, с первым входом чет вертого элемента И блока управления формированием следующего адреса и с первым инверсным входом пятого элемента И блока управления формиро ванием следующего адреса, вызсод которого соединен с первыми входами первого элемента ИЛИ блока управления формированием следующего адреса и первого элемента ИШ-НЕ блока упранпения формированием следующего адреса, второй вход которого соединен с вторым входом первого элемента ШШ блока управления фop яpoвaнием следующего адреса, с первым вх дом третьего элемента ИЛИ блока управления формированием следующего адреса и с первым выходом первого д шифратора блок управления формированием еледукицего-адреса, вход кото рого соединен с вторым входом признака перехода первого регистра мик рокоманд и с вторым информационным входом первой группы второго мультиплексора, первый информационный вход второй группы котсфого соедине с первым выходом признака перехода второго регистра микрокоманд, с первым входом шестого элемента И блока управления формированием следующего адреса и с инверсным входом второго элемента И блока управления формированием следующего адреса, первый вход которого соединен с прямым входом третьего элемента И блока управления формированием следующего адреса, с выходом седьмого элемента И блока управления фop яpoвaниeм следующего адреса и с 1-входом первого 1К-триггера блока фop мpoвaния временных интервалов, второй информационный вход второй группы второго мультиплексора соединен с вторым выходом признака перехода второго регистра микрокоманд и с входом второго дешифратора блока управления формированием следующего адреса, первый выход которого соединен с первыми входами второго элемента ИЛИ блока управления формированием следующего адреса и второго элемента ИЛИ-НЕ блока управления формированием следующего адреса, второй вход которого соединен с вторым выходом второго дешифратора блока.управления формированием следующего адреса, с вторым входом второго элемента ИЛИ блока управления формированием следующего адреса и с третьим входом первого элемента ИЛИ блока управлеmt формированием следующего адрет са, четвертый вход которого соединен с третьим входом первого элемента ИЛИ-НЕ блока управления формированием следующего адреса, с выходом четвертого элемента И блока управления формированием следующего адреса и с вторым входом третьего элемента ИЛИ блока управления формированием следующего адреса,, третий вход которого соединен с третьим входом второго элемента ИЛИ блока управления формированием следующего ад- . реса, с выходом-Шестого элемента И блока управления формированием следующего адреса, с третьим входом второго элемента ИЛИ-НЕ блока управления формированием следующего адреса и с прямым входом восьмого элемента И блока управления формированием следующего адреса, выход которого, соединен с пятым Е1ходом первого элемента ИЛИ блока управления формированием следующего адреса, шестой вход которого соединен с четвертым входом первого элемента ИЛИНЕ блока управления формированием следующего адреса и с вторым выходом первого дешифратора блока управления формированием следующего адреса, выход первого 1К-триггера блока формирования временных интервалов соединен с 1-входом второго 1К-триггера блока фop мpoвaния временных интервалов, с первым входом элемента ИЛИ блока формирования временных интервалов, со стробирующим входом третьего дешифратора блока управления формированием следукяцего адреса, с вторыми входами четвертого и шестого элементов И

блока управления формированием следующего адреса и с прямым входом пятого элемента И блока управления формированием следунмцего адреса, второй инверсный вход которого соединен с инверсным входом восьмого элемента И блока управления формированием следующего адреса, с k-входами первого и второго IK-триггеров блока формирования временных ин тервалов и с выходом второго IKтриггера блока формирования временных интервалов, 1-вход третьего 1К-триггера блока формирования временных интервалов соединен с первым выходом третьего дешифратора блока управления формированием следукяцего адреса, второй выход которого соединен с первыми входами первого и седьмого элементов И блока управления формированием следующего адреса, вторые входы которых соединены соответственно с первым выхо-. дом второго мультиплексора и выхо-, дом блока проверки условий , второй выход второго мультиплексора соединен с входом третьего деши11ратора блока управления формированием следующего адреса, выход третьего элемента И блока управления фориированием следующего адреса соединен с четвертым входом третьего элемента ИЛИ блока управления формированием следующего адреса, К-вхед и выход третьего iK-триггера блока формирования временных интервалов соединены с вторым входом элемента ИЛИ блока формирования временных интервалов, выход которого соединен с входом останова-операционного блока.

Кроме того, каждый из блоков модификадии адреса содержит регистр.

сумматор и три мультиплексора, причем группа выходов первого мультиплексора соединена с первой группой входов сумматора и является группой выходов блока, первый информащюнный вход первого мультиплексора соединен с выходом регистра, информационный вход которого соединен с выходом второго мульт типлексора, первый информационный вход которого соединен с выходом сумматора, вторые информационные входы первого и второго мультиплексоров соединены с выходом третьего мультиплексора, первый и второй информационные входы которого являются соответственно первым я вторым информационными входами блока, вход синхронизации регистра и вход сброса регистра являются соответственно входом синхронизации блока и входом начальной установки блока, управляющие входы первого, второго и третьего мультиплексоров являются соответственно первым, вторым и третьим управляющими входами блока, вход младшего разряда второй группы входов сумматора подключен к нмне единичного потенциала, остальные входы второй группы сумматора подключены к шине нулевого потенциала.

При этом блок проверки условий содержит мультиплексор и сумматор по модулю два, причем группа информационных входов мультиплексора явлется труппой информационных входов блока, выход мультиплексора соедине с первым входом сумматора по модулю два, выход которого является выходом блока, управлякмцие входы мультиплексора и второй вход сумматора по модулю два являются управляющими входаьфс группы блока.

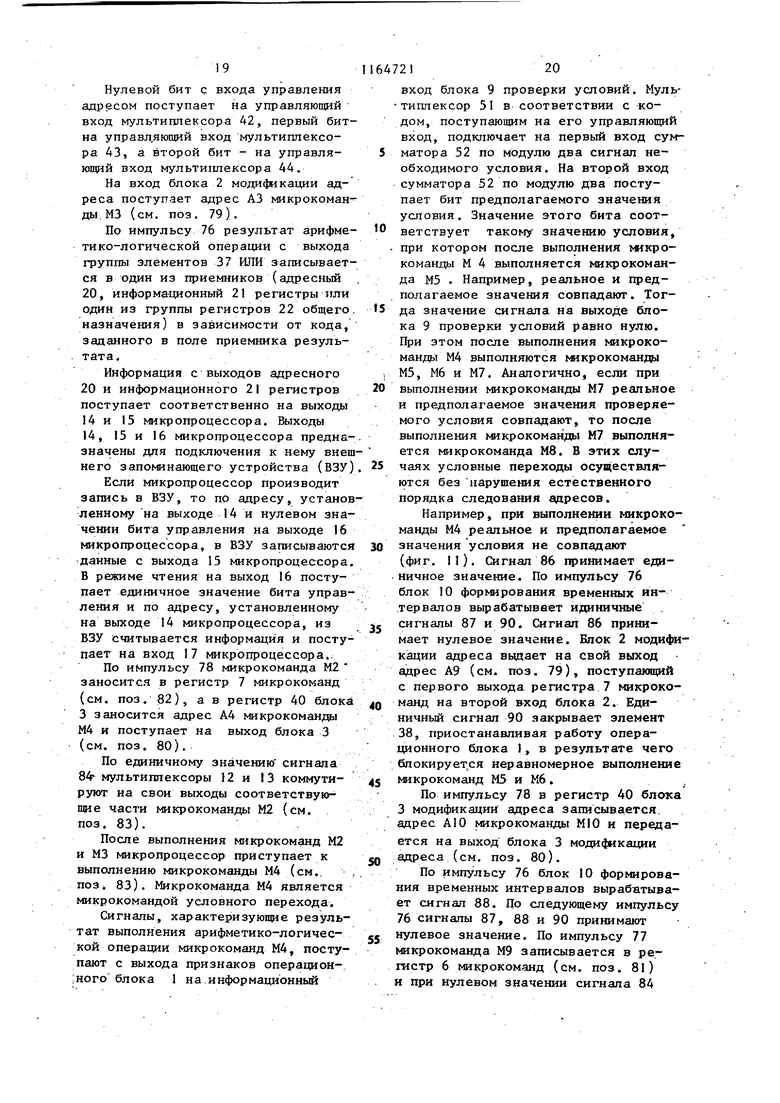

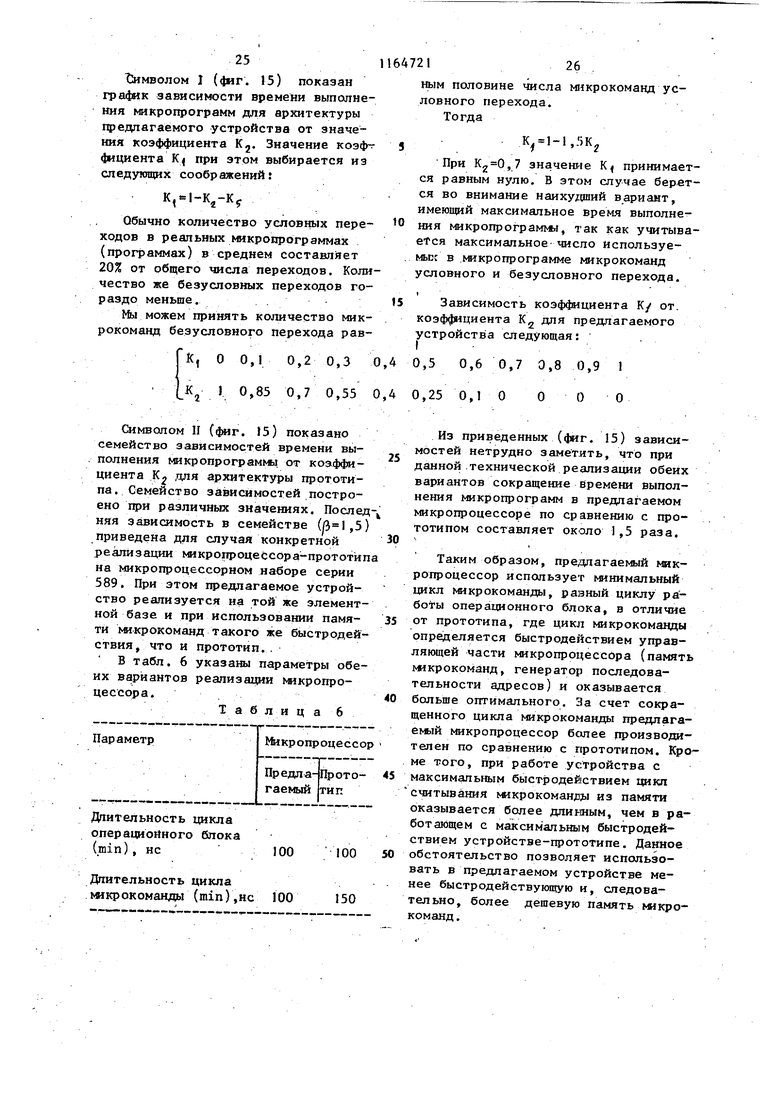

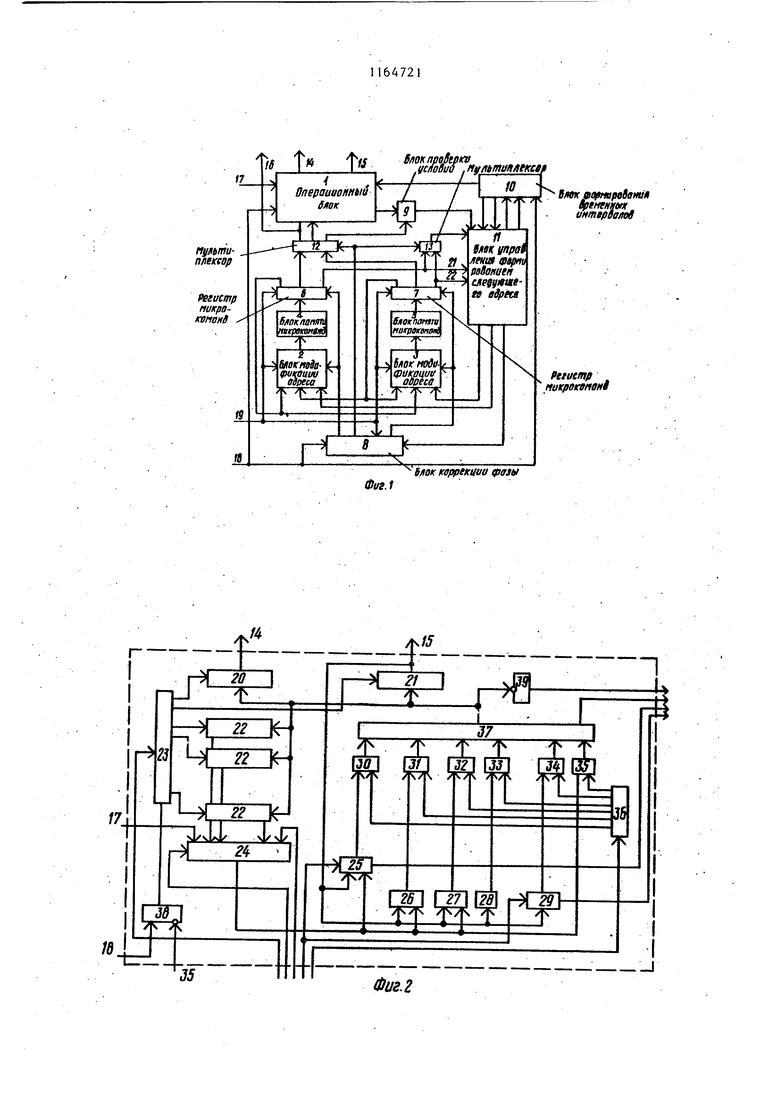

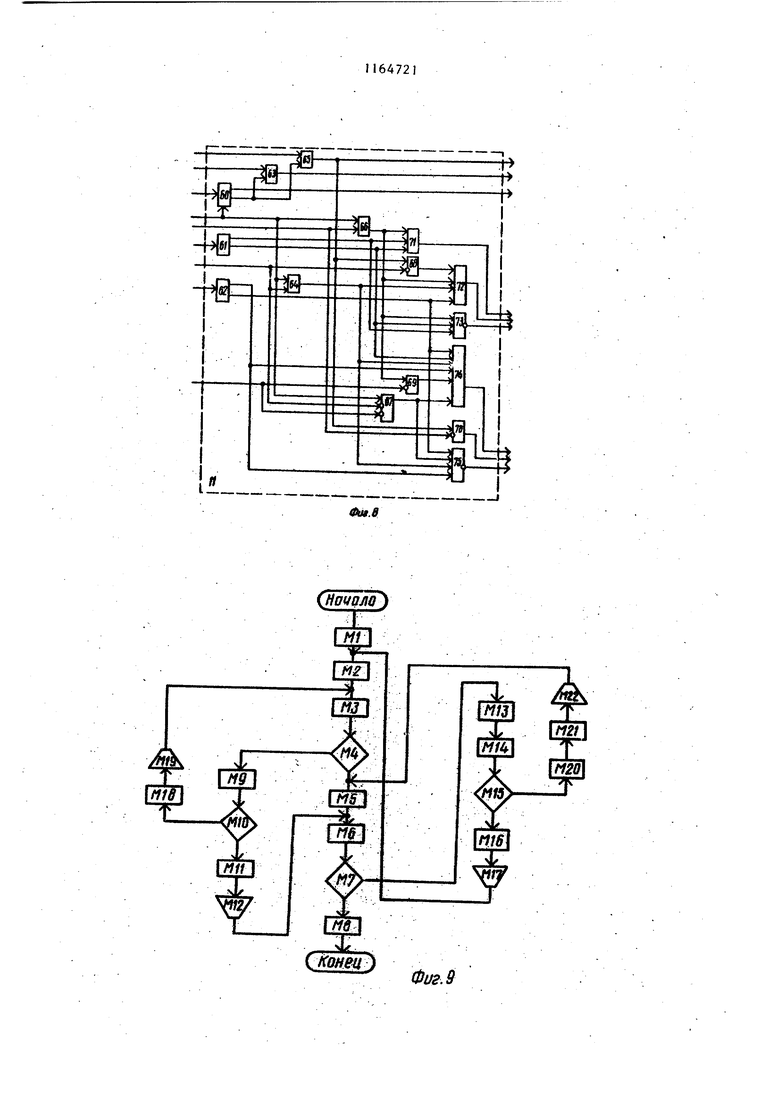

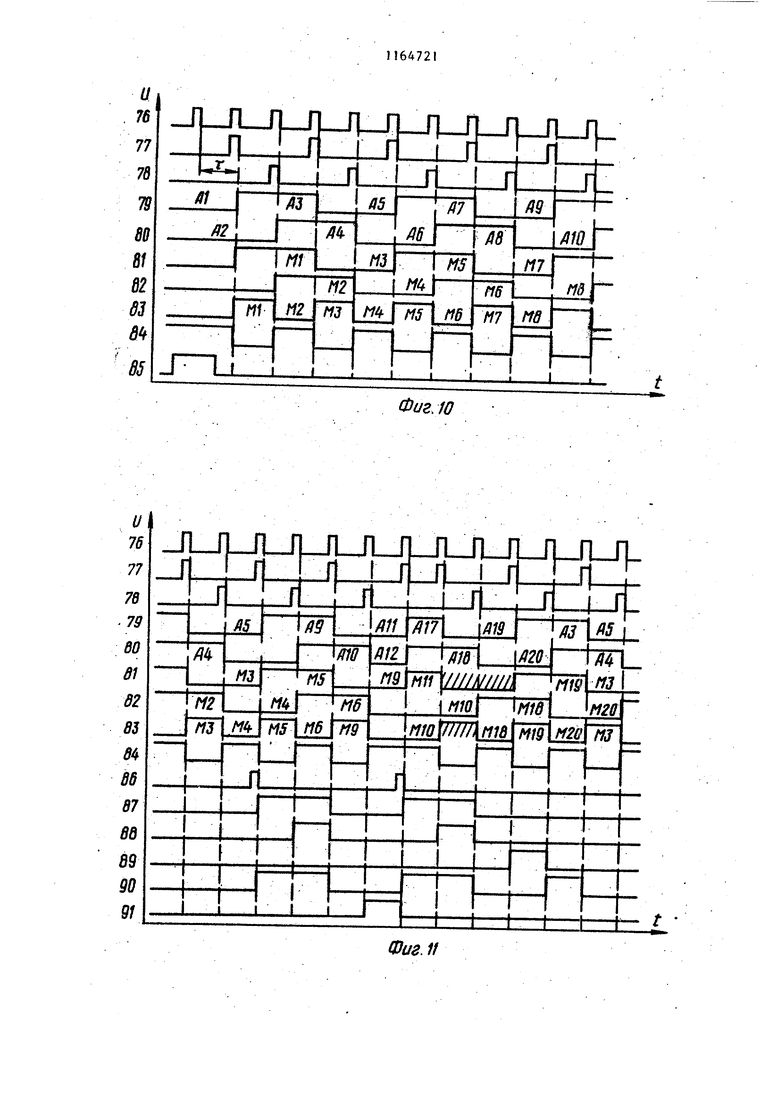

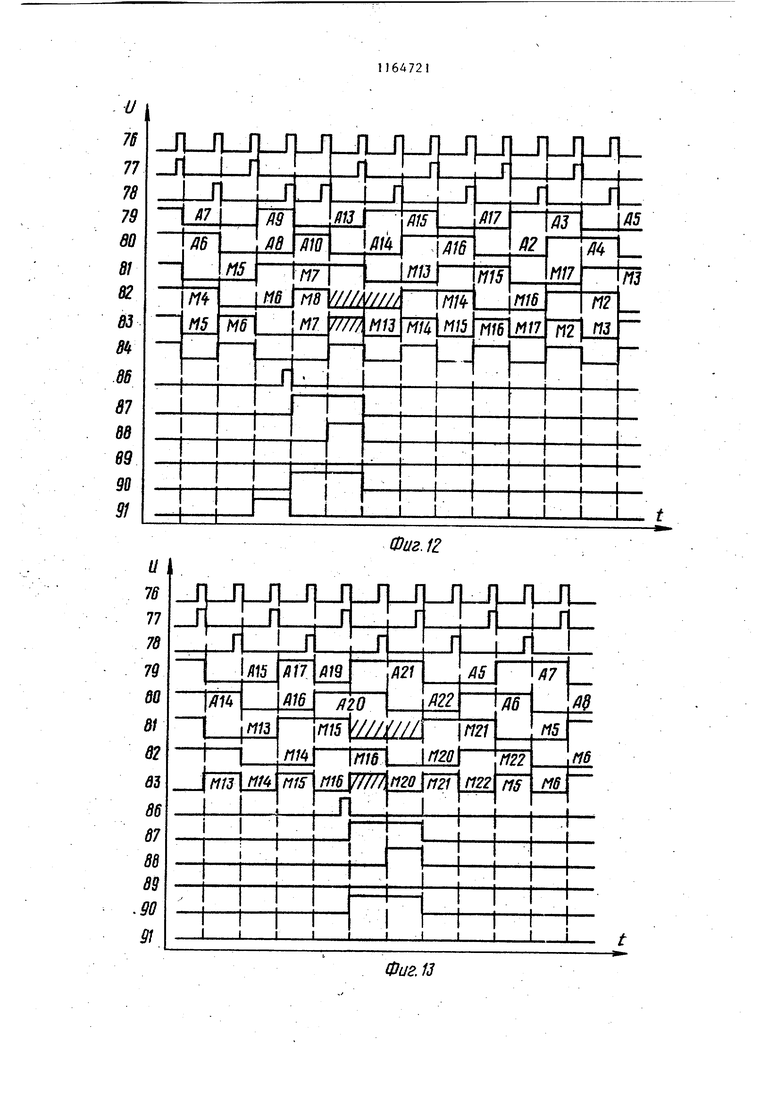

На фиг. 1 иэображена схема предлагаемого микропроцессора; на фиг.2схема операционного блока, на фиг.Зсхема блока модификации адреса{ на фиг. А - схема блока коррекцииj на фиг. 5 - схема блока проверки условий, на фиг. 6 - схема блока формирования временных интервалов; на фнг. 7 - схема мультиплексора; на фиг. 8 - схема блока управления формяроватгем следующего адреса , на фиг. 9 - блок-схема алгоритма функционирования микропроцессора; на фяг. 10-14 - временные диаграммы

работы микропроцессора на фиг. 15графики зависимостей времени выполнения микрфпрогранм в предлагаемом и известном устройствах.

Микропроцессор содержит опереди онный блок 1, блоки 2 и 3 модификации адресов, блоки 4 и 5 памяти микрокоманд, регистры 6 и 7 микрокоманд, блок 8 коррекции фазы, бло 9 проверки условий, блок 10 формирования временных интервалов , блок 11 управления формированием следующего адреса, мультиплексоры 12 и 13, адресный выход 14, информационный выход 15, упр,авляю1дий выход 16, информационный вход 17, вход 18 синхронизации и вход 19 начальной установки.

Операционный блок 1 (фиг. 2) содержит адресный 20 и информационный 21 регистры, группу регистров общего назн ачения, дешифратор 23 приемника результата, мультиплексор 24 операндов, сумматор 25, группы операционных элементов 26 И 27 ИЛИ, 28 НЕ, сдвигатель 29, группы коммутирующих элементов 30-35 И, дешифратор 36 операций, группу элементов 37 ИЛИ, элементы 38 и 39 И.

. Каждый из блоков 2.и 3 модификации адреса (фиг. 3) содержит регистр 40, счетчик 41, первый 42, второй 43 и третий 44 мультиплексоры.

Блок 8 коррекции фазы (фиг. 4) содержит первый 45 и второй 46 IKтриггеры, первый 47 и второй 48 сумматоры по модулю два и приемный 49 и второй 50 элементы И.

Блок 9 проверки условий (фиг.5) содержит мультиплексор 51 и суМматор 52 по модулю два.

Блок 10 формирования временных интервалов (фиг. 6) содержит три

5, 54 и 55 IK-триггера и элемент

56 ИЛИ.

Мультиплексор 12 и 13 (фиг. 7) содержат первый 57 и второй 58 блоки элементов И и блок 59 элемен тов или.

Влок 11 управления формированием следующего адреса (4иг. 8) содержит третий 60, второй 61 и первый 62 дешифраторы, первый 63, чет вертый 64, седьмой.65,шестой 66, пятый 67, третий 68, восьмой 69 и второй 70 элементы И, второй 71

и третий 72 элементы ИЛИ, второй элемент ИЛИ-НЕ 73, первый элемент ИЛИ 74 и первый элемент ИЛИ-НЕ 75,

Символами Mi (,2,...,n) обозначены микрокоманды ((}мг. 9).

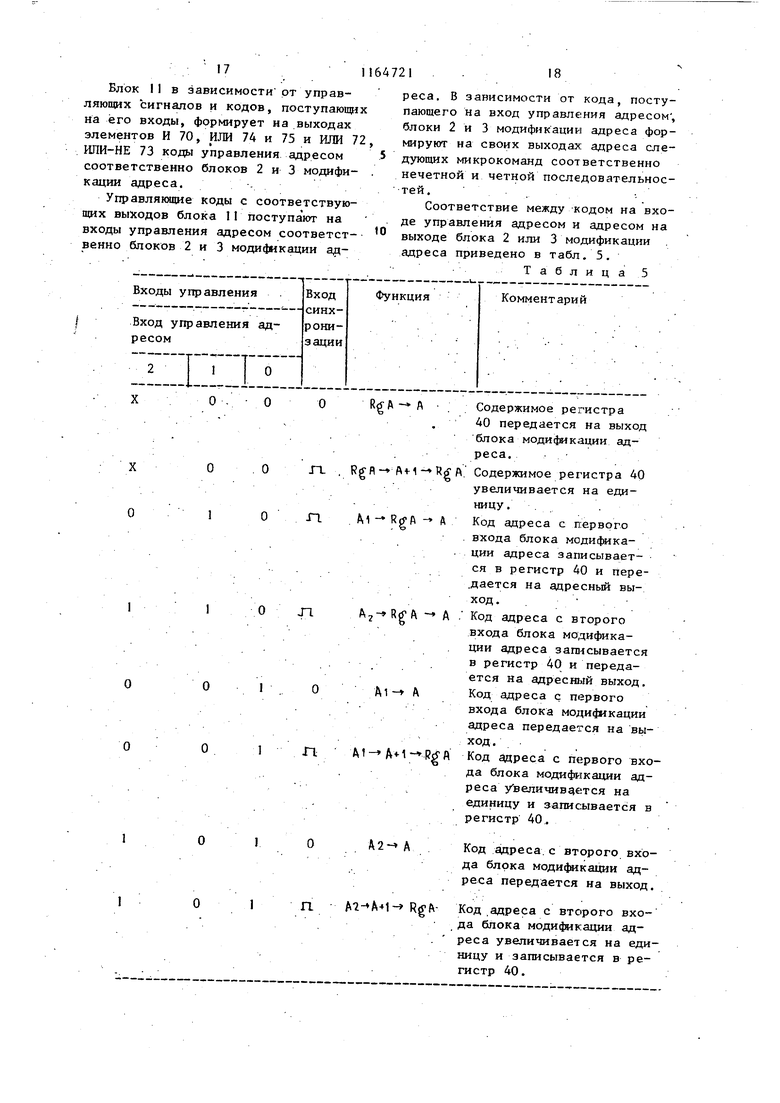

На временных диаграммах работы устройства (4мг. 10-J4) представлены импульсы 76 на входе 18 синхронизации микропроцессора, импульсы 77 на выходе элемента И 50, импульсы 78 на выходе элемента И 49, сигнал 79 адреса на выходе блока 2 модификации адреса, сигнал 80 адреса на выходе блока 3 модификации адреса, сигнал 81 кода микрокоманды на выходе регистра 6 микрокоманд, сигнал 82 кода микрокоманды на входах регистра 7 микрокоманд, сигнал 83 кода микрокоманды на выходах мультиплексоров 12 и 13, сигнал 84 на выходе сумматора 48 по модулю два, сигнал 85 на входе 19 начальной установки микропроцессора, сигнал 86 на выходе элемента И 65, сигнал 87 на выходе 1К-трИггера 53, сигнал 88 на выходе IKтриггера 55, сигнал 89 на первом выходедешифратора 60, сигнал 90 на выходе элемента ИЛИ 56, сигнал 91 на выходе элемента И 63, с - цикл микрокоманды.

Рассмотрим работу устройства на примере выполнения им микропрограмм. (фиг. 9)

Нечетные микрокоманды (M,Mj, М,...) содержатся в блоке 4 памяти микрокоманд и составляют нечетную последовательность микрокоманд, а четные (М ,М(,М, . .. ) в блоке 5 памяти микрокоманд и составляют четную последовательность микрокоманд..

В процессе работы микропроцессора возможны следующие особенности выполнения микpoпpoгpa f ы:

выполнение линейного участка мик

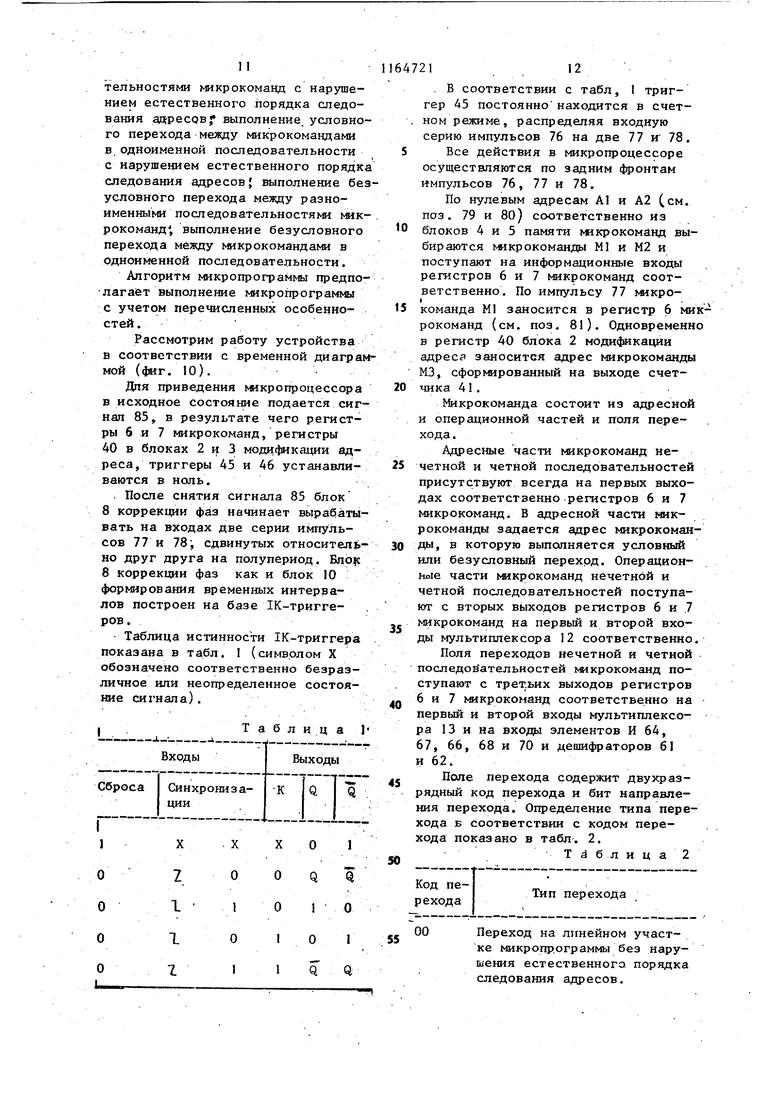

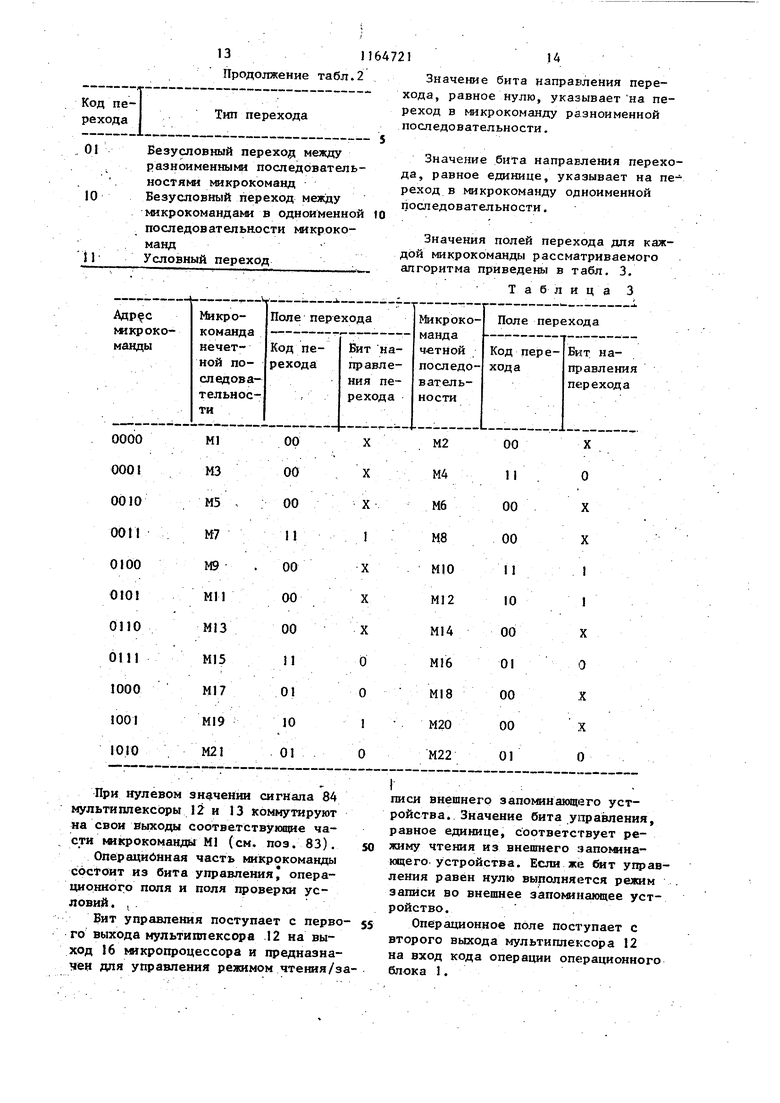

ропрограммы (в этом случае производится поочередное выполнение микрокоманд из нечетной и четной последовательностей без нарушения естественного порядка следования адресов - адрес каждой следукнцей микрокоманды на единицу больше адреса предьщущейу; выполнение усовного перехода без нарушения естественного порядка следования адресов выполнение условного перехода между разноименными последовательностями микрокоманд с нарушением естественного порядка следования адресовf выполнение, условно го перехода между микрокомандами в.одноименной последовательности с нарушением естественного порядк следования адресов J выполнение бе условного перехода между разноименными поел едовательностяьи мик рокоманд, вьшолнение безусловного перехода между микрокомандами в одноименной последовательности. Алгоритм микропрограммы предпо лагает выполнение микропрограммы с учетом перечисленных особенностей. Рассмотрим работу устройства в соответствии с временной диагра мой (4мг. 10). Для приведения микропроцессора в исходное состояние подается сиг нал 85 в результате чего регистры б и 7 микрокоманд, регистры 40 в блоках 2 и 3 моди(|икации адреса, триггеры 45 и 46 устанавливаются в ноль. . После снятия сигнала 85 блок 8 коррекции фаз начинает вырабаты вать на входах две серии импульсов 77 и 78; сдвинутых относитель но друг друга на полупериод. Бло|с 8 коррекции фаз как и блок 10 формирования временных интервалов построен на базе 1К-триггеров. Таблица истинности 1К-триггера показана в табл. 1 (символом X обозначено соответственно безразличное или неопределенное состояние сигнала) . Таблица 10 I 1 Q Q -Г 21,12 . В соответствии с табл, 1 триггер 45 постоянно находится в счетном режиме, распределяя входную серию импульсов 76 на две 77 и- 78. Все действия в микропроцессоре осуществляются по задним фронтам импульсов 76, 77 и 78. По нулевым адресам А1 и А2 (см. поз. 79 и 80) соответственно из блоков 4 и 5 памяти микрокоманд выбираются ьмкрокоманды Ml и М2 и поступают на информационные входы регистров 6 и 7 микрокоманд соответственно. По импульсу 77 NMKPOкоманда Ml заносится в регистр 6 микрокоманд (см. поз. 81). Одновременно в регистр 40 блока 2 модификации адреса заносится адрес микрокоманды МЗ, сформированный на выходе счетчика 41 . Микрокоманда состоит из адресной и операционной частей и поля перехода. Адресные части микрокоманд нечетной и четной последовательностей присутствуют всегда на первых выходах соответственно регистров 6 и 7 микрокоманд. В адресной части микрокоманды задается адрес микрокоманды, в которую выполняется условный или безусловный переход. Операционhoie части ьикрокоманд нечетной и четной последовательностей поступают с вторых выходов регистров 6 и .7 микрокоманд на первый и второй входы мультиплексора 12 соответственно. Поля переходов нечетной и четной последовательностей ьмкрокоманд поступают с трет.ьих выходов регистров 6 и 7 юткрокоманд соответственно на первый и второй входы мультиплексора 13 и на входы элементов И 64, 67, 66, 68 и 70 и дешифраторов 61 и 62. Поле перехода содержит двухразрядный код перехода и бит направления перехода. Определение типа перехода Б соответствии с кодом перехода показано в табл. 2. Т блица2 Код пе- Тип перехода рехода 00 Переход на линейном участке микропрограммы без нарушения естественного порядка следования адресов. 13 Продолжение табл Код пеТип перехода рехода 01 Безусловный переход между разноименными последовател ностями микрокоманд 10 Безусловный переход между микрокомандами в одноименн последовательности микроко манд П Условный переход При нулевом значении сигнала 84 мультиплексоры 12 и 13 коммутируют на свои вьпсоды соответствующие части микрокоманды Ml (см. поз. 83). Олёрацибниая часть микрокоманды состоит из бита управления, операционного поля и поля проверю условий . . БИТ управления поступает с перво го выхода мультиплексора 12 на выход 16 микропроцессора и предназначен дпя управления режимом чтения/з 1 Значение бита напранщения перехода, равное нулю, указываетна переход в микрокоманду разноименной последовательности. Значение бита направления перехода, равное единице, указывает на переход в микрокоманду одноименной последовательности. Значения полей перехода для каждой микрокоманды рассматриваемого алгоритма приведены в табл. 3. Таблица 3 писи внешнего запоминающего устройства. Значение бита управления, равное единице, соответствует peжиму чтения из внешнего запоьмнаю«цего устройства. Если же бит управления равен нулю выполняется режим записи во внешнее запоминающее устройство. Операционное поле поступает с второго выхода мультиплексора 12 на вход кода операции операционного блока 1. Операционное поле состоит из по ЛЯ прием 1ика результата, поля операндов, поля к.онстант, бита входного признака и поля операций. Поле приемника результата поступает на управляющий вход дешифра-тора 23, В этом поле указывается номер регистра (адресного 20, инфор мационного 21 или одного из группы регистров 22 общего назначения),в кот рый записывается результат выполняе арифметико-логической операции. ПоЛе операндов поступает на упра ляющий вход мультиштексора 2-4. В этом поле указывается номер источника второго операнда для выполнения арифметико-логической операции.. По этому номеру мультиплексор 24 передает на свой выход или информационный код с входа 18 микропроцессора, или содержимое одного из группы регистров 22 общего назначения, или содержимоеполя констант. Поле констант поступает на второй вход мультиплексора 24. Бит входного, признака поступает .одновременно на вход переноса сумма тора 25 и на вход сдвига сдвигателя 29. Битом входного признака дается входной перенос или .входной сдвиг при выполнении операций сложения или сдвига. Поле операций поступает на управляюп1ий вход дешифратора 36. В этом поле задается код арифметико. логической операции. По этому коду дешифратор 36 отрывает одну из групп элементов 30-35 И, вследствие чего результат соответствующей операции с выхода сумматора 25,или с выходов групп элементов 26 И, 27 ИЛ 28НЕ, или с выходов сдвигателя 29и мультиплексора 24 поступает на информационные входы адресного 20, информационного 21 регистров игруппы регистров 22 общего назначения. Набор выполняеьых операций в соответствии с кодом, задаваемым в по ле операций, представлен в табл. 4. Таблица 4 Код опеВыполняемая операция рации уложение содержимого информационного регистра 2 (первого операнда) с вто рым операндом, поступающ с выхода мультигшексора 16 . Продложение табл.4 --: -. Код опеВыполняемаЯ операция рации Конъюнкция первого и второго операндов. Дизъюнкция, первого и второго операндов. Инверсия первого операнда. 100 Сдвиг вправо на один разряд первого операнда. Прямая пересылка второго операнда. . Если результат операции равен нулю, на выходе элемента 39 И вырабатывается единичный сигнал. Сигнал с выхода элемента 39.И, .также как н сигналы с выхода старшего разряда группы элементов 37 ШШ (знак результата), и с выходов переноса сумматора 25, сдвига сдвигателя 29 поступают на вход признаков операционного блока 1. I - . .. . - : Сигналы с выхода признаков операционного блока 1 поступают на информационный вход блока 9 проверки ус- . ловий, на управляющий вход которого поступает поле проверки- условий операционной части микрокоманды с третьего выхода мультиплексора 12. В поле проверки условий содержится номер проверяемого условия и бит, указывающий на предполагаемое значение проверяемого условия. Номер проверяемого условия поступает на управляющий вход мультиплексора 51, в результате чего последний подключает на первый вход сумматора 52 по моду-, лю два сигнал соответствующего условия. На второй вход сумматора 52 по модулю два поступает бит,указываю1ций на предполагаемое значение проверяемого условия. Если реальное и предполагаемое значения условия совпадают , на выходе блока 9 проверки условий присутствует нулевой сигнал, в случае несовпадения - единичный. Сигнал с выхода блока 9 проверки условий поступает на вход элемента И 65 блока I1..

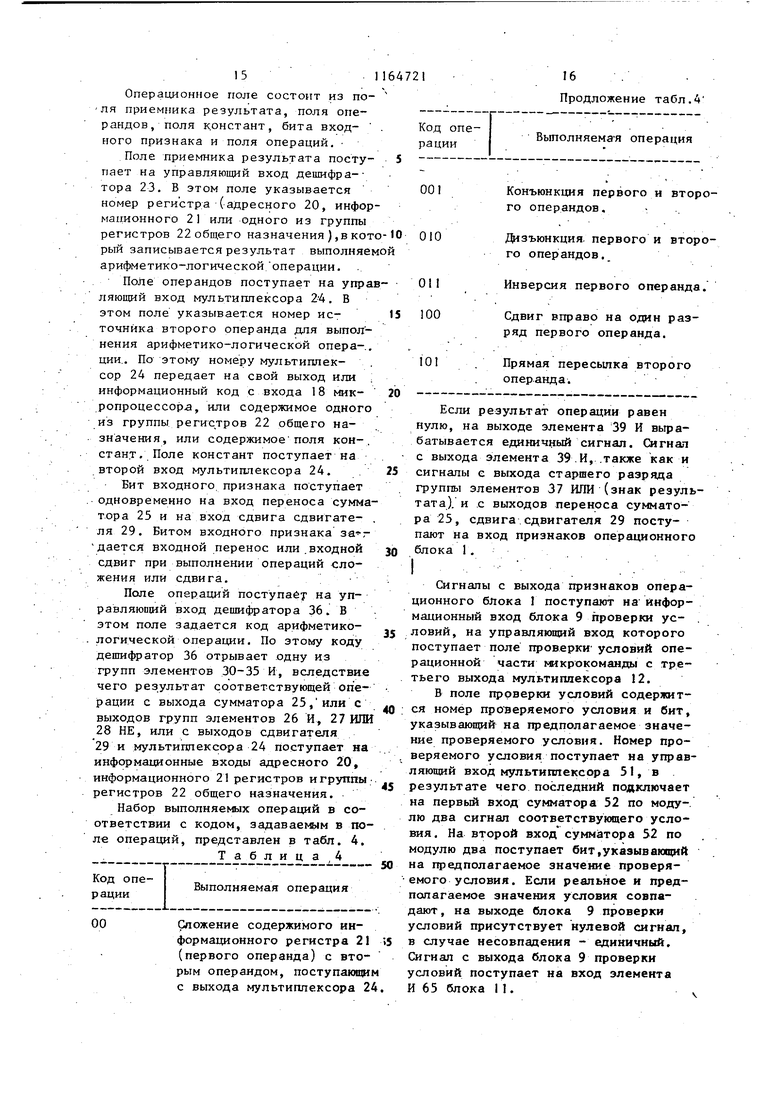

Блок II в зависимости от управляющих сигналов и кодов, поступающих на его входы, формирует на выходах элементов И 70, ИЛИ 74 и 75 и ИЛИ 72 ИПИ-НЕ 73 коды управления адресом соответственно блоков 2 и 3 модификации адреса.

Управляющие коды с соответствующих выходов блока 11 поступают на входы управления адресом соответственно блоков 2 и 3 модификации адОRcrA А Содержимое регистра

40 передается на выход

.0-П. . Rgfl- Rg А. Содержимое регистра 40

ОГТ . AI - RgA - А Код адреса с первого

О J1.А R ft А . Код адреса с второго 1 . ОAI- АКод адреса с первого .ход.

1XI At- Ai-1- PgА Код адреса с первого вхоJОА2- АКод адреса, с второго вхоП Rgftреса, В зависимости от кода, поступающего на вход управления адресом , блоки 2 и 3 модификации адреса формируют на своих выходам: адреса следующих микрокоманд соответственно нечетной и четной последовательностей. .

Соответствие между -кодом на входе управления адресом и адресом на выходе блока 2 или 3 модификации адреса приведено в табл. 5.

Таблица 5

блока модификации адреса.

увеличивается на единицу. .

. входа блока модифика. ции адреса записывается в регистр 40 и перелается на адресньй выход. .

входа блока модификации адреса записывается .в регистр 40 и передается на адресный выход.

входа блока модификации

адреса передается на выда блока модификации адреса увеличивается на единицу и записывается в регистр 40..

да блока моди кации адреса передается на выход.

Код адреса с второго входа блока моди(}икации адреса увеличивается на единицу и записывается в регистр 40. Нулевой бит с входа управления адресом поступает на управляющий вход мультиплексора 42, первый бит на управл.яющий вход мультиплексора 43, а второй бит - на управляющий вход мультиплексора 44. На вход блока 2 модификации адреса поступает адрес A3 микрокоман ды. МЗ (см. поз. 79)., По импульсу 76 результат арифме тико-логической операции с выхода группы элементов 37 ИЛИ записывает ся в один из приемников (адресный 20, информационный 21 регистры или один из группы регистров 22 общего назначения) в зависимости от кода, заданного в поле приемника результата. Информация с выходов адресного 20 и информационного 2I регистров поступает соответственно на выходы 14 и 15 микропроцессора. Выходы 14, 15 и 16 микропроцессора предназначены для подключения к Нему внеш него запоминающего устройства (ВЗУ Если микропроцессор производит запись в ВЗУ, то по адресу, установ ленному на выходе 14 и нулевом значении бита управления на выходе 16 микропроцессора, в БЗУ записываются данные с выхода 15 ьшкропроцессора В режиме чтения на выход 16 поступает единичное значение бита управления и по адресу, установленному на выходе 14 микропроцессора, из ВЗУ считывается информация и поступает на вход 17 микропроцессора,. По импульсу 78 микрокоманда М2 заносится в регистр 7 микрокоманд (см. поз. 82), а в регистр 40 блока 3 заносится адрес А4 микрокоманда М4 и поступает на выход блока 3 (см. поз. 80). По единичному значению сигнала 84 мультиплексоры 12 и 13 коммутируют на свои выходы соответствун щие части микрокоманды М2 (см. поз. 83). После выполнения микрокоманд М2 и МЗ микропроцессор приступает к выполнению микрокоманды М4 (см.. no3i. 83). №1крокоманда М4 является микрокомандой условного перехода. Сигналы, характеризующие результат выполнения арифметико-логической операции микрокоманд М4, поступают с выхода признаков операцион- ;ного блока 1 на информационный 2120 вход блока 9 проверки условий. Мультиплексор 51 в соответствии с кодом, поступающим на его управляющий вход, подключает на первый вход сумматора 52 по модулю два сигнал необходимого условия. На второй вход сумматора 52 по модулю два поступает бит предполагаемого значения условия. Значение этого бита соответствует такому значению условия, при котором после выполнения 1 «крокоманды М 4 выполняется микрокоманда М5 . Например, реальное и предполагаемое значения совпадают. Torда значение сигнала на выходе блока 9 проверки условий равно нулю. При этом после выполнения микрокоманда М4 выполняются якpoкoмaнды М5, Мб и М7. Аналогично, если при выполнении 1 икрокоманды М7 реальное и предполагаемое значения проверяемого условия совпадают, то после выполнения микрокоманды М7 выполняется микрокоманда Мб. В этих случаях условные переходы осуществляются без нарушения естественного порядка следования адресов. Например, при выполнении микрокоманды М4 реальное и предполагаемое значения условия не совпадают (фиг. П). Сигнал 86 щ инимает единичное значение. По импульсу 76 блок 10 фop a poвaния временных интервалов вырабатывает идиничные сигналы 87 и 90. Сигнал 86 принимает нулевое значение. Блок 2 модификации адреса вьщает на свой выход адрес А9 (см. поз. 79), поступаииций с первого выхода регистра 7 микрокоманд на второй блока 2. Единичный сигнал 90 закрывает злемент 38, приостанавливая работу операционного блока 1, в результате чего блокирует ся неравномерное выполнение микрокоманд М5 и Мб. По импульсу 78 в регистр 40 блока 3 модификации адреса записывается, адрес AIO микрокоманды MlО и передается на выход блока 3 модификации адреса (см. поз. 80). По импу-льсу 76 блок 10 формирования временных интервалов вырабнтывает сигнал 88. По следующему импульсу 76 сигналы 87, 88 и 90 принимают нулевое значение. По импульсу 77 микрокоманда М9 записывается в регастр 6 микрокоманд (см. поз. 81) при нулевом значении сигнала 84 21 записывается на выходы мультиплексоров 12 и 13 для выполнения (см. поз. 83). В рассмотренном случае показан пример выполнения условного перехо да из четной последовательности (микрокоманда М4) в нечетную (микрокоманда М9) с нарушением естественного порядка следования адресов После выполнения микрокоманды М9 поступает на выполнение микрокоманда MIO (см. поз. 83). Шкрокоманда М10 также является ЮТкрокомандой условного перехода. Если при выполнении микрокоманды MlО реальное и предполагаемое значение проверяемого условия совпадают, то естественный порядок выполнения микропрограммы не нарушается и после микрокоманды MlО выполняется микрокоманда ММ (см. поз. 83 на фиг; 14). Если же совпадения нет .вырабатывается сигнал 86 (см. фиг. I1). Так как условный переход в случае несовпадения реального и предполагаемого значения осуществляется между микрокомандами в одн именной последовательности (из микрокоманды MlО в микрокоманду Ml8), то сигнал 91 в процессе выполнения микрокоманды М10 имеет единичное значение. При единичном значении сигнала 9Л по импульсу 76 триггер 46 изменяет свое сос.тояние на противоположное, в резул .тате чего блок 8 изменяет фазу выдачи импульсов 77 и 78 на протйвопрложные. Блок 3 модификации адрес передает на свой выход адрес А18, поступающий на первьй вход блока 3 модификации -адреса с первого выход регистра 7 микрокоманд. По сигналу 90 операционный блок 1 приостанавливает свою работу, предупреждая неправомерное исполнение микрокоманд. Заштрихованные участки на временных 1 диаграммах (см. поз. 81 82 и 83) указыв.ают на неопределенное значение кода в рассматриваемы :момент времени. После выполнения микрокоманды MIO выполняется микрокоманда Ml8, после чего поступает к выполнению шкрокоманда Ml9. }4 крокоманда Ml 9 является микрокомандой обусловленн го перехода. В данном случае безусловный переход осуществляется между микрокомандами -в одноимен21ной последовательности (-из микрокоманды М19 в микрокоманду ИЗ). Сигнал 89 имеет единичное значение. Блок 2 модификации адреса передает на свой выход адрес A3 (см. поз. 79). При е,циничном значении сигнала 89 по импульсу 76 устанавливается в единицу триггер 54, в результате чего сигнал 90 принимает единичное значение. Приостанавливается на один такт работа операционного блока 1, вследствие чего предупреждается выполнение кмкрокоманды М20. После выполнения микрокоманды М19 выполняется микрокоманда МЗ. На временной дааграмме (фиг. 12) после выполнения микрокоманд М5 и Мб показан условный переход из мкрокоманды М7 в гдакрокоманду М13 для случая неравенства реального и предполагаемого значений Прове-f ряемого условия. В дгшном случае условнь1й переход осуществляется между микрокомандами в одноименной последовательности и его выполнение производится аналоги 1но выполнению условного перехода из микрокоманды М10 в микрокоманду MI8 (фиг. П). Выполнение условного перехода из микрокоманды Ml5 показано для , случая равенства реального и предполагаемого значений условия. После выполнения микрокоманды Ml 5 выпол-- няется микрокоманда М16. На данном участке алгоритма микропрограммы осуществляется безусловный переход между разноименными последовательностями (из микрокоманды Ml 7 в микрокоманду М2). В этом случае код перехода в микрокомандах М16 и MI7 равен 01 (табл. 2). Блоки 3 и 2 модификации адреса передают на свои выходы соответст- венно адреса А2 и A3 (см. поз. 80 и 79). После выполнения микрокоманд Ml6 и Ml 7 выполняются микрокоманды М2 и МЗ. На временной диаграмме (фиг. 13) показано выполнение ус:шовного перехода из микрокоманды Ml6 в микрокоманду М20 (в одноименной последовательности) и безусловного перехода между разноименными последовательностями (из 1«1крокоманды М22 в мик-. рокоманду М5). Выполнение их производится так же, .как и выполнение аналогичных переходов (фиг. 12).

Выполнение безусловного перехода между микрокомандами в одноименной последовательности (из микрокоманды Ml2 в микрокоманду Мб) осуществляется аналогично переходу из микрокоманды Ml9 в микрокоманду МЗ (фкг. 14. и 13).

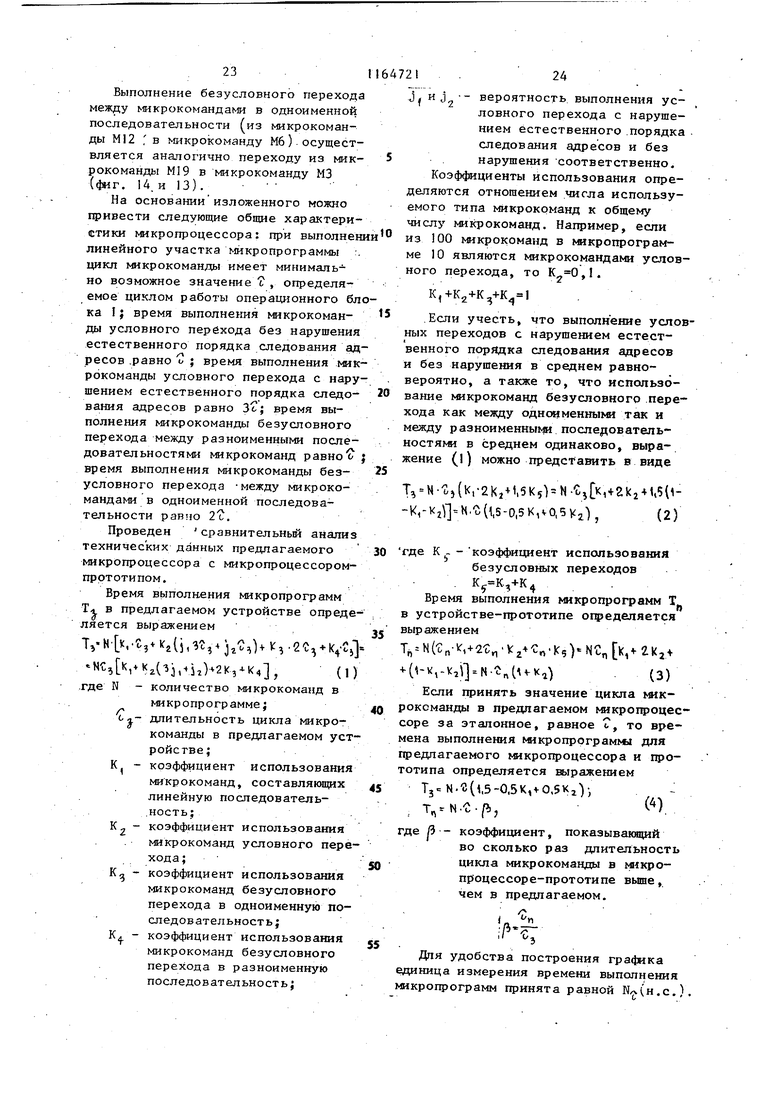

На основании изложенного можно привести следующие общие характеристики микропроцессора: при выполнени линейного участка микропрограммы цикл микрокоманды имеет минимально возможное значение, определяемое циклом работы операционного блока I; время выполнения микрокоманды условного перехода без нарушения естественного порядка следования адресов .равно С ; время выполнения микрокоманды условного перехода с нарушением естественного порядка следовакия адресов равно время выполнения микрокоманды безусловного перехода между разноименными последовательностями микрокоманд равно tвремя выполнения микрокоманды без- условного перехода -между микрокомандами в одноименной последовательности равло 2о.

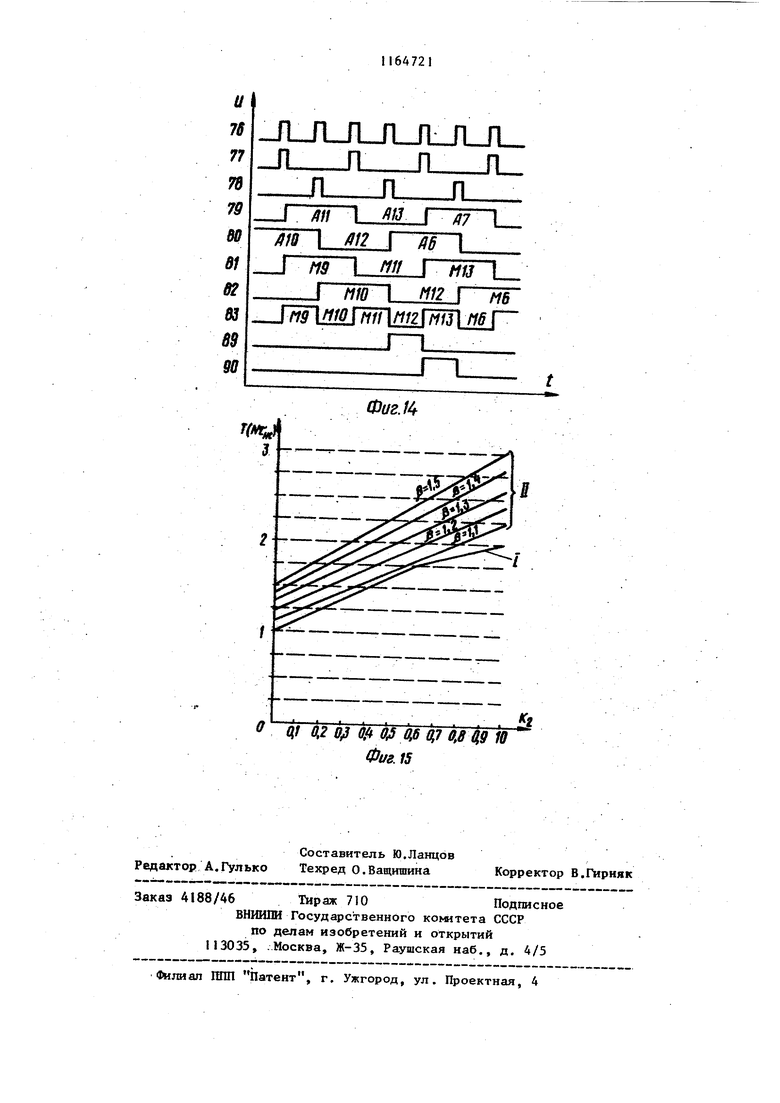

Проведен сравнительный анализ технических данных предлагаемого микропроцессора с микропроцессоромпрототипом.

Время выполнения микропрограмм Чл в предлагаемом устройстве определяется выражением

VH{K,.C,.lc,,(5,,, +

-N,K,K.,(3j,4b)2K,, (1) .где N - количество микрокоманд в

микропрограмме;

Сл- длительность цикла микрокоманды в предлагаемом устройстве;

К - козффициент использования

микрокоманд, составляющих линейную последователь.ность;

Ку - коэффициент использования

микрокоманд условного перехода ;

K,j - коэффициент использования микрокоманд безусловного перехода в одноименную последовательность;

Кх - коэффициент использования микрокоманд безусловного перехода в разноименную последовательность;

J, иj - вероятность выполнения условного перехода с нарушением естественного .порядка следования адресов и без нарушения соответственно. Коэффициенты использования определяются отношением .числа используемого типа микрокоманд к общему числу микрокоманд. Например, если из 100 ьмкрокоманд в NMKponporpaMме 10 являются ьоткрокомандами условного перехода, то К 0,1.

К,+К2+К,

Если учесть, что выполнение условных переходов с нарушением естественного порядка следования адресов и без нарушения в среднем равновероятно, а также то, что использование ьмкрокоманд безусловного перехода как между одноименными так и между разноименныьм последовательностями в среднем одинаково, выражение (|) можно представить в виде

I iijtсу.4. I сяоп л V хл . fsrtfj

T, H-i:)(K,.5K5) + 2k2 + ,5(l-KrXz l (1.5-0,5 К,vO,)(2)

где К - - коэффициент использования безусловных переходов

. .,.

Время выполнения микропрограмм Т в устройстве-прототипе оцределяется выражением T.N(,.K5)NCjk,f гКг

(-«, М-п(а)(3)

Если принять значение цикла ьмкрокоманды в предлагаемом NMKponpouecто вресоре за эталонное, равное

мена выполнения микропрограммы для предлагаемого микропроцессора и прототипа определяется выражением (,5-0,5K,0.5Ki)-,

()

, T,N.-C./,J

где /3 - коэффициент, показывакидий

во сколько раз длительность цикла микрокоманды в шкропр оцессоре-прототипе вьипе, чем в предлагаемом.

а f

Для удобства построения графика единица измерения времени выполнения микропрограмм принята равной К/ч(н.с.

- , 25 ТЗимволом I (4яг. 15) показан график зависимости времени выполнения микропрограмм для аркитектуры цредлагаемого устройства от значения коэффициента К. Значение коэффициента К при этом выбирается из следующих соображений: .. Обычно количество условных переходов в реальных микропрограммах (программах) в среднем составляет 20% от общего числа переходов. Коли чество же безусловных переходов гораздо меньше. . Мы можем принять количество микрокоманд безусловного перехода равК, О 0,1 0,2 0,3

К 0,85 0,7 0,55 0,4 0,25 Символом II (фаг. 15) показано семейство зависимостей времени выполнения микропрограммы, от коэффициента К- ,гу1Я архитектуры прототипа. Семейство зависимостей построено при различных значениях. После няя зависимость в семействе (,5 приведена для случая конкретной реализации микропроцессора-прототи на микропроцессорном наборе серии 589, При этом предлагаемое устройство реализуется на той же элемент ной базе и при использовании памяти кмкрокоманд такого же быстродей ствия, что и прототип.. В табл. 6 указаны параметры обе их вариантов реализации мкpoпpoцессора. Таблицаб Длительность цикла операционного блока (min), НС Длительность цикла NSiKpoKOMaHAbt (min),Hc 100

0,1 О

о

о

о 21 шм половине числа микрокоманд условного перехода. Тогда K l-l,iK При ,7 значен ге К принимается равным нулю. В этом случае берется во внимание наихудший вариант, имеющий максимальное время выполнения микропрограммы, так как учитывается максимальное число ИспользуеMbDc в .микропрограмме микрокоманд условного и безусловного перехода. ( . Зависимость коэффициента К/ от. коэффициента Kg для предлагаемого устройства следующая: 0,5 0,6 0,7 0,8 0,9 1 Из приведенных (фиг. 15) зависимостей нетрудно заметить, что при данной технической реализации обеих вариантов сокращение бремени выполнения микропрограмм в предлагаемом микропроцессоре по сравнению с прототипом составляет около 1,5 раза. Таким образом, предлагаемый микропроцессор использует мигшмальный цикл кмкрокоманды, равный циклу ра;боТы операционного блока, в отличие от прототипа, где цикл микрокоманды определяется быстродействием управляющей части микропроцессора (память микрокоманд, генератор последовательности адресов) и оказывается больше оптимального. Эа счет сокращенного цикла микрокоманды предлагаемый микропроцессор более производителен по сравнению с прототипом. Кроме того, при работе устройства с максимальным быстродействием цикл считывания микрокоманда из памяти оказывается более длинным, чем в работающем с максимальным быстродействием устройстве-прототипе. Данное обстоятельство позволяет использовать в предлагаемом устройстве менее быстродействукицую и, следовательно, более дешевую память микрокоманд.

Г/ Т ttf ,.

k / /

Г tiOK eaff«po6ana йменубт oHmfpDaim

. fetoemf нокроевнвнв

бйок квррекииа фазы

Фиг. f

F

51

®-щ

4f

1§И

.(

Фиг.

Фиг. 5

и

76 77 76 79

80 81 82 дЗ д

85

Фиг. W

- и

7S 77 78 79

во

81 К

83 8f 86

87 86 69 90 91

и

7В 77 78

79 дО &1 82

вз

86 87 88 89 90 S1

Фиг. 12

Фиг, 13

JLJUIJIJIJLJL JL-JlfL JL

Л

Т/ГП y/J

ЖП /ff2 I ff6

П

| I | |||

| Микропроцессор | 1982 |

|

SU1045231A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Прангишвилли Н.В | |||

| Микропроцессоры и микро-ЭВМ | |||

| М., Энергия, 1979, с | |||

| Огнетушитель | 0 |

|

SU91A1 |

Авторы

Даты

1985-06-30—Публикация

1984-01-05—Подача