21) 409 096/24-21 1:22) 18.07.86 46) 23.01.88. Бюл. № 3 (72) Ю.А.Базалев и В.И.Мяснов (53) 621.374(088.8) (56) Авторское свидетельство СССР 1225010, кл. Н ОЗК23/40, 02.10.84. Авторское свидетельство СССР 1243130, кл. Н 03 К 23/40, I7.01.85. i4) СИНХРОННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ

14

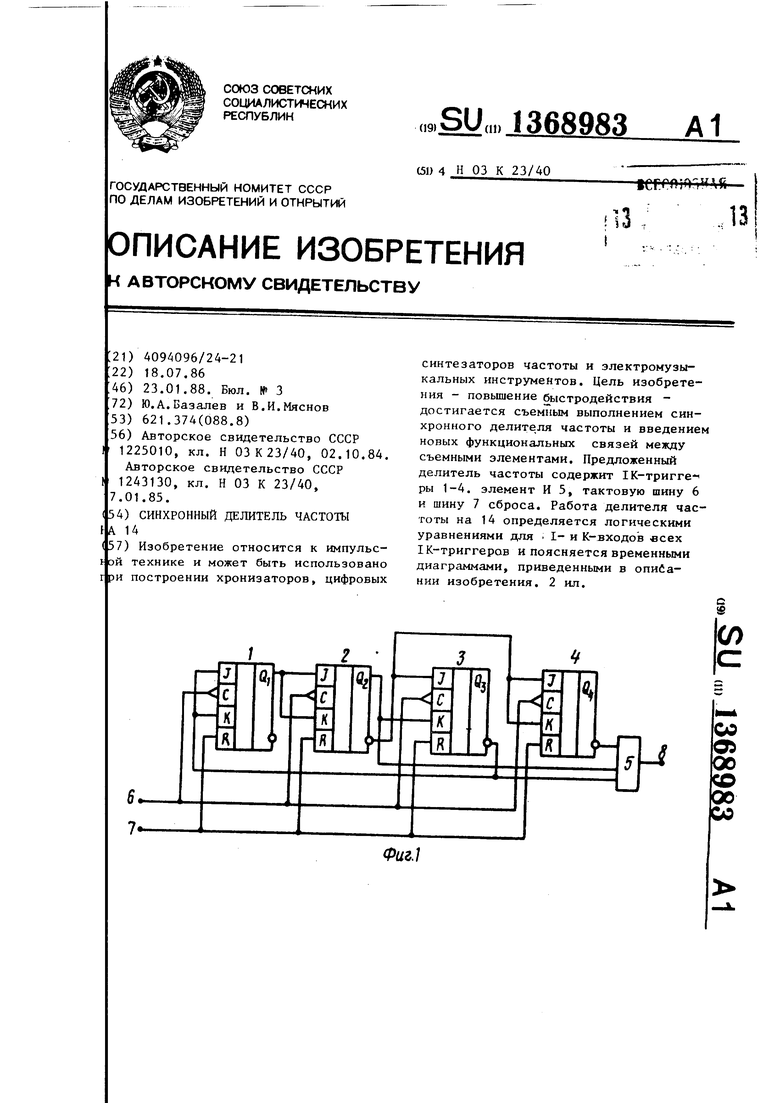

7) Изобретение относится к импульс- эй технике и может быть использовано )и построении хронизаторов, цифровых

синтезаторов частоты и электромузыкальных инструментов. Цель изобретения - повьпиение быстродействия - достигается съемным выполнением синхронного делите ля частоты и введением новых функциональных связей между съемными элементами. Предложенный делитель частоты содержит IK-тригге- ры 1-4. элемент И 5, тактовую шину 6 и шину 7 сброса. Работа делителя частоты на 14 определяется логическими уравнениями для I- и К-входов всех 1К-триггеров и поясняется временными диаграммами, приведенными в опийа- нии изобретения. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный делитель частоты на 17 | 1985 |

|

SU1285593A1 |

| Синхронный делитель частоты | 1986 |

|

SU1396275A1 |

| Синхронный делитель частоты | 1986 |

|

SU1396274A1 |

| Делитель частоты на 19 | 1984 |

|

SU1226660A1 |

| Синхронный делитель частоты | 1986 |

|

SU1406787A1 |

| Синхронный делитель частоты | 1987 |

|

SU1431066A1 |

| Синхронный делитель частоты | 1986 |

|

SU1396273A1 |

| Синхронный делитель частоты | 1986 |

|

SU1374425A1 |

| Синхронный делитель частоты на 10 | 1984 |

|

SU1225009A1 |

| Делитель частоты на 11 | 1987 |

|

SU1522398A1 |

U

со Од

00

со

ОС

00

Изобретение относится к импульсной технике и может быть использовано, например, для построения хронизато- ров, цифровых «синтезаторов частоты и электромузыкальных инструментов.

Цель изобретения - повышение быстродействия - достигается тем, что в известном синхронном делителе частоты на 14, содержащем четыре 1К-триг- гера и один элемент И, счетные входы всех 1К-триггеров соединены с тактовой шиной, а R-входы - с шиной сброса, инверсный выход второго 1К-триг- гера соединен с 1-входом третьего 1К-триггера и с первым входом, а прямой выход - с К-входом третьего 1К-триггера и с первым входом элемента И, второй вход которого соединен с инверсным выходом третьего 1К-триг гера, в котором инверсный выход третьего 1К-триггера соединен с I- и К-входами первого 1К-триггера, прямой выход которого соединен с I- и К-входами второго 1К-триггера, ин- версный выход которого соединен с I- и К-входами четвертого 1К-тригге- ра, инверсный выход которого соединен с третьим входом элемента И, вы ход которого образует выходную шину устройства.

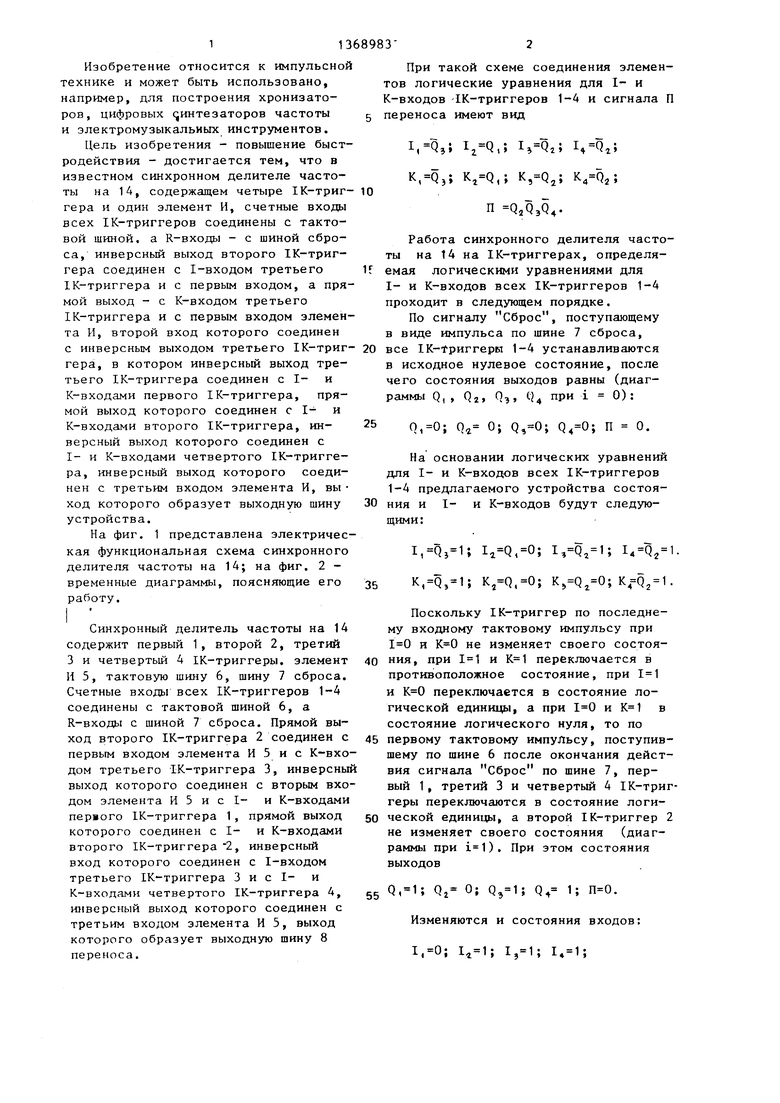

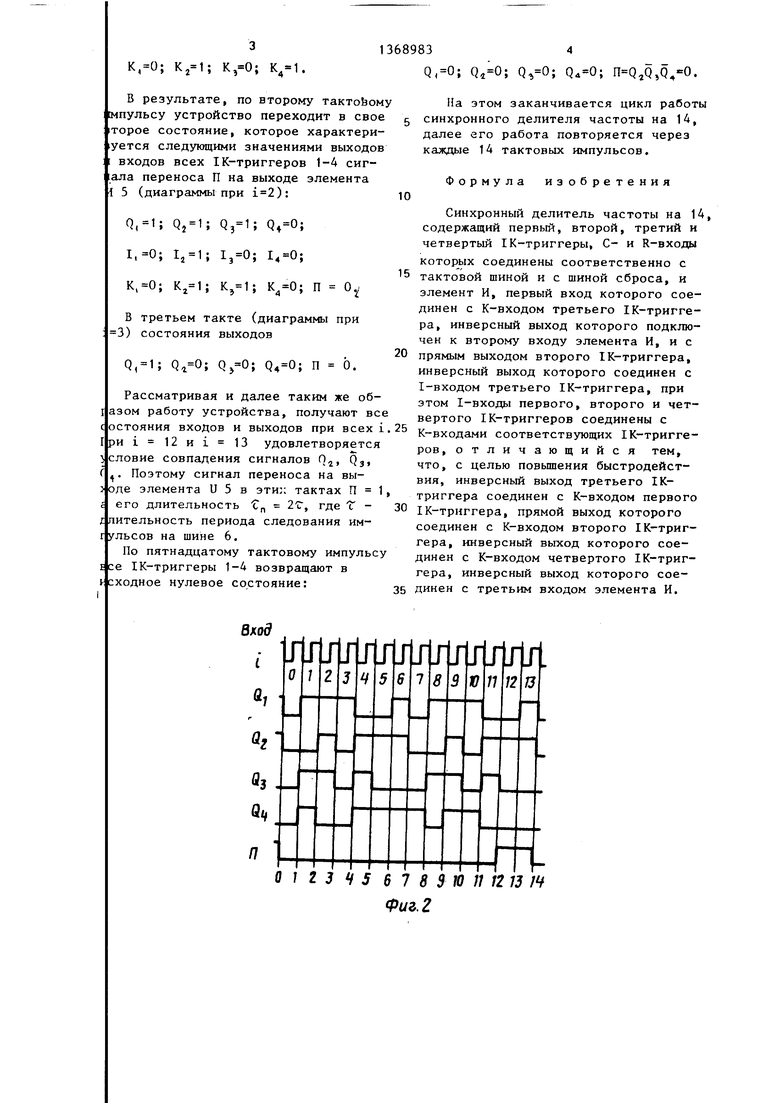

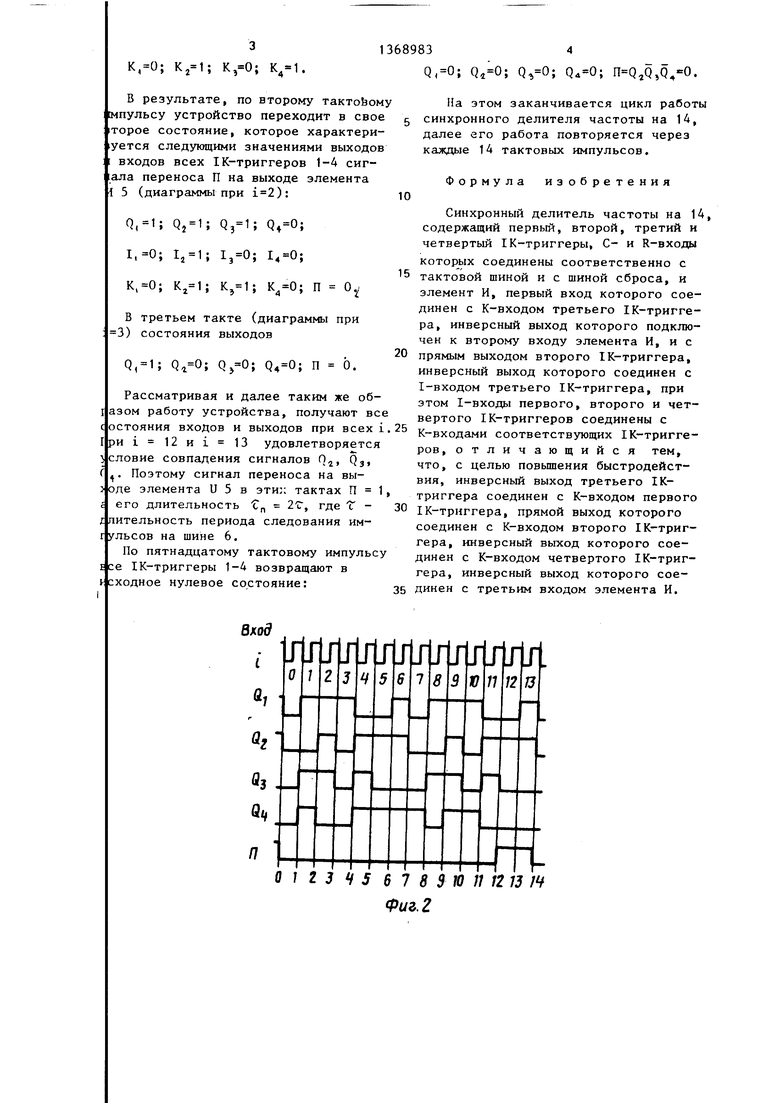

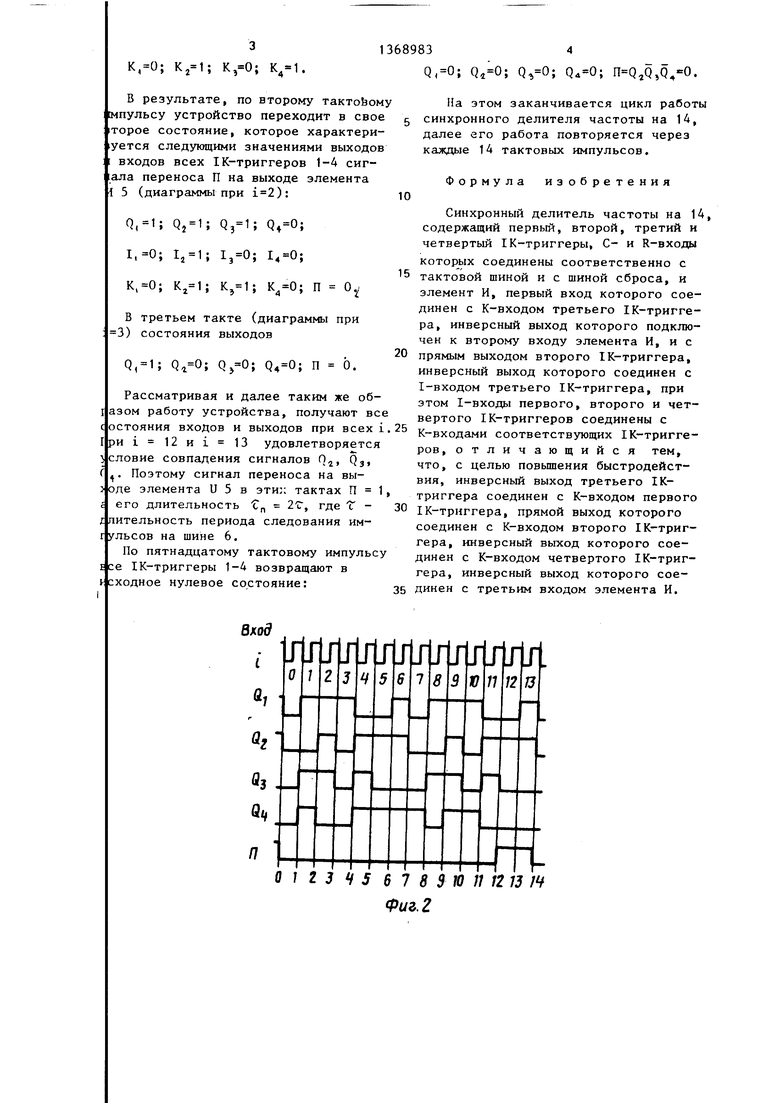

На фиг. 1 представлена электрическая функциональная схема синхронного делителя частоты на 14; на фиг. 2 - временные диаграммы, поясняющие его работу.

Синхронный делитель частоты на 14 содержит первый 1, второй 2, третий 3 и четвертый 4 1К-триггеры. элемент И 5, тактовую шину 6, шину 7 сброса. Счетные входы всех 1К-триггеров 1-4 соединены с тактовой шиной 6, а R-Бходы с шиной 7 сброса. Прямой выход второго 1К-триггера 2 соединен с первым входом элемента И 5 и с К-входом третьего 1К-триггера 3, инверсный выход которого соединен с вторым входом элемента И 5 и с 1- и К-входами первого 1К-триггера 1, прямой выход которого соединен с I- и К-входами второго 1К-триггера 2, инверсный вход которого соединен с 1-входом третьего ХК-триггера 3 и с I- и К-входами четвертого 1К-триггера 4, инверсный выход которого соединен с третьим входом элемента И 5, выход которого образует выходную шину 8 переноса.

При такой схеме соединения элементов логические уравнения для I- и К-входов -ГК-триггеров 1-4 и сигнала переноса имеют вид

i,Q,; ,; .; i,Qi;

K,Q3; K,Q,; K,Q,; K,Qj ;

П Q2Q3Q4.

Работа синхронного делителя частоты на 14 на 1К-триггерах, определяемая логическими уравнениями для I- и К-входов всех 1К-триггеров 1-4 проходит в следующем порядке.

По сигналу Сброс, поступающему в виде импульса по шине 7 сброса, все 1К-ТриггерБ1 1-4 устанавливаются в исходное нулевое состояние, после чего состояния выходов равны (диаграммы Q,, Qj, Q,, Q при i 0):

0,0; 0 0; Q,0; П 0.

На основании логических уравнений для I- и К-входов всех 1К-триггеров 1-4 предлагаемого устройства состояния и 1- и К-входов будут следующими:

I, ,O; I,Q,1; K,Q,1; K,Q,0; K,

Поскольку IK-триггер no последнему входному тактовому импульсу при и не изменяет своего состояния, при и переключается в противоположное состояние, при и переключается в состояние логической единицы, а при и в состояние логического нуля, то по первому тактовому импульсу, поступившему по шине 6 после окончания действия сигнала Сброс по шине 7, первый 1, третий 3 и четвертый 4 1К-три геры переключаются в состояние логической единицы, а второй 1К-триггер не изменяет своего состояния (диаг- раммы при ). При этом состояния выходов

Q,1; QZ 0; Q,1; Q 1; . Изменяются и состояния входов; 1,0; 1,1;

К,0; К,0; .

в результате, по второму тактоЬому мпульсу устройство переходит в свое

орое состояние, которое характери- гется следующими значениями выходов

входов всех 1К-триггеров 1-4 сигала переноса П на выходе элемента

5 (диаграммы при ):

Q,i;

I,0; I,0; I,0;

K,0; П третьем такте (диаграммы при 3) состояния выходов

Q,i; п о.

Рассматривая и далее таким же об- ззом работу устройства, получают все )стояния входов и выходов при всех i. 25 удовлетворяется ловие совпадения сигналов 0, Qj, . Поэтому сигнал переноса на вы- оде элемента U 5 в этих тактах П 1,

его длительность €„ 2Т, где Т - 30 лительность периода следования им- льсов на шине 6.

По пятнадцатому тактовому импульсу се 1К-триггеры 1-4 возвращают в ходное нулевое состояние: ,.

оЬ

13689834

Q,0; Q,0; ,Q,Q,0.

10

15

0

5

0

,.

Ь

На этом заканчивается цикл работы синхронного делителя частоты на 14, далее его работа повторяется через каждые 14 тактовых импульсов.

Формула изобретения

Синхронный делитель частоты на 14, содержащий первый, второй, третий и четвертый 1К-триггеры, С- и R-входы

которых соединены соответственно с тактовой шиной и с шиной сброса, и элемент И, первый вход которого соединен с К-входом третьего 1К-тригге- ра, инверсный выход которого подключен к второму входу элемента И, и с прямым выходом второго 1К-триггера, инверсный выход которого соединен с 1-входом третьего 1К-триггера, при этом 1-входы первого, второго и четвертого 1К-триггеров соединены с К-входами соответствующих 1К-тригге- ров, отличающийся тем, что, с целью повьшения быстродействия, инверсный выход третьего IK- триггера соединен с К-входом первого 1К-триггера, прямой выход которого соединен с К-входом второго 1К-триг- гера, инверсный выход которого соединен с К-входом четвертого 1К-триг- гера, инверсный выход которого соединен с третьим входом элемента И.

Авторы

Даты

1988-01-23—Публикация

1986-07-18—Подача