(риг. г Изобретение относится к вычислительной технике и может быть использовано при построении хронизаторов, цифровых синтезаторов частоты и т.п. Целью изобретения является-повышение надежности работы устройства путем сокращения числа элементов и цепей, а также увеличение длительности импульсов переноса, что повышает наделшость устройствпри их кас

кадном соединении.

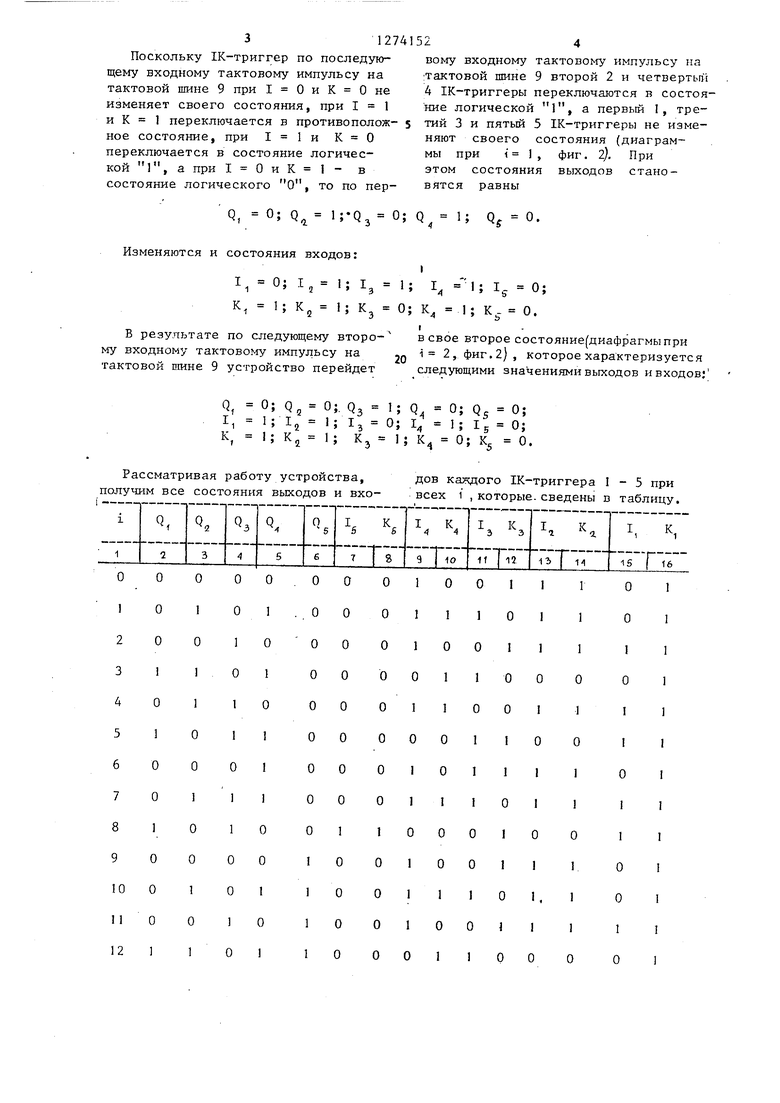

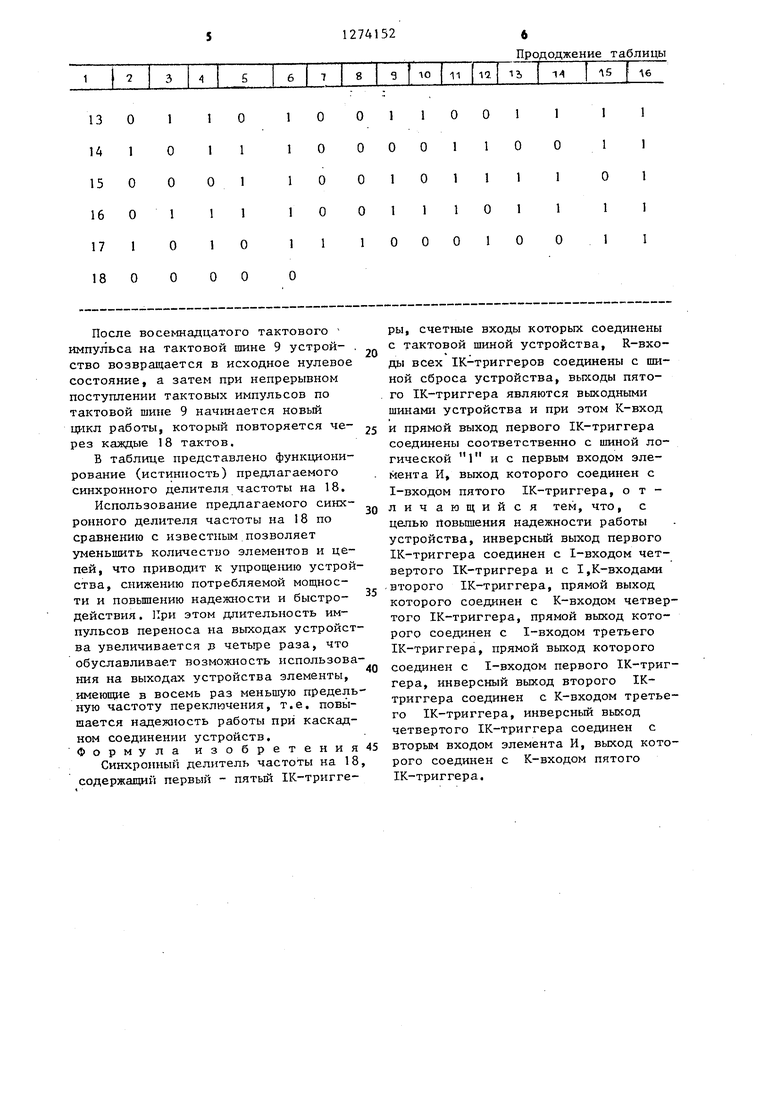

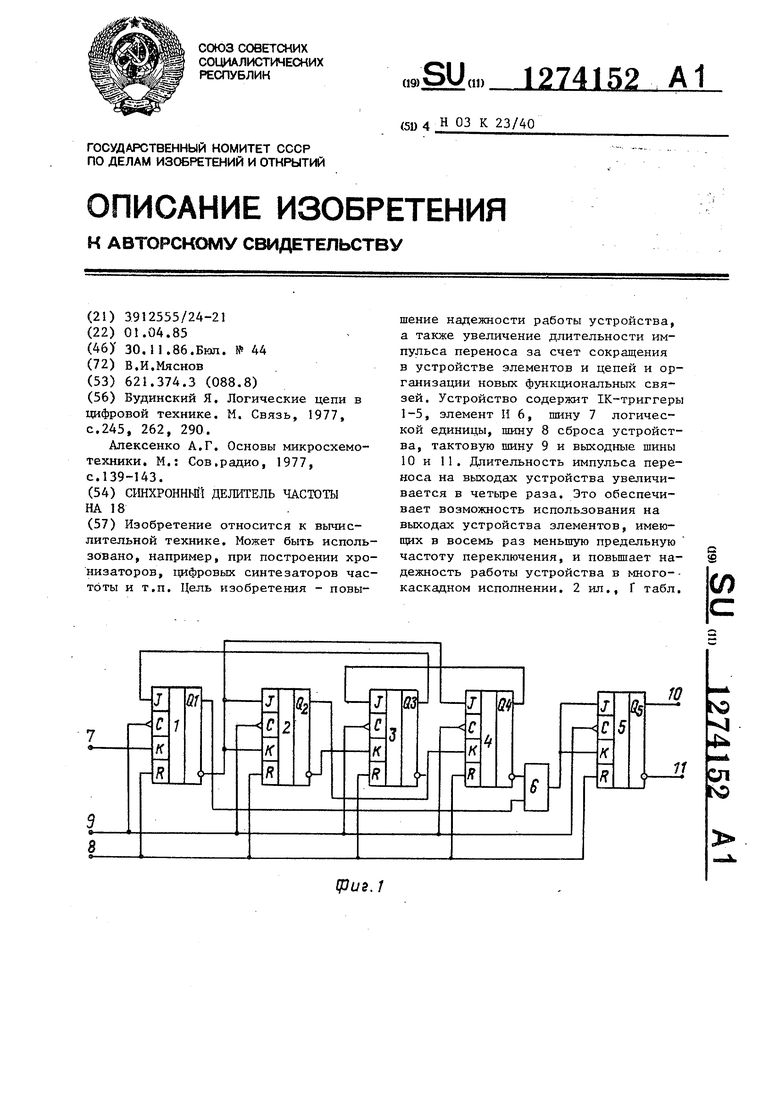

На фиг. I приведена функциональная схема синхронного делителя частоты на 18; на фиг. 2 - временные диаграммы работы устройства.

Синхронный делитель частоты на 18 содержит первый - пятый 1К-триггеры 1-5, элемент И 6, шину 7 логичест кой , шину 8 сброса устройства, тактовую шину 9 устройства и выходные шины 10 и 11.

Счетные входы всех 1К-триггеров 1 - 5 соединены с тактовой шиной 9 устройства, R-входы всех 1К-триггеров 1-5 соединены с шиной 8 сброса устройства, выходы пятого IKQ.; 1, Q,;

1 .5

5 г

к, К Kj Q,; К Q,; К, ,:

На фиг. 2 приняты следующие ЛЗозначения:

L- порядковый номер состояния предлагаемого синхронного делителя частоты на 18; порядковый номер входного тактового импульса на тактовой ишне 9;

я - входной сигнал на тактовой шине 9;

S - сигнал

Q на прямом выходе Q первого 1К-триггера 1;

В - сигнал Q на прямом выходе Q второго 1К-триггера 2;

г - сигнал Q , прямом выходе третьего 1К триггера 3;

3

g - сигнал Q на прямом выходе четвертого 1К-триггера 4;

Q.

е - сигнал Qg на прямом выходе пятого ТК триггера 5.

Q, 0; Q, 0; Q,

На основании логических уравнений для I- и К-входов 1К-триггеI, Q 0; 1, Q 1; I К, 1; К Q 1; К Qj 1; К, Q

1-входом третьего 1К-триггера 3, прямой выход которого соединен с 1-входом первого 1К-триггера 1, прямой выход которого соединен с первым входом элемента И 6, выход которого соединен с 1-й К-входами пятого IKтриггера, а второй вход соединен с инверсным выходом четвертого 1К-триггера 4, инверсный выход второго IKтриггера 2-соединен с К-входом третьего 1К-триггера 3.

За счет такой схемы соединения элементов логические уравнения для I и К-входов всех 1К-триггеров

1 - 5 синхронного делителя частоты на 18 6yfs,yT следующими (фиг. 1) :

,5 s

Q,Q,5

На фиг. 1 и 2 принято, что IKтриггеры 1 - 5 переключаются под действием отрицательного перепада сиг- нала в момент изменения его с высокого уровня (логической 1) на низкий уровень (логического О) на входной тактовой шине 9.

Работа синхронного делителя частоты на 18 полностью определяется

логическими уравнениями для I- и К-входов его 1К-триггеров.

По сигналу Сброс, поступающему в виде импульса перед началом работы устройства по шине 8 сброса, по

входам R все 1К-триггеры 1 - 5 устанавливаются в исходное нулевое состояние. В этом случае (диаграммы при , фиг.2) состояния выходов предлагаемого устройства равны

s °

0; Q 0;

ров 1 - 5 предлагаемого устройства состояния входов следуюшие:

0; 1, Q, 1; 1 Q,Q, 0; триггера 5 являются выходными шинами 10 и 11 устройства. Шина 7 логической 1 соединена с К-входом первого 1К-триггера 1, инверсный выход которого соединен с 1-входом четвертого 1К-триггера 4 и с 1,К-входами второго 1К-триггера 2, прямой выход которого соединен с К-входом четвертого 1К-триггера 4, прямой выход которого соединен с 0; к Q,Q - 0.

312741

Поскольку IK-триггер по последующему входному тактовому импульсу на тактовой шине 9 при изменяет своего состояния, при I 1 и К 1 переключается в противополож- 5 нов состояние, при I 1 и К О переключается в состояние логической 1, а при I О и К 1 - в состояние логического О, то по пер Q, 0; Q IrQj 0; Q 1; Q 0.

Изменяются и состояния входов:

I, 0; I, 1; 1 1; 1 Ч ; I. 0;

К, 1; К 1; Kg 0; К 1; К- 0.

В результате по следующему второ- в свое второе состояние(диафрагмы при

му входному тактовому импульсу на 20 2, фиг.2), которое характеризуется тактовой шине 9 устройство перейдет следующими значениями выходов и входов;

0;. Q3 1; Q 0; Q 0; 1; 1з 0; I, I; Is 0; 1; Kj 1; К 0; К 0.

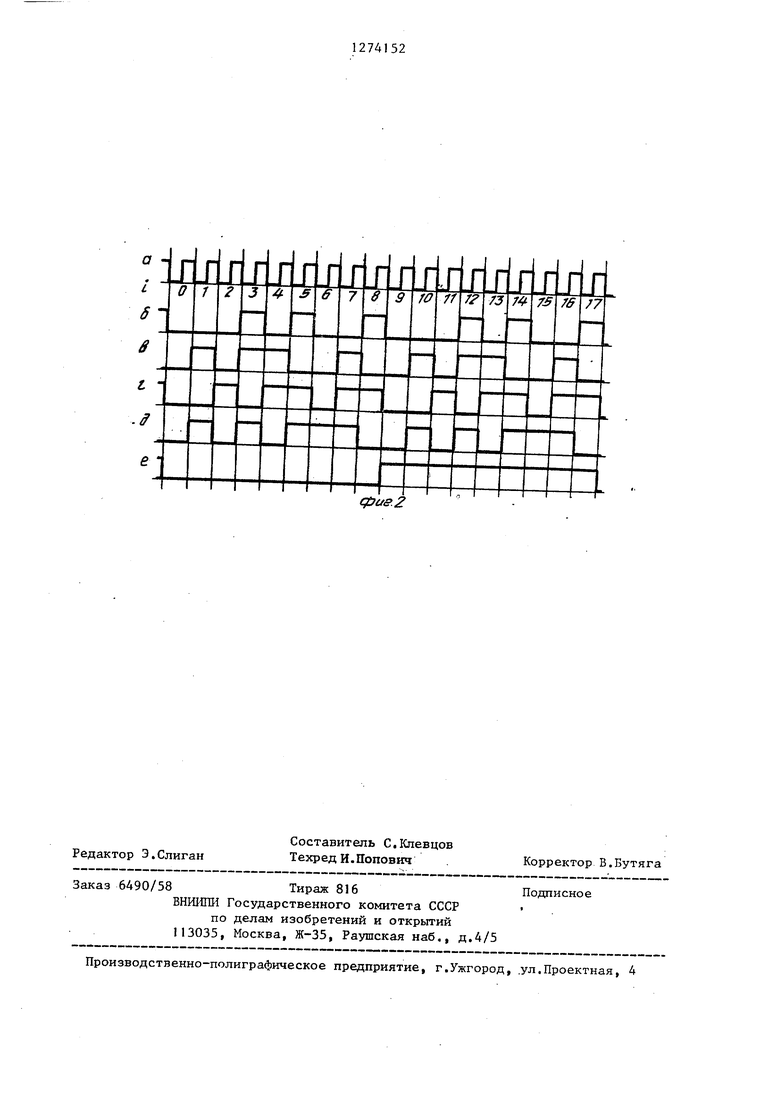

Рассматривая работу устройства, получим все состояния выходов и вхо24

вому входному тактовому импульсу на ;тактовой шине 9 второй 2 и четвертьп-i 4 1К-триггеры переключаются в состояние логической 1, а первый 1, третий 3 и пятый 5 1К-триггеры не изменяют своего состояния (диаграммы при 1 , фиг. 2), При этом состояния выходов становятся равны

дов каждого 1К-триггера I - 5 при всех 1 , которые.сведены в таблицу.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный делитель частоты на 17 | 1985 |

|

SU1285593A1 |

| Делитель частоты на 19 | 1984 |

|

SU1226660A1 |

| Синхронный делитель частоты | 1986 |

|

SU1374425A1 |

| Синхронный делитель частоты | 1987 |

|

SU1431066A1 |

| Синхронный делитель частоты | 1986 |

|

SU1396273A1 |

| Синхронный делитель частоты | 1986 |

|

SU1354415A1 |

| Синхронный делитель частоты | 1986 |

|

SU1406785A1 |

| Синхронный делитель частоты на 47 | 1990 |

|

SU1714806A1 |

| Синхронный делитель частоты на 14 | 1986 |

|

SU1368983A1 |

| Синхронный делитель частоты на 21 | 1985 |

|

SU1267613A1 |

Изобретение относится к вычислительной технике. Может быть использовано, например, при построении хронизаторов, цифровых синтезаторов частоты и т.п. Цель изобретения - повышение надежности работы устройства, а также увеличение длительности импульса переноса за счет сокращения в устройстве элементов и цепей и организации новых функциональных связей. Устройство содержит 1К-триггеры 1-5, элемент И 6, шину 7 логической единицы, шину 8 сброса устройства, тактовую шину 9 и выходные шины 10 и 11. Длительность импульса переноса на выходах устройства увеличивается в четьфе раза. Это обеспечивает возможность использования на выходах устройства элементов, имеющих в восемь раз меньшую предельную с (О частоту переключения, и повьш1ает надежность работы устройства в много-(Л каскадном исполнении. 2 ил., Г табл.

1 1

1 О

12 1 О

О 1 О О j

1 о

о о 1

о о

После восемнадцатого тактового импульса на тактовой шине 9 устройство возвращается в исходное нулевое состояние, а затем при непрерывном поступлении тактовых импульсов по тактовой шине 9 начитается новый цикл работы, который повторяется через каждые 18 тактов.

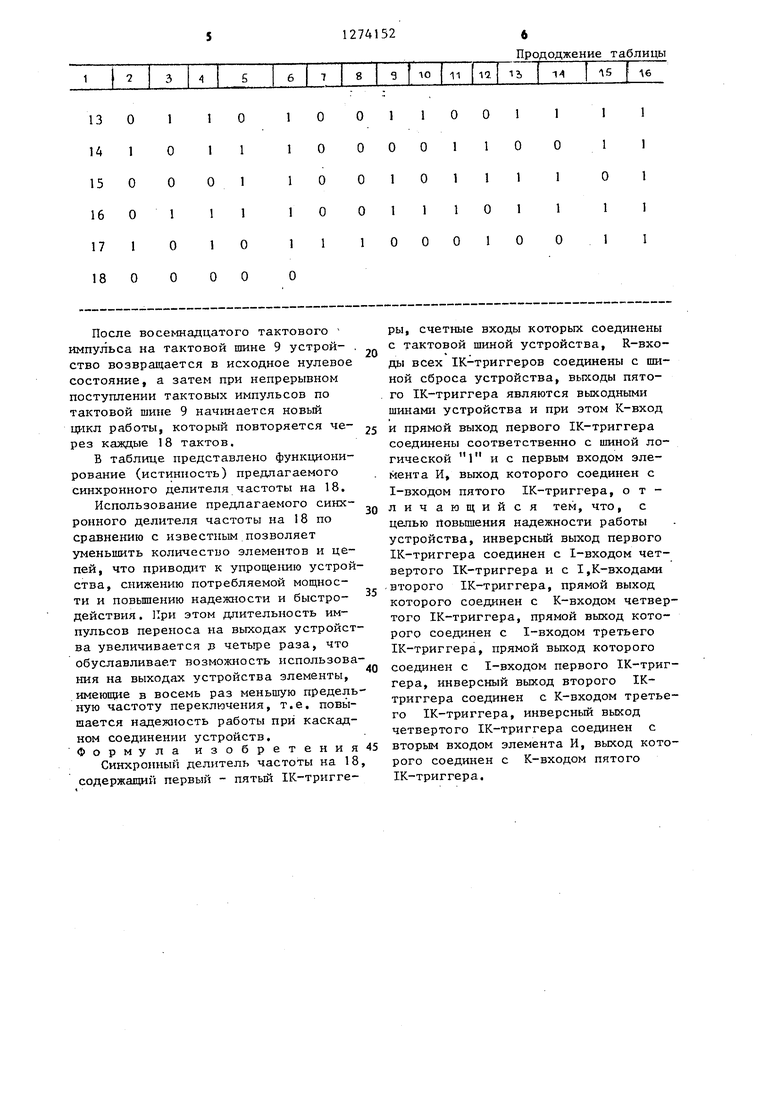

В таблице представлено функционирование (истинность) предлагаемого синхронного делителя частоты на 18.

Использование предлагаемого синхронного делителя частоты на 18 по сравнению с известным позволяет уменьшить количество элементов и цепей, что приводит к упроще1Ш10 устройства, снижению потребляемой мощности и повышению надежности и быстродействия. При этом длительность импульсов переноса на выходах устройства увеличивается дз четыре раза, что обуславливает возможность использования на выходах устройства элементы, имеющие в восемь раз меньшую предельную частоту переключения, т.е. повышается надежность работы при каскадном соединении устройств. Формула изобретения

Синхронный делитель частоты на 18 содержащий первый - пятый 1К-триггеПрододжение таблицы

ры, счетные входы которых соединены с тактовой шиной устройства, R-BXOды всех 1К-триггеров соединены с шиной сброса устройства, вьпсоды пятого 1К-триггера являются выходными шинами устройства и при этом К-вход и прямой выход первого 1К-триггера соединены соответственно с шиной логической 1 и с первым входом элемента И, выход которого соединен с 1-входом пятого 1К-триггера, отличающийся тем, что, с целью Повышения надежности работы устройства, инверсный выход первого 1К-триггера соединен с 1-входом четвертого 1К-триггера и с 1,К-входами второго 1К-триггера, прямой выход которого соединен с К-входом четвертого 1К-триггера, прямой выход которого соединен с 1-входом третьего 1К-триггера, прямой выход которого соединен с 1-входом первого 1К-триггера, инверсный выход второго IKтриггера соединен с К-входом третьего 1К-триггера, инверсный выход четвертого 1К-триггера соединен с вторым входом элемента И, выход которого соединен с К-входом пятого 1К-триггера.

фае. 2

| Будинский Я | |||

| Логические цепи в цифровой технике | |||

| М | |||

| Связь, 1977, с.245, 262, 290 | |||

| Алексенко А.Г | |||

| Основы микросхемотехники, М.: Сов,радио, 1977, с.139-143. |

Авторы

Даты

1986-11-30—Публикация

1985-04-01—Подача