(54) УСТРОЙСТВО ДЛЯ ОБМЕНА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения блоков обработки данных | 1980 |

|

SU993235A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1991 |

|

SU1837303A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| Устройство для формирования синхроимпульсов | 1978 |

|

SU767747A1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2011 |

|

RU2444052C1 |

| КОНТРОЛЛЕР ПЕРЕДАЧИ ДАННЫХ | 2013 |

|

RU2514135C1 |

| Программируемый контроллер | 1989 |

|

SU1741100A1 |

| Резервированный генератор синхроимпульсов | 1984 |

|

SU1175037A1 |

| Устройство для контроля параметров датчиков телевизионного сигнала | 1980 |

|

SU856029A1 |

| Селектор импульсных сигналов | 1982 |

|

SU1058043A1 |

1

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах с асинхронным обменом информацией между блоками.

Известны устройства обмена с фиксированной продолжительностью цикла обмена, имеющие блок сопряжения и блок синхронизации, который формирует синхронизирующие импульсы через постоянные промежутки времени fl.

Однако при использовании устройства обмена для передачи информации между разными блоками, имеющими различные временные характеристики, необходимо разрабатывать вновь блок сопряжения и блок синхронизации.

Известно устройство, содержащее несколько переключаемых генераторов синхросигналов, что позволяет производить обмен с несколькими фиксированными скоростями 12.

Недостатком этого устройства является то, что при необходимости организовать обмен между большим числом разнотипных блоков требуется большое число генераторов синхроси: налов.

Указанные недостатки устранены в устройствах с асинхронным обменом управляемых сигналами запроса и готовности к обмену, формируемыми

соответственно ведущим и обменивающимися устройствами.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее блок формирования сигнала прерывания, который по сигналу обращения подает на участвуквдую в обмене ЭВМ сигнал прерывания. Сигналом прерывания ЭВМ устанавливается в режим динамического

останова до последующего прерывания запросом на обработку данных

Гз.

Недостатком этого устройства является то, что после появления сигнала расходуется дополнительное время, длительность которого определяется длительностью цикла между моментами анализа сигнала. При программной организации анализа сигнала это время может достигать нескольких г шкросекунд, что при передаче значительных потоков информации, например между блоком переработки (процессором) и запоминанвДим блоком является неприемлемым.

Цель изобретения - повышение быстродействия устройства.

Эта цель достигается тем, что в устройство введены коммутатор и блок управления, первый выход которого соединен с установочным входом формирователя синхроимпульсов, второй выход которого соединен с первым стробируквдим входом блока управления, к второму стробирующему входу которого подключен первйй выход задающего генератора, второй выход которого подсоединен к входу коммутатора, выход которого подключен к синхронизируннцему входу формирователя синхроимпульсов, управлякадий вход коммутатора подключен к второму выходу блока управления, первый управляющий вход которого является первым входом устройства, второй управлякхций вход его - вторым входом устройства, а третий управляющий вход третьим входом устройства. Блок управления содержит триггер RS-типа, два элемента И и элемент ИЛИ, первый вход которого является первым управляющим входом блока, второй вход элемента ИЛИ является третьим управляющим входом блока, а выход его подключен к первому входу первого элемента И, второй вход которого является вторым стробирующим входом блока, а выход его соединен с первым установочным входом триггера RS-типа, к второму установочному входу которого подключен выход второго элемента И, который первым выходом блока, первый вход второго элемента И является первым стробирующим входом блока, второй вход второго элемента И является вторым управлянвдим входом блока, выход триггера RS-типа является вторым выходом блока.

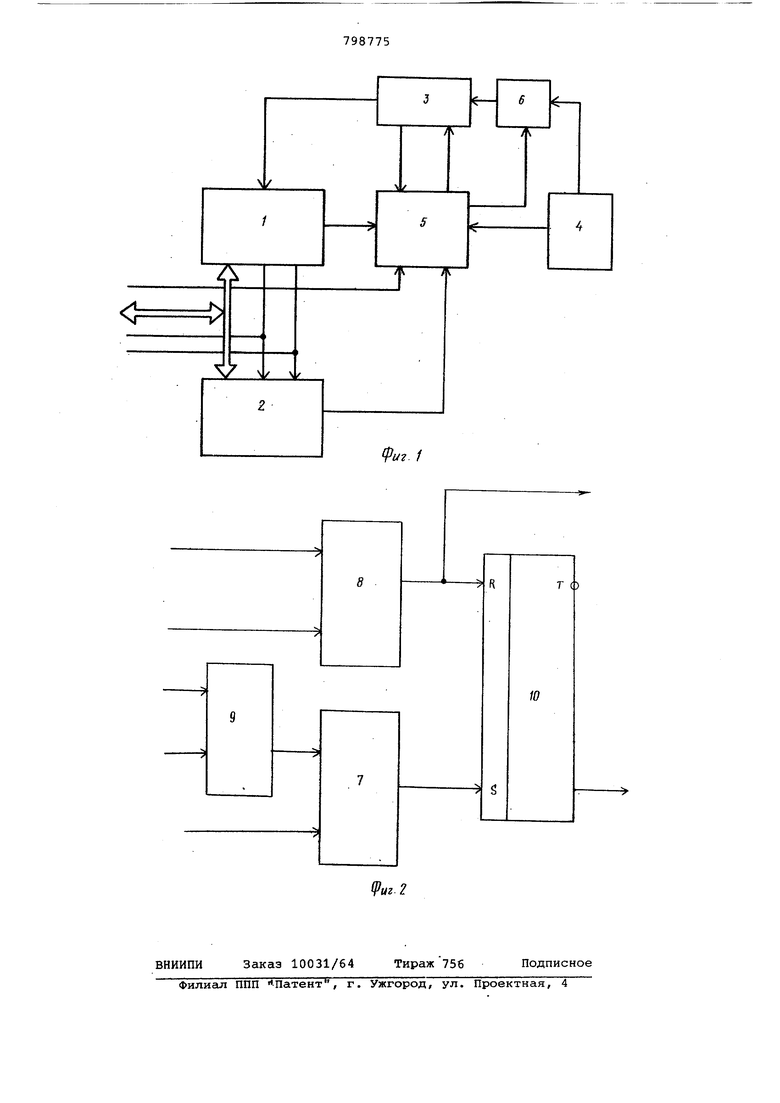

На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. 2 - схема блока управления.

Устройство содержит блок 1 переработки информации, запоминающий блок 2, формирователь 3 синхроимпульсов , задающий генератор 4, блок 5 управления, коммутатор 6.

Блок управления содержит первый 7 и второй 8 элементы И, элемент ИЛИ 9 и триггер 10 RS-типа.

. Блок переработки и запоминающий блок связаны информационными и управляющими связями, к которым могут быть подключены внешние устройства. Первый и второй .управляющие входы блока управления подключены соответственно к выходу запоминающего блок и выходу блока переработки. Третий управляющий вход блока управления является входом устройства, к которому может подключаться внешнее запоминанячее устройство. Синхронизирующий вход блока переработки подключен .к первому выходу формироват«ля синхроимпульсов. Второй выход этого формирователя подключен к первому стробирующему входу блока упраления, к его второму стробирующему входу подключен первый выход задающего генератора. Первый выход блока управления подключен к установочному входу формирователя синхроимпульсов , а второй выход блока к управляющему входу коммутатора, вход которого подключен к второму выходу задающего генератора, а выход к синхронизирующему входу формирователя синхроимпульсов.

Первый управляющий вход блока управления является первым входом элемента ИЛИ 9, второй вход которого является третьим управляющим входом блока, а выход подключен к первому входу первого элемента И 7, выход которого подключен к первому установочному входу триггера 10, а второй вход первого элемента И является вторым стробирующим входом блока. Первый и второй входы второго элемента И 8 являются соответственно первым стробирующим и вторым управляющим входами блока. Выход этой схемы является первым выходом блока и подключен к второму устновочному входу триггера, выход которого является вторым выходом блока.

Устройство для обмена работает следующим образом.

Задающий генератор вырабатывает последовательность импульсов, проходящих через коммутатор на вход формирователя. Формирователь циклическ вырабатывает серии синхроимпульсов, поступающих в блок переработки. При обращении к запоминающему блоку, бл переработки формирует одновременно с сигналом обращения к запоминающему блоку и сигнал запроса, поступакяций на второй управляющий вход блока управления, формирователь 3 зканчивает по установочному сигналу вырабоку серии синхроимпульсов, обеспечивакадих завершение переработки информации в блоке 1, и по окончании последнего необходимого для обработки синхроимпульса (СИ) формирует управлягаций сигнал для коммутатора б. По этому сигналу коммутатор отключает задающий генератор 4 от формирователя 3, синхронизирукадий вход которого перестают поступать высокочастотные импульсы. Очередной СИ не вырабатывается и блок 1 переходит в режим статического останова. Сигнал, управляющий коммутатором б в блоке управления фиксируется на триггере.

После окончания процесса выборки информации запоминающий блок формирует сигнал Готовность, поступающий на первый управляющий вход блока управления. По совпадению этого

сигнала с импульсом высокой частоты, поступающему из задающего генератора, управляющий сигнал с входа коммутатора снимается (триггер 10 возвращается в первоначальное состояние) , на вход формирователя начинают поступать импульсы высокой частоты с задающего генератора и формирователь вырабатывает синхроимпульс, по которому в блоке перера ботки производится обработка информации, поступившей из запоминающего блока в магистральные шины. Стробирование сигналов импульсами высокой частоты производится для исключения временных неопределенностей при работе схем.

В том случае, если время выборки из запоминающего блока мало и сигнал готовности появляется до синхроимпульса, по которому ведется обработка, останова не происходит. Работа происходит аналогично, если обращение ведется к внешнему устройству.

Введение блока управления, коммутатора и организации их связей в устройстве обеспечивает остановку выработки синхроимпульсов, начиная с синхроимпульса, по которому ведется обработка информации, принимаемой из запоминающего блока. Останов продолжается до момента появления сигнала Готовность на выходе запоминающего блока, свидетельствующего о наличии информации в магистральных шинах. Поскольку привязка сигнала Готовность производится к импульсам высокой частоты, период следования которых составляет -в современных устройствах 30-50 не, то толко этим и определяются потери времени при обмене, так как время срабатывания триггера укладывается в полупериод высокой частоты.

Устройство позволяет Организовать асинхронный обмен, практически без потерь времени на -обработку сигналов запрос-ответ и обеспечивает при обмене сокращение потерь времени от нескольких сотен наносекунд до микросекунд по сравнению с известными устройствами асинхронного обмена, в том числе и использующими режим динамического останог на. Это позволяет стыковать блок обработки с запоминающим блоком, существенно отличакацимися друг от друга быстродействием, при этом в каждом случае быстродействие при.обмене является максимальным для данного запоминаивдего блока и блока обработки. При наличии быстродействующего запоминающего блока, когда блок переработки работает медленно относительно запоминающего блока, скорость передачи полностью определяется блоком переработки, без дополнительных задержек.

Формула изобретения

и задающий генератор, причем первый выход формирователя синхроимпульсов является выходом устройства, от0личающееся тем, что, с целью повышения быстродействия устройства, в него введены коммутатор и блок управления, первый выход которого соединен с установочным вхо5дом формирователя.синхроимпульсов, второй выход которого соединен с первым стробирукщим входом блока управления, к второму стробирующему входу которого подключен первый выход задающего генератора, второй

0 выход которого подсоединен к входу коммутатора, выход которого подключен к синхронизирующему входу формирователя синхроимпульсов, управляющий вход коммутатора подключен к

5 второму выходу блока управления, первый управляющий вход которого является первым входом устройства, второй управляющий вход его - вторым входом устройства, а третий управ0ляющий вход - третьим входом устройства.

5 два элемента И и элемент ИЛИ, первый вход которого является первым управляющим входом блока, второй вход элемента ИЛИ является третьим управляющим входом блока, а выход его подключен к первому входу пер0вого элемента И, второй вход которого является вторым стробирукхиим входом блока, а выход его соединен с первым установочным входом триггера RS-типа, к второму установоч5ному входу которого подключен выход второго элемента И, который является первым выходом блока, первый вход . второго элемента И является первым стробирукадим входом блока,

O второй вход второго элемента И является вторым управляющим входом блока, выход триггера RS-типа является вторым выходом блока.

Источники информации,

5 принятые во внимание при экспертизе

0 кл. 97/7 D 1, 1975 (прототип). U. 1

Авторы

Даты

1981-01-23—Публикация

1978-12-09—Подача