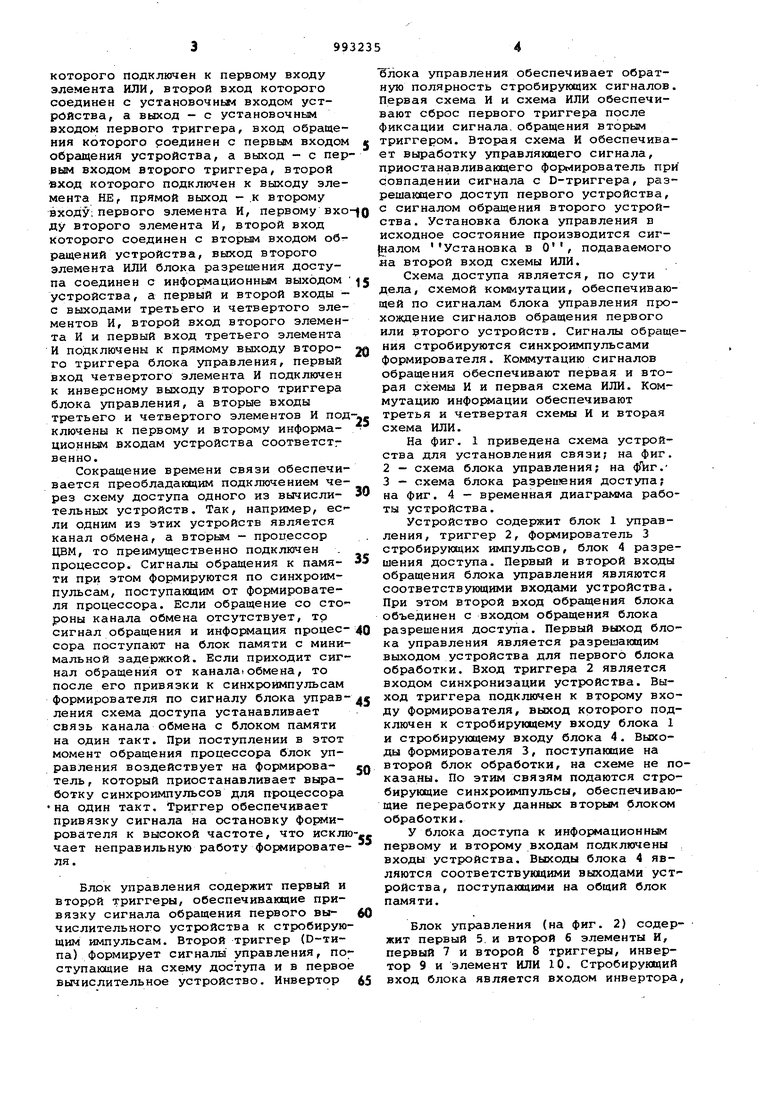

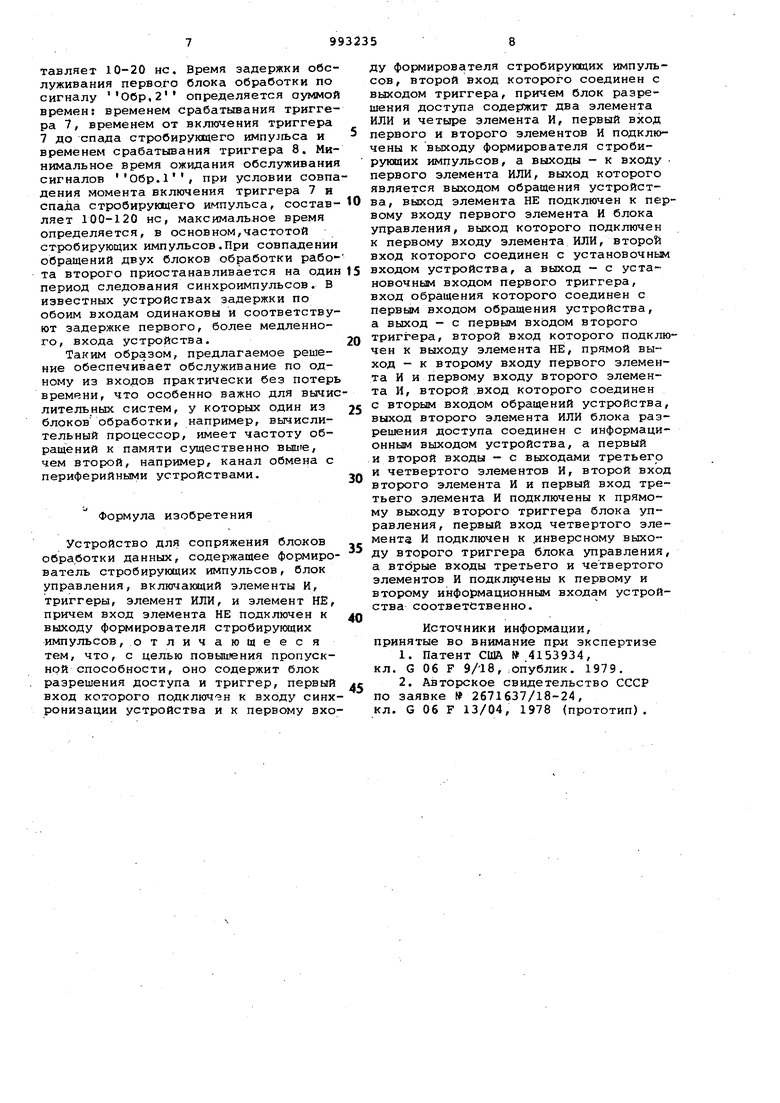

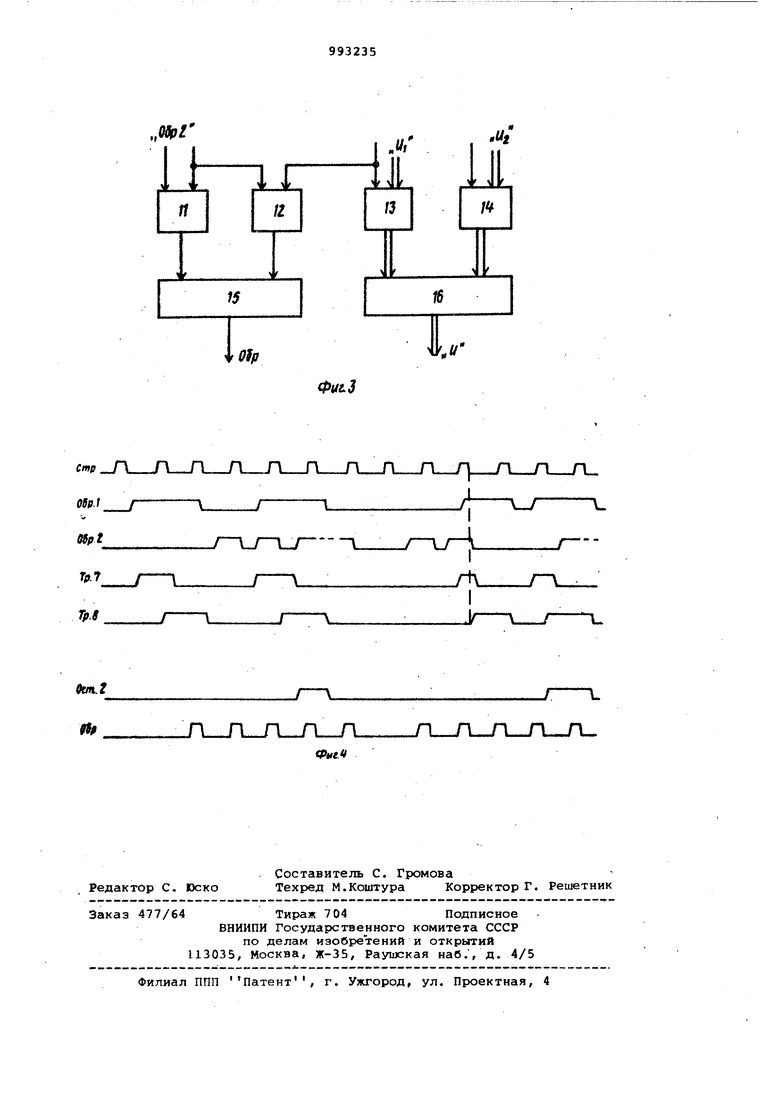

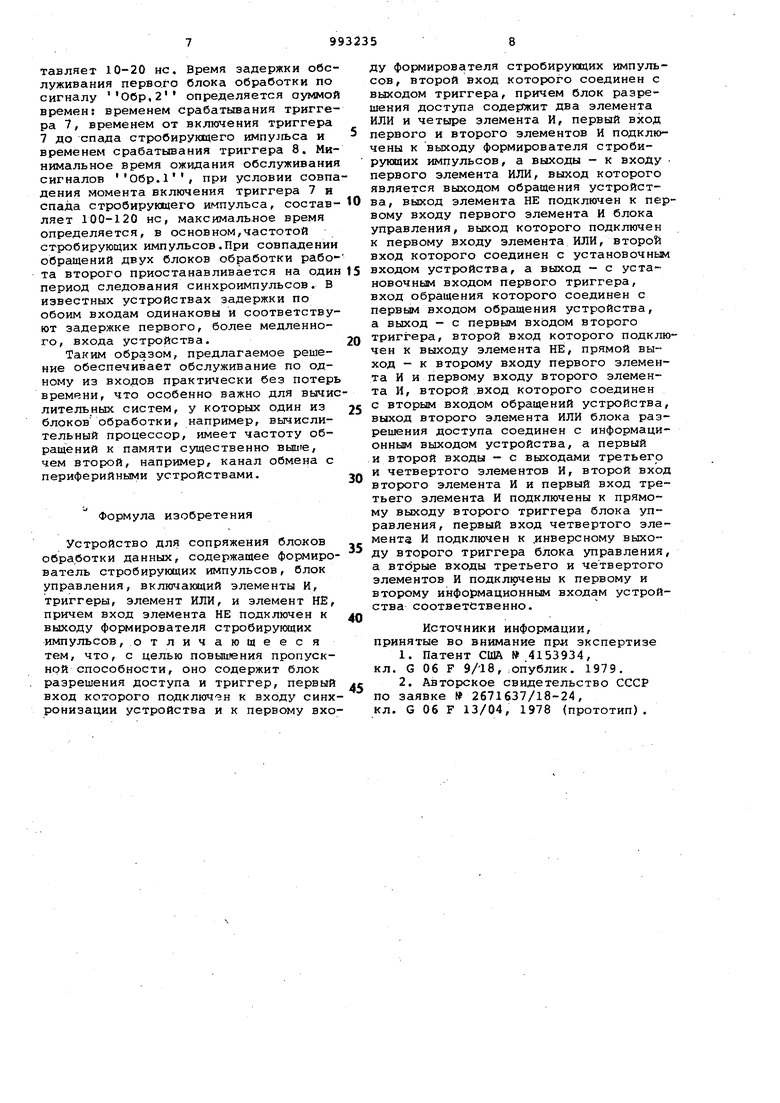

Изобретение относится к вычислительной технике и может быть примене но в системах, в которых один блок памяти одновременно используется несколькими блоками обработки информации. Известно устройство сопряжения бл ков обработки данных системы, в кото рой,, по крайней мере, два блока обра ботки информации используют одну общую память, содержащее блок управления 1 . Недостаток такой системы заключается в увеличении времени обмена изза необходимости программно-аппаратного анализа сигналов генератора пре рьшания при асинхронном обмене. Кроме того г увеличение времени происходит задержки связанной с после довательным прохождением сигнала обр щения к памяти через ряд логических схем, анализирующих наличие запросов и устанавливающих приоритет. Наиболее близким техническим реше нием к предлагаемому является устрой ство, содержащее блок управления и коммутатор, управляквдяе режимом запуска и останова формирователя соответственно сигналами из блока памяти и блока обработки информации 2. Недостатком данного устройства является невысокая пропускная способность . Цель изобретения - повышение пропускной способности при работе двух вычислительных устройств с общю блоком памяти. Поставленная цель достигается тем, что в устройство, содержащее формирователь стробируюиих импульсов, блок управления, включающий элементы И, триггеры, элемент ИЛИ, и элемент НЕ, причем вход элемента НЕ подключен к выходу формирователя стробирупцих импульсов , введены блок размещения доступа и триггер, первый вход которого подключен к входу синхронизации устройства и к первому входу формирователя стробирующих импульсов, второй вход которого соединен с выходом триггера, причем блок разреи ния доступа содержит два элемента ИЛИ и четыре элемента И, первый вход первого и второго элементов И подключены к выходу формирователя стробирующих импульсов, а выходы - к входу первого элемента ИЛИ, выход которого является выходсж обращения устройства,) выход элемента НЕ подключен к первому входу первого элемента И блока управления, выход которого подключен к первому входу элемента ИЛИ, второй вход которого соединен с установочным входом устройства, а выход - с установочным входом первого триггера, вход обращения которого роединен с первым входом обращения устройства, а выход - с пер вым входом второго триггера, второй вход которого подключен к выходу элемента НЕ, прямой выход - .к второму ВХОДУ; первого элемента И, первому вхо ду второго элемента И, второй вход которого соединен с вторым входом обращений устройства, выход второго элемента ИЛИ блока разрешения доступа соединен с информационным выходом устройства, а первый и второй входы с выходами третьего и четвертого элементов И, второй вход второго элемента И и первый вход третьего элемента И подключены к прямому выходу второГС триггера блока управления, первый вход четвертого элемента И подключен к инверсному выходу второго триггера блока управления, а вторые входы третьего и четвертого элементов И под ключены к первому и второму инфоЕялационным входам устройства соответстг венно. Сокращение времени связи обеспечивается преобладающим подключением через схему доступа одного из вычислительных устройств. Так, например, если одним из этих устройств является канал обмена, а вторым - процессор ЦВМ, то преимущественно подключен процессор. Сигналы обреидения к памяти при этом формируются по синхроимпульсам, поступающим от формирователя процессора. Если обращение со сто роны канала обмена отсутствует, то сигнал обращения и информация процессора поступают на блок памяти с минимальной задержкой. Если приходит сигнал обращения от канала обмена, то после его привязки к синхроимпульсам формирователя по сигналу блока управления схема доступа устанавливает связь канала обмена с блоком памяти на один такт. При поступлении в этот момент обращения процессора блок управления воздействует на формирователь, который приостанавливает выработку синхроимпульсов для процессора на один такт. Триггер обеспечивает привязку сигнала на остановку формирователя к высокой частоте, что исклю чает неправильную работу формирователя. Блок управления содержит первый и второй триггеры, обеспечивающие привязку сигнала обращения первого вычислительного устройства к стробирующим импульсам. Второй триггер (D-типа) формирует сигналы управления, по ступающие на схему доступа и в первое вычислительное устройство. Инвертор ёлока управления обеспечивает обратную полярность стробирующих сигналов. Первая схема И и схема ИЛИ обеспечивают сброс первого триггера после фиксации сигнала, обращения вторьм триггером. Вторая схема И обеспечивает выработку управляющего сигнала, приостанавливающего формирователь при совпадении сигнала с D-триггера, разрешающего доступ первого устройства, с сигналом обращения второго устройства. Установка блока управления в исходное состояние производится сиг{налом Установка в О, подаваемого на второй вход схемы ИЛИ. Схема доступа является, по сути дела, схемой коммутации, обеспечивающей по сигналам блока управления прохождение сигналов обращения первого или второго устройств. Сигналы обращения стробируются синхроимпульсами формирователя. Коммутацию сигналов обращения обеспечивают первая и вторая схемы И и первая схема ИЛИ. Коммутацию инфо 4ации обеспечивают третья и четвертая схемы И и вторая схема ИЛИ. На фиг. 1 приведена схема устройства для установления связи; на фиг. 2- схема блока управления; на фТиг.3- схема блока разрюи ения доступа; на фиг. 4 - временная диаграмма работы устройства. Устройство содержит блок 1 управления, триггер 2, формирователь 3 стробирующих импульсов, блок 4 разрешения доступа. Первый и второй входы обращения блока управления являются соответствующими входами устройства. При этом второй вход обращения блока объединен с входом обращения блока разрешения доступа. Первый выход блока управления является разрешающим выходом устройства для первого блока обработки. Вход триггера 2 является входом синхронизации устройства. Выход триггера подключен к второму входу формирователя, выход которого подключен к стробирующему входу блока 1 и стробирующему входу блока 4. Выходы формирователя 3, поступающие на второй блок обработки, на схеме не показаны. По этим связям подаются стрюбирующие синхроимпульсы, обеспечивающие переработку данных вторым блоком обработки. У блока доступа к информационным первому и второму входам подключены входы устройства. Выходы блока 4 являются соответствующими выходами устройства, поступающими на общий блок памяти. Блок управления (на фиг. 2) содержит первый 5 и второй б элементы И, первый 7 и второй 8 триггеры, инвертор 9 и элемент ИЛИ 10. Стробирующий вход блока является входом инвертора. ..выход которого подключен к второму входу второго триггера и первому вхо ду первого элемента И 5, второй вход которого объединен с первьам входом элемента И б и подключен к прямому выходу триггера 8. Этот выход является первьм выходом блока управления. Инверсный выход триггера 8 является вторым выходом блока, а первый-вход этого триггера подключен к первому триггеру, его выходу. Первый вход триггера 7 является первым входом обращения блока 1 и устройства в целом второй вход этого триггера подключен к шинам питания, а установочньлй вход к ВЫХОДУ элемента ИЛИ. Первый вход элемента ИЛИ 10 подключен к выходу первого элемента И 5, а второй вход элемента ИЛИ является установочным входом Уст. О. Стробирующий вход и второй вход обращения блока управ- ления являются соответственно входом инвертора и вторым входом второго эл мента И, выход которого является тре тьим выходом блока управления. Блок разрешения доступа, функциональная схема которого приведена на фиг. 3, содержит первый 11, второй 12, третий 13 и четвертый 14 элементы И, первый 15 и второй 16 элементы ИЛИ. Первый вход элемента 11 объединен с первым входом элемента 12 и яв ляется стробирующим входом блока. Выходы элементов 11 и 12 подключены к входам первого элемента ИЛИ 15, вы ход которого является выходом обраще ния блока. Первый вход элемента 13 объединен с вторым входом элемента 12 и является первым входом блока ра решения доступа. Первый вход элемента 14 является вторым входом блока. Выходы элементов 13 и 14 подключены к входс1м элемента ИЛИ 16, выход кото рого, второй вход -элемента 13 и второй вход элемента 14 являются соотве ственно информационным выходом, первь л и вторым информационньФ4И входами блока. Второй вход элемента 11 является входом обращения блока. Устройство работает следующим образом. В исходном состоянии по сигналу, поступающему на установочный вход бл ка управления (элемент ИЛИ 10),-триг геры 7 я 8 переходят в состояние, пр котором по сигналам с первого и второго выходов блока.управления блок 4 раэрешения доступа настраивается на пропуск к блоку памяти сигналов и ин формации блока обработки, подключенного к второму входу обращения СОб 2). Триггер 7 блока управления обнуляется и на выходах D-триггера появ ляются сигналы, разрешающие прохожде ние сигнала обращения и информации через элементы И 11 и 14 соответстве но. Если при этом в устройстве нет игналов на первом входе обращения С,Обр. 1) и есть сигналы Обр. 2} то они проходят без задержки. При этом второй блок обработки шлеет доступ к блоку памяти в каждом цикле. Выход элемента 6 (сигнал .) имеет нулевое значение и не влияет на работу формирователя, 3, вырабатывающего серию синхроимпульсов для второго блока обработки. Время задер . жки сигнала обращения Обр. 2 определяется временами задержки одного элемента И и одного элемента ИЛИ. В том случа, когда к памяти обращается первый блок обработки, сигнал Обр.1, поступающий асинхронно на блок управления, записывается на триггер 7 и по спаду стробирующего импульса, как это видно на временной диаграмме фиг. 4, переписывается в триггер 8. В следующем, после окончания сигнала Обр.2, такте на прямом выходе триггера 8 появляется единичный сигнал, устанавливающий через элементы 5 и 10 триггер 7 в нулевое состояние, а также разрешающий фондирование сигнала обращения через элементы И J.2 и ИЛИ 15 и прохождение информации через элементы И 13и ИЛИ 16 первого блока обработки данных, т.е. производится обслуживание по сигналу Обр. 1. Если во время обс.луживания сигнала Обр.1 появляется сигнал Обр. 2- , то второй блок обработки данных в связи с прекращением выработки для него формирователем синхроимпульсов переходит в режим ожидания окончания обслуживания сигнала Обр.1по сигналу Ост.2, формируемому элементом И 6 и поступающему на формирователь. По спаду стробирующего сигнала триггер 8 сбрасывается, что вызывает снятие сигнала останова формирователя на выходе элемента б и переключение блока разрешения доступа на связь со вторым блоком обработки. При поступлении очередного строба осуществляется обслуживание приостановленного сигнала Обр.2. Спад сигнала на прямом выходе триггера 8 сигнализирует также первому блоку обработки о завершении, его обслуживания. Предлагаемое техническое решение обеспечивает работу одного из блоков обработки с общим блоком при отсутствии конфликтов с минима.льной задержкой, что осебенно важно, когда частота обращений этого устройства преобладает над частотой обращений другого. В предлагаемом варианте задержка минимальна для второго устройства и ее величина определяется быстродействием одного элемента И и одного элемента ИЛИ. При использовании -существующей элементной базы это время соетавляет 10-20 не. Время задержки обслуживания первого блока обработки по сигналу Обр,2 определяется оуммой времен временем срабатывания триггера 7, временем от включения триггера 7 до спада стробиругацего импульса и временем срабатывания триггера 8. Минимальное время ожидания обслуживания сигналов Обр., при условии совпа дения момента включения триггера 7 я спада стробирующего импульса, составляет 100-120 НС, максимальное время определяется, в основном,частотой стробирующих импульсов.При совпадении обращений двух блоков обработки работа второго приостанавливается на один период следования синхроимпульсов. В известных устройствах задержки по обоим входам одинаковы и соответствуют задержке первого, более медленного, входа устройства. Таким образом, предлагаемое решение обеспечивает обслуживание по одному из входов практически без потерь времени, что особенно важно для вычис лительных систем, у которых один из блоков обработки, например, вычислительный процессор, имеет частоту обращений к памяти существенно выиге, чем второй, например, канал обмена с периферийными устройствами. Формула изобретения Устройство для сопряжения блоков обработки данных, содержащее формирователь стробирующих импульсов, блок управления, включающий элементы И, триггеры, элемент ИЛИ, и элемент НЕ, причем вход элемента НЕ подключен к выходу формирователя стробирующих импульсов, отличающееся тем, что, с целью повыгиения пропускной способности, оно содержит блок разрешения доступа и триггер, первый вход которого подключэн к входу синхронизации устройства и к первому входу формирователя стробирующих импульсов, второй вход которого соединен с выходом триггера, причем блок разрешения доступа содержит два элемента ИЛИ и четыре элемента И, первый вход первого и второго элементов И подключены к выходу формирователя стробирующих импульсов, а выходы - к вхоДу первого элемента ИЛИ, выход которого является выходом обращения устройства, выход элемента НЕ подключен к первому входу первого элемента И блока управления, выход которого подключен к первому входу элемента ИЛИ, второй вход которого соединен с установочным входом устройства, а выход - с установочным входом первого триггера, вход обращения которого соединен с первым входом обращения устройства, а выход - с первым входом второго триггера, второй вход которого подключен к выходу элемента НЕ, прямой выход - к второму входу первого элемента И и первому входу второго элемента И, второй вход которого соединен с вторым входом обращений устройства, выход второго элемента ИЛИ блока разрешения доступа соединен с информационным выходом устройства, а первый и второй входы - с выходами третьего и четвертого элементов И, второй вход второго элемента И и первый вход третьего элемента И подключены к прямому выходу второго триггера блока управления, первый вход четвертого элемента И подключен к .инверсному выходу второго триггера блока управления, а вторые входы третьего и четвертого элементов И подключены к первому и второму информационным входам устройства соответственно. Источники информации, принятые во внимание при экспертизе 1.Патент США 4153934, кл. G Об F 9/18, .опублик. 1979. 2.Авторское свидетельство СССР по заявке № 2671637/18-24, кл. G 06 F 13/04, 1978 (прототип).

r г

Cttnf

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления доступом к памяти для обмена массивами данных в многопроцессорной системе | 1989 |

|

SU1633418A1 |

| Устройство для обмена | 1978 |

|

SU798775A1 |

| Многопроцессорная система | 1988 |

|

SU1601614A1 |

| Устройство управления сегментированной памятью многопроцессорной системы | 1990 |

|

SU1753477A1 |

| Система для обмена данными между информационными процессорами | 1980 |

|

SU1001070A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство для регенерации динамической памяти | 1988 |

|

SU1534509A2 |

| Динамическое запоминающее устройство | 1987 |

|

SU1474739A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1987 |

|

SU1532937A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

,;

in

f ; f

.

7f/7 Pi/fc/

«-f

,09рГ

e

i Фt(Wl/

Pae.Z

ii:-ii ii

12

15

Ofy

ui

16

L

Г, -/

Tf.t

Авторы

Даты

1983-01-30—Публикация

1980-11-03—Подача