Изобретение относится к области вычислительной техники, в частности к построению информационно-измерительных систем, и может быть использовано при проектировании интеллектуальных крейт- контроллеров КАМАК.

Цель изобретения - повышение быстродействия с одновременным упрощением устройства.

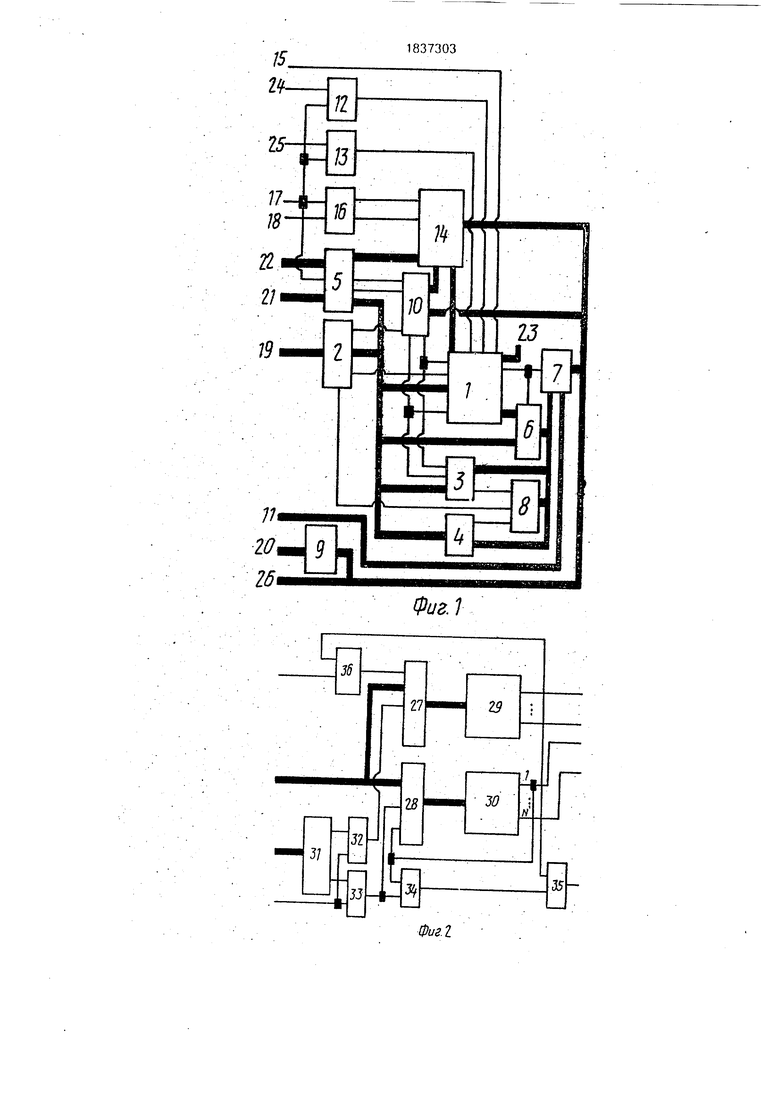

Блок-схема устройства представлена на фиг.1.

Устройство содержит блок управления обменом (микроконтроллер) 1, блок 2 обработки прерываний (БОП), оперативную память (ОЗУ) данных 3. (ПЗУ) постоянную память программ 4, регистрбданных, порты данных которых объединены с внутренней шиной данных и с первой группой входов регистра адреса 6, регистр команд 7 и дешифратор адреса 8, входы данных которых

объединены с внутренней шиной адреса и с адресными входами ОЗУ 3 и ПЗУ 4, дешифратор номера 9 и дешифратор команд 10, информационные входы которых объединены с второй группой выходов регистра команд 7, первая группа выходов которого соединена с шиной 11 команд периферийных устройств, первый 12 и второй 13 триггеры, выходы которых подключены соответственно к первому и второму статусным входам микроконтроллера 1, первая группа статусных выходов которого подключена к информационным входам формирователя 14 длины слова, а вторая группа статусных выходов - к шине 15 запрета периферийных устройств, и генератор цикла 16, вход которого подключен к управляющему выходу формирователя 14 длины слова данных, первый выход - объединен с шиной 17 первого синхроимпульса, второй выход 00

00

sl

со о со

с шиной 18 второго синхроимпульса периферийных устройств, а третий выход - с входом установки формирователя 14 длины слова данных, выходы данных которого подключены к входам управления регистра 5 данных, а входы выборки - к второй группе выходов регистра 7 команд, причем шина 19 запросов периферийных устройств подключена к информационным входам блока 2 обработки прерываний, шина 20 номера - к выходам дешифратора номера 9. шина 21 записи - к выходам данных, а шина 22 чтения - к входам данных регистра 5 данных, вход записи которого соединен с вторым, а вход чтения - с третьим выходом дешифра- тора команд 10, четвертый выход которого подключен к управляющему входу формирователя 14 длины слова данных, а первый выход - к входу записи блока 2 обработки прерываний, выход которого соединен с входом прерывания микроконтроллера 1, а вход чтения - с вторым выходом дешифратора 8 адреса, первый и третий выходы которого подключены к входам выборки соответственно ОЗУ 3 данных и ПЗУ4 про- грамм, при этом вход записи ОЗУ 3 соединен с вторым управляющим выходом микроконтроллера 1 и с первым входом управления дешифратора 10 команд, а вход чтения - с третьим управляющим выходом микроконтроллера 1 и с вторым входом управления дешифратора 10 команд, первый управляющий выход микроконтроллера 1 подключен к входу записи регистра 7 команд и к входу записи регистра 6 адреса, вторая группа входов которого подключена к порту адреса микроконтроллера 1, выход передатчика и вход приемника которого объединены с линией 23 последовательной связи с ЭВМ, причем шина 17 первого син- хроимпульса периферийных устройства соединена с тактовым входом регистра 5 данных, тактовым входом первого триггера 12, информационный вход которого подключен к шине 24 дешифрации команд периферийных устройств и тактовым входом второго триггера 13, информационный вход которого подключен к шине 25 ответа периферийных устройств, а шина 26 субадреса объединена с информационными вхо- дами дешифратора 9 номера, с второй группой выходов регистра 7 команд и с информационными входами дешифратора 10 команд.

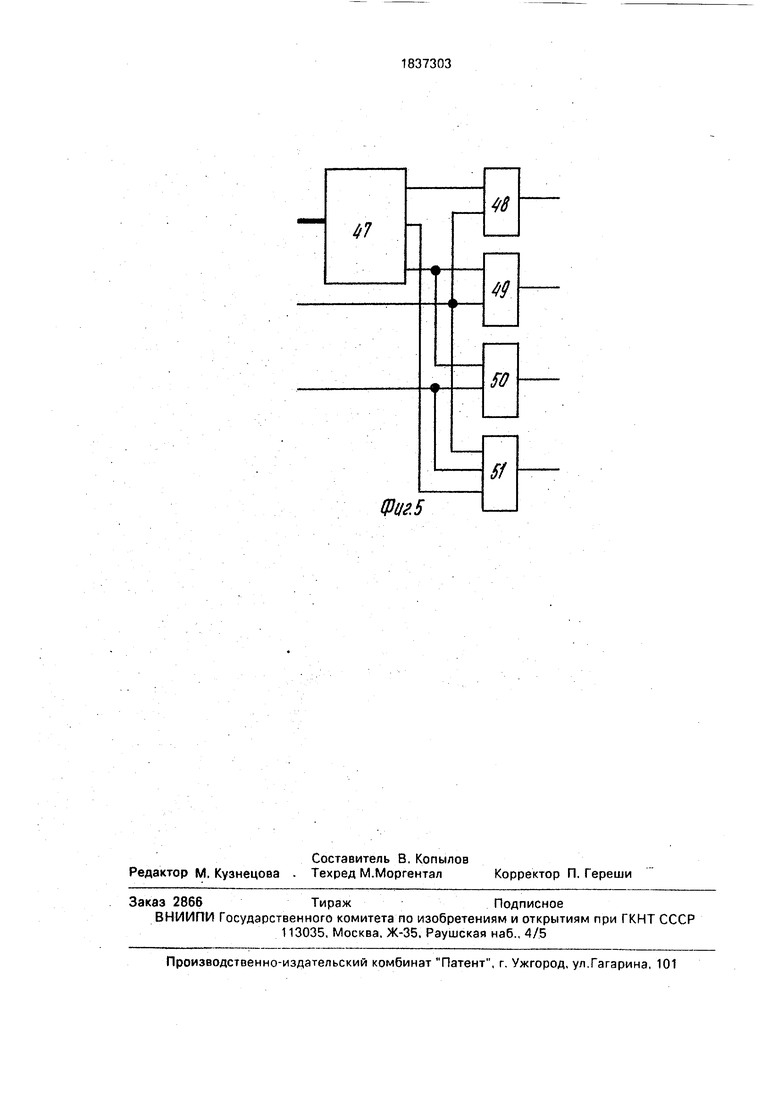

На фиг.2 представлена блок-схема фор- мирователя 14 длины слова данных. Он содержит первый 27 и второй 28 счетчики, установочные входы которых объединены с информационными входами формирователя 14, первый 29 и второй 30 дешифраторы,

входы которых подключены к выходам соответственно первого 27 и второго 28 счетчиков, третий 31 дешифратор, входы которого объединены с входами выборки формирователя 14, первую 32 и вторую 33 схемы И, первые входы которых подключены к управляющему входу формирователя 14, вторые входы - соответственно к первому и второму выходу третьего 31 дешифратора, а выходы - к счетному входу соответственно первого 27 и второго 28 счетчиков, третью 34 схему И, первый вход которой соединен с выходом второй 33 схемы И, схему ИЛИ 35, первый вход которой подключен к выходу третьей 34 схемы И. а выход - соединен с управляющим выходом формирователя 14, причем N выходов первого 29 и N выходов второго 30 дешифраторов составляют выходы данных формирователя 14, первый выход первого 29 дешифратора соединен с вторым входом схемы 35 ИЛИ и с первым входом четвертой схемы 36 И, первый выход второго 30 дешифратора - с вторым входом третьей 34 схемы И и с входом записи второго 28 счетчика, при этом вход записи первого 27 счетчика объединен с выходом четвертой схемы 36 И, второй вход которой подключен к входу установки формирователя 14.

На фиг.З представлена блок-схема регистра 5 данных. Регистр 5 данных содержит регистр 37 данных чтения N слов, регистр 38 данных записи N слов, демультиплексор 39 с N направлений, мультиплексор 40 на N направлений, схему И 41 и буфер 42, причем входы данных регистра 5 данных соединены с информационными входами регистра 37 данных чтения, N тактовых входов которого объединены с тактовым входом регистра 5 данных, выходы данных - с выходами буфера 42, информационные входы которого подключены к выходам регистра 38 данных записи N слов, входы управления - с входами управления демуль- типлексора 39 и мультиплексора 40 и с первыми входами схемы И 41, вторые входы которой объединены с входом записи регистра 5 данных, а выходы 1,.4 N подключены к N тактовым входам регистра 38 данных записи N слов, выходы демультиплексора 39 и информационные входы мультиплексора 40 объединены0с портом данных ре- гистра 5 данных, причем первый выход схемы И 41 подключен к входу управления буфера 42, выходы регистра 37 данных чтения N слов соединены с информационными входами демультиплексора 39, стробирую- щий вход которого подключен к входу чтения регистра 5 данных, а выходы мультиплексора 40 - с информационными

иходами регистра 38 данных записи N ;лов.

На фиг.А показана блок-схема генерато- )а 16 цикла. Он содержит RS-триггер 43, 5ход установки которого соединен с входом енератора 16 цикла, а выход - с входом 1апрета генератора 44 тактовых импульсов 1 с входом сброса счетчика 45, счетный вход соторого подключен к выходу генератора 44 тактовых импульсов, и дешифратор 46, пер- зый, второй и третий выходы которого явля- отся соответственно первым, вторым и третьим выходами генератора 16 цикла, а четвертый выход соединен с входом сброса RS-триггера 43, причем информационные входы дешифратора 46 объединены с выходами счетчика 45.

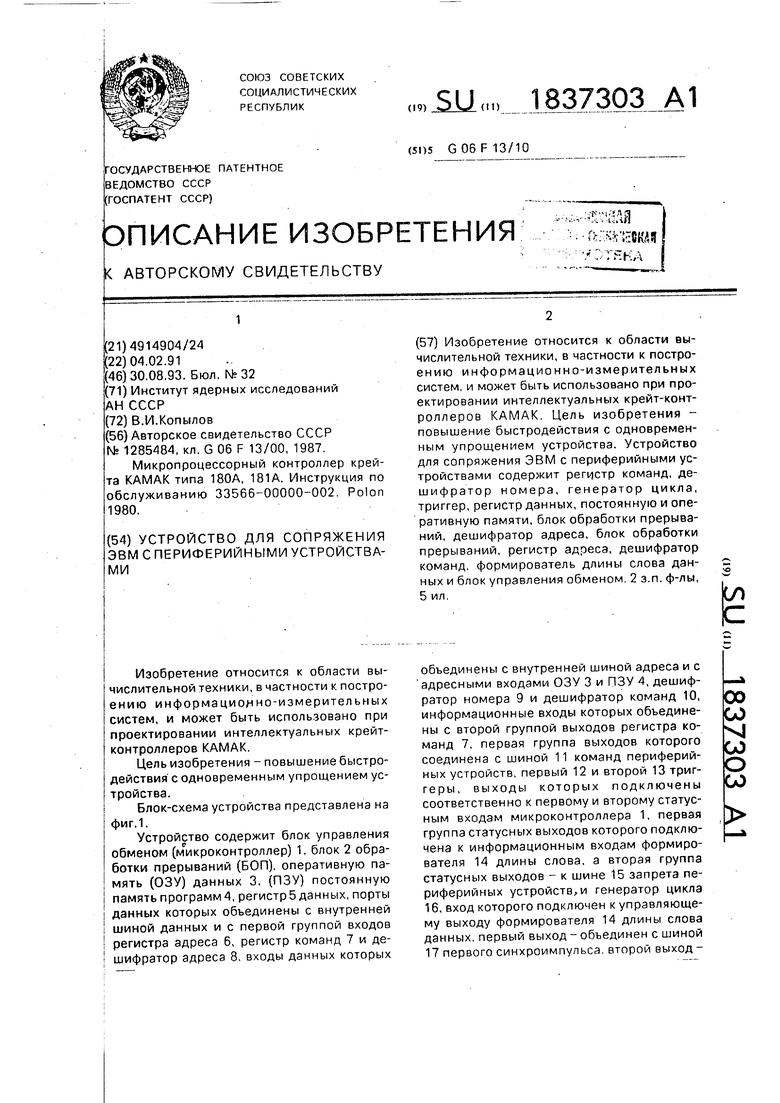

На фиг.5 представлена блок-схема дешифратора 10 команд. Он содержит дешифратор 47, информационные входы которого объединены с информационными входами дешифратора 10 команд, первую 48, вторую 49, третью 50 и четвертую 51 схемы И, выходы которых являются соответственно первым, вторым, третьим и четвертым выходами дешифратора 10 команд, причем его первый вход управления соединен с первым входом первой 48 схемы И, с первым входом второй 49 схемы. И и с первым входом четвертой 51 схемы И, вторые входи которых подключены соответственно к первому, второму и третьему выходам дешифратора 48, а второй - с первым входом третьей 50 схемы И и с третьим входом четвертой 51 схемы И.

Формирователь 14 длины слова данных работает следующим образом. На информационные входы формирователя подается цифровой код, соответствующий разрядности слов данных, с которыми устройство должно оперировать на шинах 22 чтения и 21 записи периферийных устройств. При этом минимальная разрядность слова данных составляет М бит, что соответствует разрядности данных микроконтроллера 1, а максимальная - MxN бит, что соответствует разрядности данных периферийных устройств.

Рассмотрим функционирование формирователя 14 при выполнении устройством операций передачи данных на шину 21 записи периферийных устройств. Цифровой код К {1... N}, установленный на информационных входах формирователя 14, поступает на установочные входы первого 27 счетчика и переписывается в него, соответственно появляясь на его выходах по заднему фронту импульса на входе установки формирователя 14, подключенном к второму входу четвертой схемы И. В исходном

состоянии-на первом входе четвертой 36 схемы И присутствует сигнал низкого уровня с первого выхода первого 29 дешифратора, разрешающий прохождение импульса с

второго входа схемы И на ее выход и, соответственно, на вход записи первого 27 счетчика. Код К с выходов первого 27 счетчика поступает на информационные входы первого 29 дешифратора и на его К-ом выходе

0 .появляется сигнал низкого уровня, передаваемый на соответствующий выход управления формирователя 14. Третий 31 дешифратор, информационные входы которого объединены с входами выборки форми5 рователя 14, осущестэляет дешифрацию команд, код которых поступает на эти входы выборки, причем сигнал высокого уровня на его первом выходе формируется, если дешифрируемая команда является командой

0 записи данных, а на втором,-если командой чтения данных.

Сигнал с первого выхода третьего 31 дешифратора поступает на второй вход первой 32 схемы И, на первый вход которой

5 подаются импульсы высокого уровня с управляющего входа формирователя 14. Эти импульсы стробируют сигнал с первого выхода третьего 31 дешифратора и на выходе первой 32 схемы И и, соответственно, на

0 счетном входе первого 27 счетчика формируются результирующие импульсы, передним фронтом каждого из которых первый 27 счетчик уменьшает на единицу свое содержимое, что приводит к соответствующе5 му изменению кода на информационных входах первого 29 дешифратора. При этом на его соответствующих выходах от К-го до первого появляются сигналы низкого уровня, поступающие на соответствующие выхо0 ды управления формирователя 14.

Сигнал низкого уровня, появляющийся на первом выходе первого 29 дешифратора, поступает на первый вход четвертой 36 схемы И и разрешает прохождение на ее выход

5 импульса с входа установки формирователя 14, задним фронтом которого первый 27 счетчик вновь устанавливается в К-е состояние и снимает сигнал низкого уровня на первом выходе первого 29 дешифратора.

0 Кроме того, сигнал с первого выхода первого 29 дешифратора проходит на выход схемы 35 ИЛИ и далее на управляющий выход формирователя 14.

Рассмотрим функционирование форми5 рователя 14 при выполнении устройством операций приема данных с шины 22 чтения периферийных устройств. Цифровой код К (1...-N), установленный на информационных входах формирователя 14. поступает на установочные входы второго 28

счетчика и переписывается в него, соответственно появляясь на выходах второго 28 счетчика по заднему фронту импульса на его входе записи, который формируется на первом выходе второго 30 дешифратора.

В исходном состоянии счетчик 28 установлен в К-ое состояние, на его выходах и, соответственно, на информационных входах второго 30 дешифратора присутствует цифровой код К, которому соответствует наличие сигнала низкого уровня на К-м выходе второго 30 дешифратора, а второй 28 счетчик удерживается в режиме счета импульсов, т.к. запись в счетчик 28 цифрового кода с информационных входов формирователя 14 осуществляется лишь по заднему фронту импульса с первого входа второго 30 дешифратора.

Если дешифрируемая третьим 31 дешифратором команда является командой чтения данных, то на втором выходе этого дешифратора формируется сигнал высокого уровня, поступающий на второй вход второй 33 схемы И и разрешающий прохождение на выход этой схемы импульсов высокого уровня с управляющего входа формирователя 14. При этом на выходе второй 33 схемы И и, соответственно, на счетном входе второго 28 счетчика, появляются импульсы, передним фронтом каждого из которых этот счетчик уменьшает на единицу свое содержимое, что приводит к соответствующему изменению кода на информацион- ных входах второго 30 дешифратора. В результате на соответствующих выходах второго 30 дешифратора от К-го до первого появляются сигналы низкого уровня, поступающие на соответствующие выходы управления формирователя 14. Задним фронтом сигнала низкого уровня, появляющегося на первом выходе второго 30 дешифратора, код К с установочных входов переписывается во второй 28 счетчик и этот счетчик вновь устанавливается в К-ое состояние, что, в свою очередь, приводит к переходу сигнала на первом выходе второго 30 дешифратора из низ.кого в высокий уровень. Кроме того, сигнал низкого уровня с первого выхода второго 30 дешифратора разрешает прохождение импульса с выхода второй 33 схемы И на выход третьей 34 схемы И и далее на выход схемы ИЛИ 35, подключенный к управляющему выходу формирователя 14.

Таким образом, однажды записанный в первый 27 и второй 28 счетчики код длины слова данных автоматически перезаписывается в эти счетчики каждый раз, когда очередная команда чтения или записи данных орерирует с последним М-битным словом

данных и в этот момент формируется импульс на управляющем выходе формирователя 14, причем та или иная операция с очередным М-битным словом данных сопро- вождается соответствующим изменением кода на выходах управления формирователя 14.

Регистр 5 данных работает следующим образом. Данные из периферийных уст0 ройств по шине 22 чтения поступают на входы данных регистра 5 данных, объединенные с информационными входами регистра 37 данных чтения N слов и переписываются в него импульсом с шины 17 первого синхро5 импульса, подключенной к тактовому входу регистра 5 данных, объединяющему N тактовых входов регистра 37 данных чтения N слов, с выхода которого N слов параллельно поступают на информационные входы де0 мультиплексора 39 с N направлений, осуществляющего переключение на свой выход и, соответственно, в порт данных регистра 5 данных разрядностью М бит одного из N входов, причем управление переключением

5 осуществляется под управлением цифрового кода, передаваемого с входов управления регистра 5 данных на входы управления де- мультиплексора 39, выходы которого стро- бируются импульсом, поступающим на

0 стробирующий вход демультиплексорэ 39 с входа чтения регистра 5 данных.

Данные с порта данных разрядностью М бит регистра 5. которые должны быть переданы в виде слова данных разрядностью

5 MxN бит на шину 21 записи данных периферийных устройств, поступают на информационные входы мультиплексора 40 на N направлений, с выходов разрядностью М бит которого они передаются на одну из N

0 групп М-битных информационных входов регистра 38 данных записи N слов, выбор которых осуществляется под управлением цифрового кода, поступающего с входов управления регистра 5 данных на входы управ5 ления мультиплексора 40. Запись этих данных в регистр 38 данных записи N слов осуществляется импульсами с соответствующих выходов 1... N схемы И 41, на первые входы которой поступает цифровой код с

0 входов управления регистра 5 данных, а на вторые N входов, объединенные с входом записи регистра 5 данных ,- импульсы записи. Слово данных разрядностью NxM бит, сформированное таким образом на выходах

5 регистра 38 данных записи N слов, поступает на информационные входы буфера 42, выходы которого объединены с выходами данных регистра 5 данных, а стробирующий вход подключен к первому выходу схемы И 41. Таким образом, слово данных будет передано на шину 21 записи периферийных стройств с выхода буфера 42 лишь когда лово данных разрядностью NxM бит будет |полностью сформировано в регистре 38 энных записи.

Генератор 16 цикла работает следующим образом. На его вход поступают импульсы, передаваемые далее на вход установки RS-триггера 43. каждым из которых триггер 43 устанавливается и на его выходе формируется сигнал высокого уровня, поступающий на вход запрета генератора 44 тактовых импульсов и разрешающий генерацию импульсов на его выходе. Тактовые импульсы с выхода генератора 44 поступают на счетный вход счетчика 45, причем каждым импульсом счетчик увеличивает на единицу цифровой код на своих выходах, передаваемый на информационные входы дешифратора 46, причем на соответствующих выходах дешифратора 46 формируются сигналы низкого уровня, первые три из которых поступают соответственно на первый, второй и третий выходы генератора 16 цикла, а четвертый - на вход сброса RS-триггера 43, Этим сигналом триггер 43 сбрасывается и на его выходе формируется сигнал низкого уровня, запрещающий генерацию генератором 44 тактовых импульсов и сбрасывающий счетчик 45 в исходное состояние, когда на его выходах присутствует нулевой код и соответственно на всех выходах дешифратора 46 формируются сигналы высокого уровня. Таким образом, каждый импульс, поступающий на вход генератора 16 цикла, приводит к формированию на его первом, втором и третьем выходах определенной последовательности импульсов низкого уровня.

Дешифратор 10 команд работает следующим образом. Цифровой код, приходящий на информационные входы дешифратора 47, преобразуется на соответствующих выходах дешифратора 47 в сигналы низкого уровня, стробируемые импульсами на первом либо втором входах управления дешифратора 10 команд и при этом, соответственно, на выходах первой 48, второй 49, третьей 50 либо четвертой 51 схем И формируются импульсы, появляющиеся, соответственно, на первом, втором, третьем либо четвертом выходах дешифратора 10 команд.

Ниже рассматривается алгоритм функ- I ционирования заявляемого устройства. | После инициализации микроконтрол- I лер 1 начинает выборку команд из ПЗУ 4 команд, для чего в каждом цикле сначала выставляет на своих выходах порта адреса код старшей части адреса, на выходах порта

данных - код младшей части адреса, затем результирующий код адреса запоминается в регистре 6 адреса по переднему фронту импульса записи с первого управляющего

выхода порта управления микроконтроллера 1, после чего этот код адреса поступает через внутреннюю шину адреса на адресные входы ПЗУ 4 программ и входы данных дешифратора 8 адреса, на третьем выходе

0 которого формируется импульс, поступающий на вход выборки ПЗУ А, по которому содержимое соответствующей ячейки передается на выходы порта данных ПЗУ 4 и далее через двунаправленную внутреннюю

5 шину данных на входы порта данных микроконтроллера 1.

В ходе исполнения программы начальной установки, хранящейся в ПЗУ 4 программ, микроконтроллер 1 программирует

0 БОП 2 и устанавливает режим работы встроенного приемопередатчика, выход передатчика и вход приемника которого подключены к линии 23 последовательной связи с удаленной ЭВМ.

5Программирование БОП 2 заключается

в программной установке статуса уровней приоритетов запросов, поступающих на входы БОП 2 с шины 19 запросов периферийных устройств, маскировании этих запросов, оп0 ределении способа формирования сигнала прерывания на выходе БОП 2, поступающего на вход прерывания микроконтроллера 1, и выполняется следующим образом.

Адрес БОП 2. сформированный микро5 контроллером 1 способом, описанным выше, на выходах регистра 6 адреса, поступает на входы данных регистра 7 команд и запоминается в нем по заднему фронту импульса с первого управляющего выхода порта уп0 равления микроконтроллера 1.

На второй группе выходов регистра 7 команд выделяются коды команд обработки данных, а также субадресов, поступающих на шину 26 субадреса, и номеров, через

5 дешифратор 9 номера поступающих на шину 20 номера периферийных устройств, в то время как на первой группе выходов этого регистра формируются коды как команд обработки данных, так и статусных

0 команд.

Коды команд обработки данных с второй группы выходов регистра 7 команд и, в частности, команда записи данных в БОП 2 поступают на информационные входы де5 шифратора 10 команд, при этом на первом выходе дешифратора 10 команд по этой команде формируется импульс записи данных в БОП 2, выставляемых в этот момент микроконтроллером 1 на внутренней шине данных.

Запрограммированный соответствующим образом БОП 2 готов к обработке запросов, поступающих с шины 19 запросов периферийных устройств на его информационные входы, заключающейся в формировании на выходе БОП 2 сигнала запроса на прерывания, поступающего на вход прерывания микроконтроллера 1 и вызывающего переход микроконтроллера 1 к выполнению подпрограммы обслуживания прерывания, в ходе чего БОП 2 под управлением импульса на его входе чтения передает через внутреннюю шину данных в порт данных микроконтроллера 1 код номера соответствующего запроса на шине 19 запросов периферийных устройств.

При этом импульс на входе чтения БОП 2 образуется на втором выходе дешифратора 8 адреса в соответствии с кодом адреса, сформированного микроконтроллером 1 на внутренней шине адреса как это было описано выше.

Программирование встроенного в микроконтроллер 1 последовательного приемопередатчика заключается в установке формата посылки и скорости обмена по линии 23 связи, соответствующих принятым для удаленной ЭВМ, с которой осуществляется обмен данными.

После окончания программирования БОП 2 и встроенного приемопередатчика микроконтроллер 1 через последовательный передатчик посылает по линии 23 связи в удаленную ЭВМ последовательность кодовых слов, информирующих удаленную ЭВМ о готовности устройства к организации обмена данными между этой ЭВМ и периферийными устройствами, после чего микроконтроллер 1 переходит в режим приема информации из линии 23 связи с удаленной ЭВМ, ожидая прихода данных во встроенный приемник.

Удаленная ЭВМ, получив заранее заданную последовательность кодовых слов, посылает в устройство через линию 23 связи массив данных, представляющих собой программу взаимодействия устройства с периферийными устройствами.

Считывая передаваемые ЭВМ данные с встроенного приемника, микроконтроллер 1 пословно записывает их в ОЗУ 3 данных, формируя, как это было показано выше, адреса соответствующих ячеек ОЗУ 3 на внутренней шине адреса, подключенной к адресным входам ОЗУ 3. При этом на первом выходе дешифратора 8 адреса формируется импульс выборки ОЗУ 3, а собственно запись данных в ОЗУ 3 осуществляется из микроконтроллера 1 по внутренней шине данных под управлением

импульсов записи, поступающих с второго выхода порта управления микроконтроллера 1 на вход записи ОЗУ 3.

По окончании записи в ОЗУ 3 всего мас- 5 сива данных, переданных из ЭВМ в микроконтроллер 1, ЭВМ переходит в режим ожидания приема данных от периферийных устройств, а микроконтроллер 1 начинает выборку команд из ОЗУ 3, формируя, как это

0 было показано выше, адреса ячеек и импульсы выборки ОЗУ 3, причем передача информации из ОЗУ 3 на внутреннюю шину данных осуществляется под управлением импульсов с третьего выхода порта управле5 ния микроконтроллера 1.

В ходе исполнения программы микроконтроллер 1 может выполнить одну из следующих операций: чтение данных с шины 22 чтения; запись данных на шину 21 записи;

0 чтение статусной информации; установка статусной информации; связь с удаленной ЭВМ.

Первые две операции сопровождаются предварительной установкой формировате5 ля 14 длины слова данных и кодов на шинах 11 команд, номера 20, субадреса 26, а также запуском генератора 16 цикла, причем исполнение команд периферийными устройствами контролируется микроконтроллером

0 1 по состоянию первого 12 и второго 13 триггеров, выходные сигналы которых передаются соответственно на первый и второй статусный входы микроконтроллера 1.

Начальная установка формирователя 14

5 длины слова данных осуществляется переписью в него через информационные входы данных с первой группы статусных выходов микроконтроллера 1, в результате чего в формирователе 14 устанавливается код дли0 ны слова данных К (1... N}.

Если микроконтроллер 1 должен выполнить операцию чтения или записи данных с шины 22 чтения или, соответственно, на шину 21 записи периферийных устройств, он

5 через регистр 6 адреса формирует адрес на внутренней шине адреса, который переписывается в регистр 7 команд, как это было показано выше. При этом код данных с второй группы выходов регистра команд 7 по0 ступает на шину 26 субадреса, через дешифратор 9 номера - на шину 20 номера, на информационные входы дешифратора 10 кома.нд и на входы выборки формирователя 14 длины слова, а с первой группы

5 выходов - на шину 11 команд периферийных устройств.

В результате дешифрации данных, поступивших на его информационные входы, дешифратор 10 команд формирует импульсы на втором и третьем выходах соответстИЛИ

импульсов

венно для команд записи и чтения данных и на четвертом выходе - импульс записи статусной информации в формирователь 14 длинь слова, причем этот импульс формируется в дешифраторе 10 команд автоматически п и дешифрации команды записи либо чтения данных.

выполнении команды чтения дан- шины 22 чтения периферийных уст- в импульс с четвертого выхода рзтора 10 команд проходит на управой вход формирователя 14 длины сло- Далее через третью 34 схему И и схему на управляющий выход формиро- 14, своим задним фронтом уменьшая шицу содержимое второго 28 счетчи- HN пульс с управляющего выхода форми- еля 14 длины слова запускает 16 цикла, который вырабатывает первом, втором и третьем выходах поступающие соответственно на 17 первого, шину 18 второго синхро- периферийных устройств и на установки формирователя 14. Первым пульсом, поступающим на такто- регистра 5 данных, слово данных NxM бит целиком переписы- с шин 22 чтения в регистр 37 данных N слов. Одновременно на выходах формирователя 14 формируется код слова данных, поступающий на вхо- демультиплексора 39 с N на- который подключает на свои К-ю группу, выходов регистра 37 чтения. Теперь при поступлении на чтения регистра 5 данных импульса с выхода дешифратора 10 команд с выходов демультиплексора 39 этим импульсом и поступают порт данных регистра 5 данных и да- внутреннюю шину данных в-порт микроконтроллера 1. Таким обра- EJ микроконтроллер 1 будет принято К-е бит|ное слово, тогда как всего необходимо К М-битных слов, что и составляет операцию чтения данных микрокон- ром 1 с шины 22 чтения периферий- у тройств.

результате выполнения следующей чтения микроконтроллер 1 считает регистра 37 данных чтения (К-1)-е М-бит- с ов и т.д. до тех пор, пока не будет первое М-битное слово. При этом и раз на третьем выходе дешифрато- оманд будет формироваться импульс, на вход чтения регистра 5 , на, выходах управления формирова- 4 длцны слова - последовательно, от уменьшающиеся коды, переключаю- емультиплексор 39 на соответствуюп и команды

При ных с ройс деши ляющ ва, и 35

вател на ед ка. рова генерётор на свс их импульсы шину импу; вход } син: вый разрядностью ваетс чтени t даннь х Кдлииы ды управления, правлений выхо; ы даннь х вход треть го данные строб -фуются через лее

данных зом, Мприн5|тьполную тролл ных

в

команды

из

ное

счита о

каждь

раЮ

поступающий

данных

теля

К до 1

щие

щую группу выходов регистра 37 данных чтения, на четвертом выходе дешифратора 10 команд- импульс, через вторую 33 схему И попадающий на счетный вход второго 28

счетчика и уменьшающий каждый раз на единицу его содержимое, причем на управляющем выходе формирователя 14 импульсы формироваться не будут, т.к. на первом выходе второго 30 дешифратора присутст0 вует сигнал высокого уровня, запрещающий прохождение этих импульсов на выход третьей 34 схемы И, и генератор 16 цикла запускаться не будет.

Когда микроконтроллером 1 будет под5 ана команда чтения, по которой в него будет считано первое М-битное слово данных и, таким образом, передано с шин 22 чтения все слово КхМ бит, задним фронтом импульса с четвертого выхода дешифратора 10 ко0 манд, прошедшего через вторую 33 схему И, второй 28 счетчик будет установлен в нулевое состояние и на первом выходе второго 30 дешифратора появится сигнал низкого уровня, фронтом которого второй 28 счетчик

5 будет вновь установлен в К-е состояние.

Теперь при выполнении новой операции чтения данных нет необходимости начальной установки длины слова данных иначе как только тогда, когда требуется из0 менить длину слова данных. Однако установка той или иной длины слова данных зависит от разрядности слова данных периферийного устройства, имеющего максимальную разрядность среди всех пери5 ферийных устройств, сопряжение которых с удаленной ЭВМ осуществляет предлагаемое устройство, и должна производиться один раз после инициализации микроконтроллера 1.

0При выполнении команд записи данных

из микроконтроллера 1 на шину 21 записи периферийных устройств по каждой команде записи импульс с четвертого выхода дешифратора 10 команд проходит на управ5 ляющий вход формирователя 14 длины слова и далее через первую 32 схему И - на счетный вход первого 27 счетчика, своим задним фронтом уменьшая каждый раз на единицу его содержимое, первоначально

0 равное К. Цифровой код от К до 1 с выходов первого 27 счетчика поступает на информационные входы первого 29 дешифратора, на выходах которого от К до 1 формируются импульсы, поступающие на выходы данных

5 формирователя 14 длины слова и далее на входы управления мультиплексора 40 на N направлений, на информационные входы которого последовательно поступают К М- битных слов с порта данных микроконтроллера 1, а также на первые входы схемы И 41,

на вторые входы которой поступают импульсы с второго выхода дешифратора 10 команд. При этом на соответствующих выходах от К-го до первого схемы 1/1.41 формируются импульсы, поступающие на соот- ветствующие тактовые входы регистра 38 данных записи N слов, по которым в этом регистре формируется КхМ-битное слово данных, поступающее на информационные входы буфера 42 и стробируемое импульсом с первого выхода схемы И 41. С выходов буфера 42 стробированные данные поступают через выходы данных регистра 5 данных на шину 21 записи периферийных устройств. Одновременно с этим первый 26 счетчик переходит в нулевое состояние, соответственно на первом выходе первого 29 дешифратора появляется сигнал низкого уровня, разрешающий прохождение импульса с входа установки формирователя 14 длины слова на выход четвертой схемы И 36. Сигнал с первого выхода первого 29 дешифратора через схему ИЛИ 35 поступает на управляющий выход формирователя 14 и далее на вход генератора 16 цикла, запуская его, как это было описано выше. Генератор 16 цикла формирует сигнал на шине 17 первого синхроимпульса, на шине 18 второго синхроимпульса и на входе установки формирователя 14, причем первый 27 счетчик в формирователе 14 будет вновь установлен в К-ое состояние, чем будет завершена полная операция записи данных из микроконтроллера 1 на шину 21 записи периферийных устройств.

В ходе исполнения операций чтения или записи данных микроконтроллер 1 может контролировать состояние шины 24 дешифрации команд и шины 25 ответа периферийных устройств. Сигналы с ука- занных шин поступают на информационные входы соответственно первого 12 и второго 13 триггеров и их состояние запоминается в этих триггерах по импульсу с шины.17 первого синхроимпульса. Выходные сигналы триггеров могут быть считаны соответственно на первый и второй статусные входы микроконтроллера 1. При этом сигнал низкого уровня на выходе первого 12 триггера показывает, что поданная микроконтроллером

Iкоманда, определяемая кодами на шине

IIкоманд, шине 20 номера и шине 26 субадреса, не выполнена выбранным периферийным устройством, что говорите неисправности этого устройства, о чем микроконтроллер должен сообщить удаленной ЭВМ, а сигнал низкого уровня на выходе второго 13 триггера, - что в результате исполнения поданной микроконтроллером

1 команды выбранное периферийное устройство выполнило заранее обусловленную операцию.

Микроконтроллер 1 может установить данные на второй группе своих статусных выходов, приводя тем самым в определенное состояние шину 15 запрета, чем достигается запрещение или разрешение выполнения заранее обусловленных операций одновременно всеми периферийными устройствами.

При необходимости обмена данными с удаленной ЭВМ микроконтроллер 1 приступает к выполнению заданного протокола обмена по последовательной линии 23 связи через встроенный приемопередатчик.

Формула изобретения 1. Устройство для сопряжения ЭВМ с периферийными устройствами, содержащее регистр команд, первая группа выходов которого соединена с шиной команд периферийных устройств, дешифратор номера, выходы которого соединены с шиной номера периферийных устройств, генератор цикла, первый выход которого подключен к шине первого синхроимпульса, а второй выход - к шине второго синхроимпульса периферийных устройств, первый и второй триггеры, тактовые входы которых подключены к шине первого синхроимпульса, причем информационный вход первого триггера соединен с шиной дешифрации команд, а второго - с шиной ответа периферийных устройств, регистр данных, информационные входы и выходы которого соединены соответственно с шиной чтения и шиной записи периферийных устройств, постоянную память программ, оперативную память данных и блок обработки прерываний, порты данных которых объединены с внутренней шиной данных и с портом данных регистра данных, и дешифратор адреса, первый выход которого соединен с входом чтения блока обработки прерываний, отличающееся тем, что, с целью повышения быстродействия в режиме обмена данными с одновременным аппаратным упрощением, в него введены регистр адреса, дешифратор команд, формирователь длины слова данных и блок управления обменом, порт данных которого и первая группа входов данных регистра адреса объединены с внутренней шиной данных, порт адреса блока управления обменом соединен с второй группой входов данных регистра адреса, выходы которого подключены к внутренней шине адреса устройства, объединяющей входы данных регистра команд, дешифратора адреса и адресные входы оперативной памяти данных и постоянной памяти

ходы

дами

памя

ных,

равл

запи

команд, при этом второй и третий вы- цешифратора адреса соединены с вхо- выборки соответственно постоянной и команд и оперативной памяти дан- тервый управляющий выход блока уп- зния обменом соединен с входом

:и регистра адреса и входом записи регистра команд, вторая группа выходов которого подключена к информационным входам дешифратора номера, шине субадреса периферийных устройств, входам выборки формирователя длины слова данных и к информационным входам дешифратора команд, первый вход управления которого соединен с входом записи оперативной па- мяти данных и с вторым управляющим выходом блока управления обменом, третий упраиляющий выход которого подключен к Bxoflv чтения оперативной памяти данных и

к второму входу управления дешифратора команд, первый выход которого соединен с входэм записи блока обработки прерываний, выход которого подключен к входу пре- рывгния блока управления обменом, а инфс рмационные входы объединены с шиной о апросов периферийных устройств, шина гервого синхроимпульса которых подключена к тактовому входу регистра данных, вход записи и вход чтения которого соединены соответственно с вторым и третьим выходами дешифратора команд, четвертый выход которого подключен к управляющему входу формирователя длины слова данных, информационные входы которого соединены с первой группой статусных

выходов блока управления обменом, выхсды данных - с входами.управления ре- гист за данных, управляющий выход - с входом генератора цикла, а вход установки - с третьим выходом генератора цикла, причем вторая группа статусных выходов блока уп- равгения обменом соединена с шиной запрета периферийных устройств, его первый и второй статусные входы - с выходами соответственно первого и второго триггеров. а выход передачи и вход приема данных соединены с последовательной линией связи. ;

Ј. Устройство поп.1,отличающее- с я |тем, что формирователь длины слова данных содержит первый и второй счетчики, установленные входы которых являются информационными входами формирователя, тервый и второй дешифраторы, входы которых подключены к выходам соответст- венно первого и второго счетчиков, третий дешифратор, входы которого являются вхо5

10 15

0

5

0

5

0 5

0 5

дами выборки формирователя, первый и второй элементы И, первые входы которых объединены и являются управляющим входом формирователя, вторые входы первого и второго элементов И подключены соответственно к первому и второму выходам третьего дешифратора, а выходы - к счетному входу соответственно первого и второго счетчиков, третий элемент И, первый вход которого соединен с выходом второго элемента И, элемент ИЛИ, первый вход которого подключен к выходу третьего элемента И, а выход является управляющим выходом формирователя, при этом группы выходов первого и второго дешифраторов образуют выходы данных формирователя, причем первый выход группы выходов первого дешифратора соединен с вторым входом элемента ИЛИ и с первым входом четвертого элемента И, первый выход группы выходов второго дешифратора соединен с вторым входом третьего элемента И и с входом записи второго счетчика, вход записи первого счетчика соединен с выходом четвертого элемента И, второй вход которого подключен к входу установки формирователя.

3. Устройство по п. г, о т л и ч а ю щ е е- с я тем, что регистр данных содержит регистр чтения данных, регистр данных записи, демультиплексор, мультиплексор, группу элементов И и буфер, причем входы данных регистра соединены с информационными входами регистра данных чтения, тактовые входы которого являются тактовым входом регистра, выходы данных регистра соединены с выходами буфера, информационные входы которого подключены к выходам регистра данных записи, входы управления регистра соединены с входами управления демультиплексора и мультиплексора и с первой группой входов элементов И группы, вторая группа входов которых является входом записи регистра, а выходы подключены соответственно к тактовым входам регистра данных записи, выходы демультиплексора и информационные входы мультиплексора объединены и являются портом данных регистра, причем выход первого элемента И группы подключен к входу управления буфера, выходы регистра данных чтения соединены с информаци- онными входами демультиплексора, стробирующий вход которого является входом чтения регистра, выходы мультиплексора соединены с информационными входами регистра данных записи.

1837303

| название | год | авторы | номер документа |

|---|---|---|---|

| Распределенная система управления | 1989 |

|

SU1732345A1 |

| Устройство обмена информацией | 1987 |

|

SU1532941A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Многоканальное устройство управления шаговым двигателем | 1990 |

|

SU1789970A1 |

| Устройство для формирования прерывания при отладке программ | 1985 |

|

SU1305680A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с периферийными устройствами | 1985 |

|

SU1285484A1 |

| Устройство для контроля цифровых узлов | 1990 |

|

SU1756894A1 |

Изобретение относится к области вычислительной техники, в частности к построению информационно-измерительных систем, и может быть использовано при проектировании интеллектуальных крейт-конт- роллеров КАМАК. Цель изобретения - повышение быстродействия с одновременным упрощением устройства. Устройство для сопряжения ЭВМ с периферийными устройствами содержит регистр команд, дешифратор номера, генератор цикла, триггер, регистр данных, постоянную и оперативную памяти, блок обработки прерываний, дешифратор адреса, блок обработки прерываний, регистр адреса, дешифратор команд, формирователь длины слова данных и блок управления обменом. 2 з.п. ф-лы, 5 ил.

Фиг. Т

фие.4

фиг.З

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с периферийными устройствами | 1985 |

|

SU1285484A1 |

| Насос | 1917 |

|

SU13A1 |

| Переносный кухонный очаг | 1919 |

|

SU180A1 |

| Ключ-жезл при блокировке для отправления на перегон рабочих поездов при закрытом выходном семафоре и толкачей при открытом выходном семафоре | 1930 |

|

SU33566A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1993-08-30—Публикация

1991-02-04—Подача