ограничения на взаимное расположение и длительность сигналов в управляюще и информационнь1х каналах связи. С другой стороны, необходимость увеличения длительности сигнала в управляющем канале связи уменьшает быстродействие устройства, что приводит к увеличению времени передачи информации, а это, в свою очередь, - к снижению помехоустойчивости и надежности работы устройства.

Наиболее близким по технической сущности к данному устройству является устройство для передачи информации , содержащее два триггера, пять элементов И, элемент НЕ, два информационных входа, блок управления, две шины синхроимпульсов 2.

Недостатком этого устройства является низкая помехоустойчивость, поскольку в нем не обеспечена защита от помех различной полярности. В связи с этим, поступление помехи низкого уровня и, соответственно, появление разрешающего сигнала на выходе элемента НЕ в момент поступлени полезных сигналов на информационные входы устройства, приводит к формированию ложного сигнала на выходе устройства. Кроме того, длительность полезного сигнала на информационных входах устройства должна превышать длительность периода следования синхронизирующих сигналов на выходах блока управления, поскольку синхронизирующим сигналом с выхода блока управления осуществляется опрос информационных входов устройства, что требует обязательного совпадения во времени указанных сигналов. Это в свою очередь, ограничивает быстродействие устройства, что приводит к увеличению времени передачи информации и к снижению надежности работы устройства.

Цель изобретения - повышение, помехоустойчивости и надежности работы- устройства.

Поставленная цель достигается тем что в устройство, содержащее блок управления, первый выход которого соединен через первый элемент И с первым нулевым входом первого триггера, второй триггер, единичный и первый нулевой входы которого соединены соответственно с выходами второго и третьего элементов И, четвертый и пятый элементы И, первые входы которых соединены соответственно с первым и вторьа информационными входами устройства и элемент НЕ, введены пять триггеров, пят1 элементов И, з1лемент равнозначности и буферный блок, выходы которого являются группой информационных выходов устройства, причем единичный выход второго триггера непосредственно соединен со вторым входом первого элемента И, через, шестой элемент И - с выходом

сигнала ошибки устройства, а через седьмой элемент И - с первым входом блока управления, нулевой выход второго триггера соединен с первым входом BocbMqro элемента И, выходом соединенного с единичным входом первог триггера, единичны выход которого соединен с первым входом второго элемента И, а нулевой выход - с первым входом третьего элемента И, выход четвертого элемента И соединен с единичным входом третьего триггера и со вторым входом второго элемента И, третий вход которого соединен с выходом пятого элемента И и с единичным входом четвертого триггера, входы девятого элемента И соединены соответственно с единичньом выходом третьего триггера и нулевым выходом четвертого триггера, а выход - с информационным входом буферного блока входы элемента равнозначности соединены соответственно с единичными и нулевыми выходами третьего и четвертого триггеров, а выход - непосредственно со вторым входом седьмого элемента И и через элемент НЕ - со вторым входом шестого элемента И, первый вход десятого элемента И соединен с первым управляющим входом устройства, а выход - с четвертым входом второго элемента И и единичным входом пятого триггера, выход которого соединен со вторым входом восьмого элемента И, второй вход блока управления соединен с первой входной шиной синхроимпульсов и с третьим входом восьмого элемента И, четвертый вход которого соединен с выходом шестого триггера, пятый вход второго элемента И соединен со второй шиной синхроимпульсов и с третьим входом блока управления, первый вход которого соединен с первым управляющим входом буферного блока, второй выход - со вторым входом третьего элемент И, с единичным входом шестого триггера и со вторым управляющим входом буферного блока, третий выход - с первыми нулевыми входами третьего, четвертого, пятого и шестого триггеров, четвертый выход - с нулевым входом седьмого триггера, пятый выход - с третьим управляющим входом буферного блока, а шестой выход - с первым единичным входом седьмого триггера, единичный выход которого соединен со вторыми входами четвертого, пятого и десятого элементов И, второй единичный вхо седьмого триггера соединен со вторьм нулевыми входг1ми первого шестого триггеров, со входами установки в состояние О блока управления и буферного блока и со вторым управляющим входом устройства.

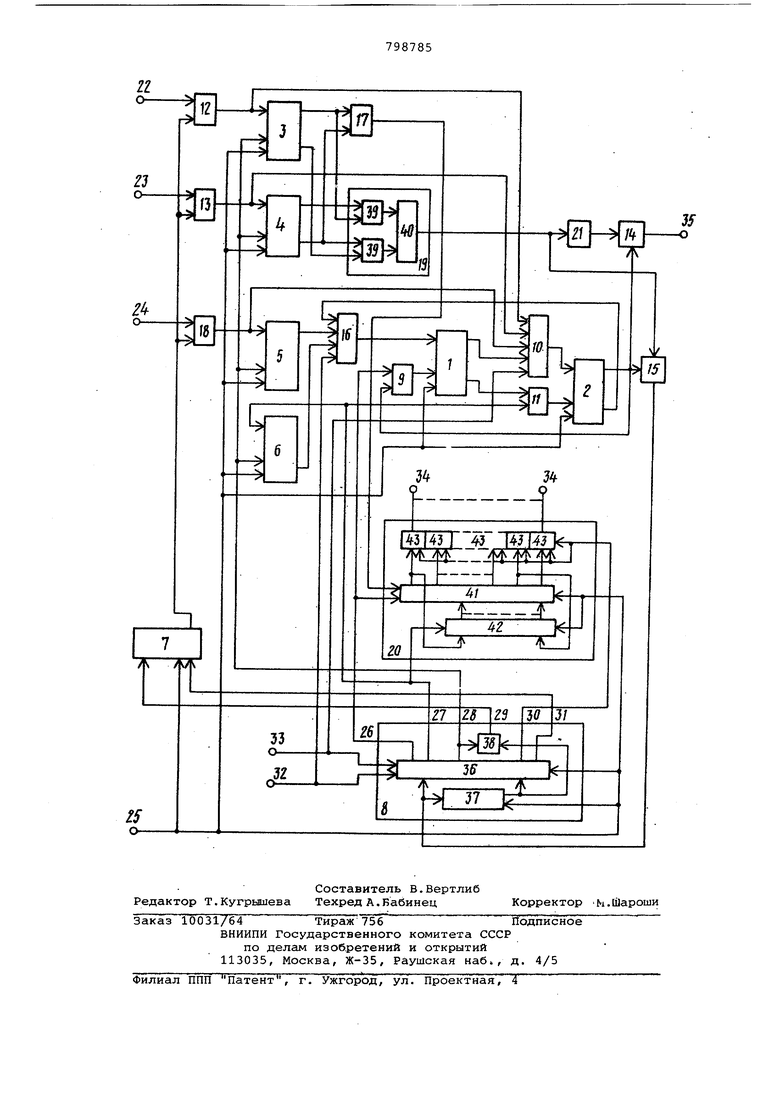

При этом блок управления содержит элемент И, регистр сдвига, первый, 65 второй и третий входы которого явля ются соответственно первым, вторьом третьим входами блока, а выходы - с ответственно первым, вторым, третьим пятым и шестым выходами блока, счет чик числа символов, первым входом соединенный с первым входом блока, вторым входом - с четвертым входом регистра сдвига и входом установки в состояние О блока, а выходом с пятым входом регистра сдвига и пер вым входом элемента И, второй вход и выход которого соединены соответственно с третьим и четверым выходами блока. Кроме того, буферный блок содержит два регистра и группу элементов И, выходы которых являются вующими выходами блока, а первые входы соединены с выходами соответст вующих разрядов первого регистра, пе вый и второй входы которого соединены соответственно с информационным и первым управляющим входами блока выходы соответствующих разрядов - с группой входов второго регистра,груп па входов - с группой выходов второго регистра, первым входом соединенного со вторым управляющим входом блока, а вторым входом - с третьим входом первого регистра и входом установки в состояние О блока. На чертеже представлена блок-схе ма устройства. Устройство для выьода информации содержит триггеры 1-7, блок 8 управления, элементы И 9-18, элемент 19 равнозначности, буферный выходной блок 20, элемент НЕ 21, первый 22 и второй 23 информационные входы устро ства , первый 24 и второй 25 управляющие входы устройства, выходы 2631блока В управления, входные шины 32и 33 синхроимпульсов, информационный выход 34 устройства, выход 35 сигнала ошибки устройства. Блок 8 управления содержит регист 36 сдвига, счетчик 37 числа символов и элемент И 38. Элемент 19 равнознач ности содержит элементы И 39 и элемент ИЛИ 40. Выходной блок 20 содержит регистры 41, 42 и элементы И 43 группы, число которых равно числу разрядов в регистре 41. Устройство работает следующим образом. В исходном состоянии все триггеры устройства, которые могут быть выполнены, например, в базисе элементо И-ИЛИ-НЕ, находятся в состоянии О. Перед начётом передачи информации на вход 25 устройства поступает сигнал сброса, который устанавливает в состояние 1 триггер 7, подтверждает состояние триггеров 1-6 блока 8, выходного блока 20 и, тем самым, подготавливает элементы И 12, 13, 18 к прохождению сигналов. После этого на вход 22 поступает сигнал, соответствующий коду 1 передаваемогг сигнала информации. В случае передачи кода О информационный сигнал поступает соответственно только на вход 23. Одновременно с сигналом, поступающим на первый или второй информационные входы устройства, на вход 24 поступает тактирующий сигнал, сопровождающий каждый символ передаваемой информации. С поступлением кода 1 в передаваемом символе информации триггеры 3 и 5 устанавливаются в состояние 1, при этом формируется сигнал на выходе элемента И 17, поскольку оба его входа оказываются подготовленными. Сигнал с выхода элемента И 17 поступает на информационный вход выходного блока 20 и далее на выход регистра 41. Регистры 41, 42 предназначены для преобразования поступающего последовательного кода в параллельный, а элементы И 43 - для передачи параллельного кода на выходы 34 к какому-либо внешнему абоненту, например запоминающему устройству. При установке триггера 5 в состояние 1 элемент И 16 оказывается полностью подготовленным, поскольку тритеры 2 и б находятся в состоянии О и сигналами с их нулевых выходов подготовлены соответствующие входы элемента И 16. Очередной синхроимпульс, поступающий на шину 32 сдвинутый относительно синхроимпульса, поступающего на шину 33, на половину периода следования, проходит через элемент И 16 на единичный вход триггера 1 и устанавливает его в состояние 1. Сигналы с его единичного выхода подготавливают элемент И 10, через который поступление сигналов с шины 33 начинается только после спада заднего фронта тактирующего сигнала, поступающего на вход 24, и заднего фронта информационного сигнала, поступающего на вход 22. После спада заднего фронта указанных сигналов, на выходах элементов И 12 и 18 появляется разрешающий сигнал и, тем самым, подготавливается элемент И 10 через который очередной синхроимпульс с шины 33 проходит на единичный вход триггера 2. Если при поступлении сигнала на вход 22 на входе 23 отсутствует ложный сигнал, то триггеры 3, 4 находятся в противоположных состояниях. В связи с тем, что входы одного из элементов И 39 элемента 19 равнозначности соединены с нулевыми выходами триггеров 3, 4, а входы другого элемента И 39 - с единичными выходами тех же триггеров, то при противоположных состояниях триггеров 3 и 4 сигнал на выходе элемента 19 равнозначности становится разрешающим для элемента И 15. Поскольку элемент И 15 подготовлен, сигнал с единичного выхода триггера 2 проходит на первый вход блока 8, а на выход 35 сигнала ошибки через элемент И 14 не проходит, так как последний закрыт эапрешающим сигналом с выхода элемента НЕ 21. С порогового выхода блока 8 сигнал поступает соответственно на вход регистра 36 сдвига, после чего начинается формирование сигналов на его выходах и соответственно на выходах 26, 27, 28 блока 8. Одновременно с выхода элемента И 15 сигнал поступает на вход счетчика 37, предназначенного для фиксации момента окончания заданного количества сиволов информации. Сигнал на выходе 26 блока 8, формируемый синхронно с синхроимпульсом на шине 32, поступает на первый вход элемента И 9 и проходит на первый нулевой вход триггера 1, поскольку элемент И 9 подготовлен сигналом с единично1о выхода триггера 2. При установке триггера 1 в состояние О, подготавливается элемент И 11, и второй сигнал, формируемый на выходе 27 блока 8 синхронно с синхроимпульсом на шине 33, проходит через элемент И 11 на первый нулевой вход триггера 2 для установки его в исходное состояние. Одновременно с установкой триггера 2 в состояние О сигналов с выхода 27 блока 8 осуществляется установка в состояние 1 триггера б, сигнал с нулевого выхода которого закрывает элемент И 16. В связи с этим, исключается повторная установка в состояние 1 триггера 1, а следовательно, и повторный запуск блока 8, в случае если к этому моменту времени сигнал на входе 25 еще присутствует. Кроме того, сигналы с выходов 26, 27 поступают на управляющие входы выходного блока 20 и далее на входы регистров 41, 42 для преобразования кода.

Преобразование кода в выходном блоке 20 осуществляется следующим образом.

При поступлении сигнала с выхода 26 в первый разряд регистра 41 вносится код, поступающий на информационный вход выходного блока 20 с выхода элемента И 17, а со второго по М-ый разряд - код из регистра 42, который имеет на один разряд меньше, чем регистр 41. При поступлении сигнала с выхода 27 в первый разряд регистра 42 вносится код из первого разряда регистра 41, а в М-ый разряд регистра 42 - код из М-1-го разряда регистра 41. Сигналом, формируемым на выходе 28, осуществляется установка триггеров 3-6 в состояние О тем самым, завершается цикл приема одного символа информации. Задержка формирования сигнала на выходе 28 блока 8 выбирается таким образом, чтобы сброс триггеров 3-6 происходил после окончания переходных процессов

которые возможны при спаде заднего фронта входных сигналов из-за влияния линии связи, подключаемой к информационным входам 22, 23 и к управляющему входу 24 устройства. Тем сас мым исключается влияние помех, формируемых при спаде заднего фронта входных сигналов на работоспособность устройства.

Функционирование узлов устройства

при передаче кода О осуществляется аналогично, при этом входные сигналы поступают на входы 23 и 24 устройства, а затем - соответственно на входы триггеров 4 и 5. Сигнал с единичного выхода триггера 5 через элемент

5 И 16 осуществляет установку в состо,-яние 1 триггера 1, сигнал с единичного выхода которого, в свою очередь. приводит к установке в состояние 1 -триггера 2 и запуску блока 8 управления. На выходах 26-28 блока 8 снова начинается формирование очередной группы синхронизирующих сигналов, и цикл работы устройства повторяется. После приема группы символов информации, например, соответствующей управляющему или информационному слову, передаваемому из ЦВМ, на выходе счетчика 37 формируется сигнал, разрешающий формирование группы сигналов на выходах 29, 30, 31 блока 8.

Сигнал, формируемый на выходе 29 синхронно с сигналом на выходе 28, устанавливает в состояние О триггер 7 и, тем самым, запрещает поступление сигналов на единичные входы триггеров 3, 4 и 5 со входов 22, 23 и

24 устройства соответственно. Второй сигнал, .формируемый на выходе 30, осуществляет передачу кода из регистра 41 через элементы И 43 на выход

0 34, а третий сигнал с выхода 31 осуществляет установку триггера 7 в состояние 1 для подготовки устройства к приему следующей группы символов входной информации.

5 в случае, если в момент поступления импульса на вход 22 поступает сигнал помехи на вход 23, то оба триггера 3 и 4 оказываются в состоянии 1, в результате чего на выхоQ де элемента 19 равнозначности формируется сигнал, который запрещает поступление сигнала с единичного выхода триггера 2 через элемент И 15 на запуск блока 8. Тем же сигналом

- с выхода элемента 19 равнозначности поступающим на вход элемента НЕ 21, разрешается поступление сигнала с единичного выхода триггера 2 через элемент И 14 на выход 35. Сигнал ошибки используется, например, для

0 построения передачи. В этом случае на вход 25 поступает сигнал сброса, к.оторый устанавливает в состояние 1 триггер 7 и подтверждает состояние О всех остальных узлов устройства. Затем начинается цикл передачи информации, как было описано выше.

Если сигнал помехи формируется на входе 24 устройства при отсутствии сигналов на входах 22 и 23, то оба триггера 3 и 4 остаются в состоянии О, и на выходе элемента 19 равнозначности также формируется запрещающий сигнал, что, в свою очередь , приводит к формированию сигнала на выходе 35 сигнала ошибки. При одновременном воздействии сигналов помех на входы 22, 23 и 24 передача на выходы 34 устройства ложного кода также исключена. В этом случае на выходе 35 формируется сигнал и запрещается запуск блока 8. Если же возможно появление сигнала помехи в момент формирования сигналов на входах 22, 23, которая приводит, например, к кратковременному пропаданию полезных сигналов, то в этом случае также исключается поступление ложной информации на выходы 34, поскольку сигнал с выхода 28 осуществляет установку в состояние О триггеров 35 с задержкой после спада заднего фронта входных сигналов. Момент формирования сигнала на выходе 28 в данном случае выбирается с учетом длительности входных сигналов и длительности переходных процессов, возможных после спада заднего фронта входных сигналов, поскольку запуск блока 8 может произойти в момент кратковременного спада полезных сигналов.

Таким образом, устройство по сравнению с известным позволяет исключит передачу на выходы устройства ложной информации при поступлении на информационные входы и на управляющий вход устройства сигналов помех любой полярности, что возможно, например, при одновременном воздействии сильных электромагнитных полей, на линии связи, подключаемых ко входам устройства. Это достигается путем обнаружения поступления на входы устройства ошибочной информации в промежутках времени между моментами передачи символов одной и той же группы. Кроме того, в промежутке времени, равном длительности формирования полезных сигналов на входах устройства, а также в промежутке вре мени после спада заднего фронта входных сигналов до момента сброса входных триггеров 3-5 и в промежутке между моментами передачи двух соседних групп символов информации достигается полное исключение поступления на входы триггеров 3-5 сигналов помех. Тем самым повышается помехоустойчивость, а следовательно, и надежность работы устройства.

Предлагаемое устройство обладает также более широкими функциональными возможностями, поскольку оно предназначено для передачи как числоимпульсНого, так и любого другого кода, например позиционного.

Кроме того, в связи с тем, что запуск основных узлов формирования информации триггера 2, блока 8 упрэв5 ления и выходного устройства 20 осуществляется после спада задних фронтов входных сигналов, устройство не критично к длительности входных сигналов . Тем самым расширяются функциональные возможности устройства, а также его быстродействие что, в свою очередь, увеличивает помехоустойчивость и надежность работы устройства за- счет возможности сокращее ния времени приема информации.

Формула изобретения

1. Устройство для вывода информации, содержаш.ее блок управления, первый выход которого соединен через первый элемент И с первым нулевым входом первого триггера, второй триггер, единичный и первый нулевой

5 входы которого соединены соответственно с выходами второго и третьего элементов И, четвертый и пятый элементы И, первые входы которых соединены соответственно с первым и вторым

0 информациояными входами устройства и элемент НЕ, отличающее с я тем, что, с целью повышения помехоустойчивости устройства, в него введены пять триггеров, пять элес ментов И, элемент равнозначности и буферный блок, выходы которого являются группой информационных выходов устройства, причем единичный выход второго триггера непосредственно соединен со вторым входом первого

0 элемента И, через шестой элемент

И - с выходом сигнала ошибки устройства, а через седьмой элемент И с первьал входом блока управления, нулевой выход второго триггера соединен с первым входом восьмого элемента И, -выходом соединенного с единичным входом первого триггера, единичный выход которого соединен с первым входом второго элемента И, а нуQ левой выход - с первым входом третьего элемента И, выход четвертого элемента И соединен с единичным входом третьего триггера и со вторым входом второго элемента и, третий вход которого соединен с выходом пя5того элемента И и с единичным входом четвертого триггера входы девятого элемента И соединены соответственно с единичным выходом третьего триггера и нулевым выходом четвертого триггера, а выход - с информационным входом буферного блока, входы элемента равнозначности соединены .соответственно с единичными и нулевыми выходами третьего и четвертого триггеров,

5 а выход - непосредственно со вторым

входом седьмого элемента И и через элемент НЕ - со вторым входом шестого элемента И, первый вход десятого элемента И соединен с первым управляющим входом устройства, а выход с четвертым входом второго элемента И и единичным входом пятого триггера, выход которого соединен со вторым входом восьмого элемента И, второй вход блока управления соединен с первой входной шиной синхроимпульсов и с третьим входом восьмого элемента И, четвертый вход которого соединен с выходом шестого триггера, пятый вход второго элемента И соединен со второй шиной синхроимпульсов и с третьим входом блока управления первый вход которого соединен с первым управляющим входом буферного блока, второй выход - со вторым входом третьего буферного элемента И, с единичным входом шестого триггера и со вторым управляющим входом буферного блока, третий выход - с первым нулевыми входами третьего, четвертого, пятого и шестого триггеров, четвертый выход - с нулевым входом седьмого триггера, пятый выход - с третьим управляющим входом буферного блока, а шестой выход - с первым единичным входом седьмого триггера, единичный выход которого соединен со вторыми входами четвертого, пятого и десятого элементов И, второй единичный вход седьмого триггера соединен со вторыми нулевыми входами первого шестого триггеров, со входами установки в состояние О блока управления и буферного блока и со вторым управляющим входом устройства.

2. Устройство по п. 1, отличающееся тем, что блок управления содержит элемент И, регистр сдвига, первый, второй и третий входы которого являются соответственно первым, вторым и третьим входами блока, а выходы т соответственно первым, вторым, третьим, пятым и шестым входами блока, счетчик числа символов, первым входом соединенный с первым входом блока, вторым входом с четвертым входом регистра сдвига и входом установки в состояние О блока, а выходом - с пятым входом регистра сдвига и первым входом элемента И, второй вход и выход которого соединены соответственно с третьим и четвертым выходами блока.

3. Устройство по п. 1, отличающееся тем, что буферный блок содержит два регистра и группу элементов И, выходы которых являются соответствующими выходами блока, а первые входы соединены с выходами соответствующих разрядов первого регистра, первый и второй входы которого соединены соответственно с информационным и первым управляющим входами блока, выходы соответствую цих разрядов - с группой ьходов второго регистра, группа входов - с группой выходов второго регистра, первым входом соединенного со вторым управляющим входом блока, а вторым входом - с третьим входом первого регистра и входом установки в состояние О блока.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 414585... кл. G 06 F 3/04, 1971.

2. Авторское свидетельство СССР № 306554, кл. Н 03 К 3/28, 1969 (про4Q тотип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации сигналов | 1977 |

|

SU669347A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1981 |

|

SU1012234A1 |

| Канал обмена многомашинного комплекса | 1984 |

|

SU1236492A1 |

| Устройство для вычисления модуля комплексного числа | 1989 |

|

SU1693599A1 |

| Многоканальная микропрограммная управляющая система | 1985 |

|

SU1280628A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1444770A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Многопроцессорная система | 1989 |

|

SU1741144A1 |

| Устройство для сдвига информации | 1985 |

|

SU1291962A1 |

Авторы

Даты

1981-01-23—Публикация

1979-04-23—Подача