.28 }27

О

3 00 О1 43 чС

Изобретение относится к вычислительной технике и может Выть использовано в с легализированных вычислителях.

Цель изобретения - повышение достоверности за счет возможности работы в режиме самоконтроля операционной части устройства.

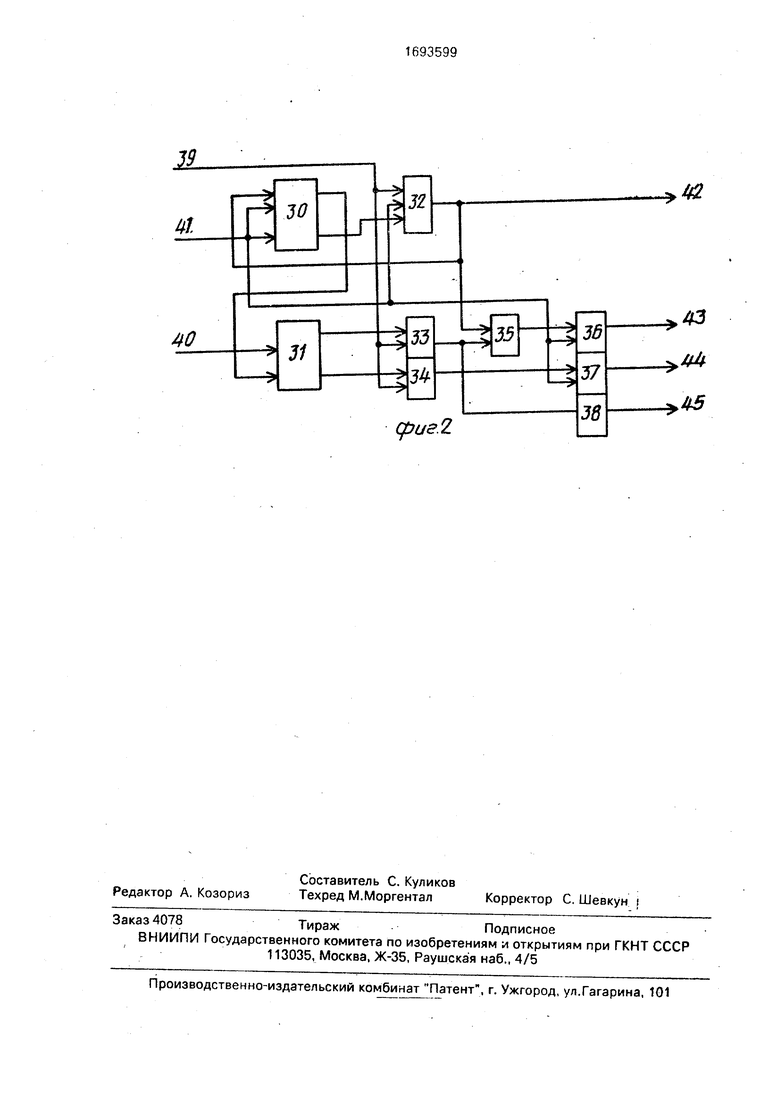

На фиг. 1 представлена функциональная схема устройства; на фиг, 2 - функциональная схема блока управления.

Устройство содержит элементы НЕ 1 и 2, блок 3 управления, три1 геры 4 и 5, коммутаторы 6 и 7, триггеры 8 и 9, первый 10 и второй 11 регистры аргумента, коммутаторы 12 и 13, буферный регистр 14, коммутатор 15, сумматоры 16 - 18, схему 19 сравнения, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 20, триггер 21, коммутатор 22, входы 23 и 24 соответственно первого и второго аргументов, тактовый вход 25 вход 26 разрешения самоконтроля, выход 27 результата, выход- 28 признака неисправности, выход 29 признака самоконтроля.

Блок управления содержит триггеры 30 и 31, элементы И-НЕ 32 и 33, элемент И 34, элементы И-НЕ 35-37, элемент НЕ 38, вход 39, тактовый вход 0 управления циклом самоконтроля, вход 41 разрешения само контроля, тактовые выходы42 -45с первого по четвертый.

Устройство функционирует следующим образом,

В режиме Работа в I-M т акте по переднему фронту синхроимпульсов в перзый 10 и второй 11 регистры аргументов заносятся n-разрядные мантиссы прямых кодов оот- Еютственно действительной и мнимой т составляющих комплексного -мела, л в буферный регистр 14 - значение модуля комплексного числа, составляющие которого поданы в i-1-м такте. С выхода первого регистра 10 аргумента прямой код действительной составляющей поступает на входы первого 16 и второго 17 сумматоров, а л-2 старших разряда этого кода - на вход третьего сумматора 18. С анхода второго регистра 11 аргумента инверсный код мнимой составляющей поступает на второй вход иторого сумматора 17, прямой код- на второй вход третьего сумматора 18, а п-2 старших разрядов этого кода - на второй вход первого сумматора 16. На выходах-первого 16 и третьего 18 сумматоров реализуются соответственно функции 1

I RE I +

Iml

1

I Im I +-J I RE |.

На втором сумматоре 17 вычисляется разность кодов реальной к мнимой составляющих. Если эта разность положительная, то на выход первого коммутатора 22 проходит результат с выхода первого сумматора 16, в противном случае на выход ком иутатора 22 проходит результат с выхода ч ретьего сумматора 18. Таким образом, в буферный регистр 14 заносится п+1 -разряд код модуля комплексного числа как результат сложения большей составляющей комплексного числа

0 с меньшей составляющей, сдвинутой на два разряда в сторону младших разрядов. В режиме Рабо и результат с выхода третьего регистра пос гупает на выход 27 результата устройства.

5 Для проведения самоконтроля устройства на вход 26 разрешения самоконтроля подается сигнал Лог. Г, Единичный сигнал с выхода второго триггера 4 разрешает работу всех триггеров, разблокирует элемен0 ты И-НЕ 32, И-НЕ 37 блока управления, разрешает прохождение через второй 6 и третий 7 коммутаторы информации с выхода шестого коммутатора 15. На выходах 42 -45 блока 3 управления под действием синхро5 импульсов вырабатываются серии импульсов. Под воздействием отрицательных импульсов с выходов 42-44 происходит установка в единичное состояние всех разрядов буферного регистра 14, первого 10 и

0 второго 11 регистров аргументов. Установка буферного регистра 14 происходит один раз за весь цикл самоконтроля по первому синхроимпульсу, прошедшему на устройство после установки в единичное состояние вто5 рого триггера 4.

Установка первого регистра 10 аргумента происходи с по всем нечетным синхроимпульсам, а установка второго регистра 11 аргумента - по первому и всем четным син0 хроимпульсам. По первому синхроимпульсу происходит установка в единичное состояние также четвертого 5 и первого 9 триггеров. Единичное значение с выхода триггера 9 пропускает на вход первого сумматора 16

5 и вход третьего сумматора 18 значение Лог. 1 соответственно с выходов пятого коммутатора 12 и шестого коммутатора 13, а также инвертирует на элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 20 значение знакового разряда

0 второго сумматора 17.

Цикл самоконтроля разбивается на два этапа. На первом этапе, поскольку значение знакового разряда второго сумматора 17 инвертируется, при RE Im на вход первого

5 коммутатора 22 будет проходить сумма с выхода третьего сумматора 18, а при RE т - с выхода первого сумматора 16. Таким образом, в буферный регистр 14 заносится результат сложения меньшей составляющей комплексного числа с большей

составляющей, сдвинутой на два разряда в сторону младших разрядов (лри этом два старших разряда дополняются единицами). При поочередном занесении в первый 10 и второй 11 регистры аргумента максималь- ных чисел соответственно во второй 11 и первый 10 регистры поочередно заносятся п младших разрядов кода модуля с. выхода буферного регистра 14.

Результат на выходе буферного оегист- ра 14 в двух соседних тактах, начиная с второго, одинаков. На схеме 19 сравнения происходит сравнение значений модуля предыдущего и последующего тактов, и результат сравнения во всех нечетных тактах, начиная с третьего, фиксируется на пятом триггере 21. При несовпадении значений модуля пятый триггер 21 устанавливается в единичное состояние, что является сигналом неисправности устройства. Единичный сигнал с выхода неисправности устройства 28 запрещает прохождение синхроимпульсов на тактовый вход 25.

В 32-м такте (в общем случае - в такте 2n+1) в старшем п+1-м разряде буферного ре- гистра 14 появляется значение Лог. О. Все триггеры переключаются по фронту, поэтому четвертый триггер 5, являющийся Т-триг- гером, в 32-м такте переключается в нулевое состояние. Нулевое значение с выхода чет- вертого триггера 5 переключает четвертый коммутатор 15, и на его выход начинает поступать код, старшие n-2-разряда которого являются n-2-младшими разрядами кода с выхода коммутатора, а два младших раз- ряда принимают значение Лог, 0. Поэтому, начиная с 33-го такта (в общем случае - с такта 2п+1+1), в первый 30 и второй 11 регистры будет по очереди заноситься код с модуля с выхода буферного регистра 14, сдвинутый на два разряда в сторону старших разрядов.

В 33-м такте первый триггер 9 переходит в нулевое состояние, и начинается второй этап цикла самоконтроля, на котором пятый 12, шестой 13 и первый 22 коммутаторы, первый 16, второй 17 и третий 18 сумматоры и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 20 функционируют, как в режиме Работа. В цикле самоконтроля в качестве большей составляющей выступает максимальное число (2п-1), а в качестве меньшей составляющей - код, получаемый на выходах вычитающего счетчика.

Таким образом, на первом этапе проис- ходит контроль первого входа первого сумматора 16 и второго выхода третьего сумматора 19 по всем 2П возможным значениям, а на втором этапе происходит контроль второго входа первого сумматора 16 и

первого входа третьего сумматора 18 по всем 2П возможным значениям.

В 41-м такте (в общем случае - в (2пМ ь 2П 1)-м такте происходит последнее сравнение цикла самоконтроля, При нормальной работе устройства в 40-м такте четвертый триггер 5 устанавливается в единичное состояние, а в 42-м такте по фронту на выходе буферного регистра 14 в единичное состояние устанавливается третий триггер 8. Единичное состояние на выходе 29 сброса режима самоконтроля свидетельствует об окончании цикла самоконтроля и eeflef к снятию сигнала Лог. 1й на выходе 26 разрешения самоконтроля устройства. С установлением первого триггера 4 в нулевое состояние устройство переходит в режим Работа.

В режиме Работа блок управления блокирован сигналом Лог. О на входе 41 разрешения самоконтроля. В режиме самоконтроля при поступлении сигнала Лог. 1 на вход 41 первый синхроимпульс с входа 39 проходит через элемент И-НЕ 32 на выход 42 и на первый вход второго элемента 2И-ИЕ 35, что ведет к выработке импульса на выходе 43. Поскольку триггер 31 находится в нулевом состоянии (открыт элемент 2И 34), по первому синхроимпульсу также вырабатывается сигнал на выходе 44. По окончании первого синхроимпульса по фронту, получаемому на выходе элемента 32, триггер 30 переключается в единичное состояние, и нулевое значение с инверсного выхода триггера 30 блокирует дальнейшее прохождение синхроимпульсов на вход 42. Сигнал Лог. 1 с выхода триггера 30, поступающий на вход установки в нулевое состо- яние триггера 31, разрешает рабо ту триггера 31. Триггер 31 является Т-тригге- ром, и при поступлении фронтов с входа управления циклом самоконтроля, начиная с второго, происходит переключение этого триггера из нулевого состояния в единичное и наоборот. При этом поочередно открываются элемент И-НЕ 33 и элемент И 34, поочередно пропуская синхроимпульсы на выходы 43 и 44. Происходит выработка также синхроимпульса на выход 45. По окончании режима самоконтроля сигнал Лог. О на входе 41 вновь блокирует блок управления.

Формула изобретения Устройство для вычисления модуля комплексного числа, содержащее два регистра аргументов, три сумматора и первый коммутатор, причем n-разрядкый выход первого регистра аргумента соединен с п-разрядны- ми входами первых слагаемых первого и второго сумматоров, выходы п-2 старших

разрядов первого регистра аргумента соединены с п-2 младшими разрядами входа первого слагаемого третьего сумматора, п- разрядные прямой и инверсный выходы второго регистра аргумента соединены с входами вторых слагаемых соответственно фетьего я второго сумматоров, выходы п-2 старших разрядов прямого выхода второго регистра аргумента соединены с п-2 младшими разрядами входа второго слагаемого первого сумматора, выходы первого и третьего сумматоров соединены соответственно с первым и вторым информационными входами первого коммутатора, отличаю щ е- вся тем, что, с целью повышения достоверности за счет возможности работы в режиме самоконтроля операционной части устройства, в него дополнительно введены пять коммутаторов, схема сравнения, буферный регистр, пять триггеров, два элемента НЕ., элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и блок управления, причем входы первого и второго аргументов устройства соединены с первыми информационными входами соответственно второго и третьего коммутаторов, выходы которых соединены с информационными входами соответственно первого и второго регистров аргумен ов, входы начальной установки которых соедииены соответственно с первым и еторым тактовыми выходами б.покч управления, тактовый вход устройства соединен с одноименный входом блока управления, синхронизирующими входами записи первого и второго регистров аргумента, буферного регистра, первого триггера и а ходом первого элемента НЕ, выход которого соединен с входом управления циклом самоконтроля блока управления и синхронизирующим входом второго триггера, информационный вход которого соединен с входом разрешения самоконтроля устройства, выход второго триггера соединен с входами сброса первого, третьего, четвертого и пятого триггеров, управляющими входами второго и третьего коммутаторов и входом разрешения самоконтроля блока управления, третий тактовый .выход блока управления соединен с .синхронизирующим входом пятого триггера, четвертый тактовый выход блока управления соединен с входами установки первого и четвертого триггеров i/f входом

начальной установки буферного регистра, выход четвертого триггера соединен с информационными входами первого и . ретье- го триггеров и управляющим еходом

четвертого коммутатора, выход которого соединен с вторыми информационными входами второго и третьего коммутаторов, выход первого триггера соединен с управляющими входами пятого к шестого коммутаторов и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход кото- роге соединен с выходом знакового разряда второго сумма ора, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с управляющим входом первого коммутатора, ri+1-й разрядный сыход которого соединен с (п+1)- м разрядным информационным входом буферного регистра и (п+1}-разрядным входом первого операнда схемы сравнения, п младших разрядов, выход буферного регистра соединен с rv младшими разрядами входа второго операнда схемы сравнения и первым n-разрядным информационным входом четвертого коммутатора, выходы п-2 млэдших разрядов буферного регистра соединены, с п-2 старшими разрядами второго информационного входа четвертого коммутатора, два младших разряда второго информационного входа которого соединены

со значением логического , выход п+1 старшего разряда буферного регистра соединен с п+1 м разрядов входа второго операнда схемы с|завнени «, входом второго элемента НЕ.и синхронизирующим входом

третьего триггера, выход которого является выходом признака самоконтроля устройства, выход признака неисправности которого соединен с выходом пятого триггера, информационный вход которого соединен с

выходом схемы сравненмя;(п+1)-разрядный выход буферного регистра является выходом результата устройства, выход второго элемзнта НЕ соединен с синхронизирующим входом четвертого триггера, выходы

пятого и шестого коммутаторов соединены с двумя младшими разрядами соответственно первого и третьего сумматоров, первые информационные входы пятого и шестого коммутаторов соединены с входом логического 0, вторые информационные входы которых соединены с входом логической 1,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования координат | 1983 |

|

SU1141405A1 |

| Функциональный преобразователь | 1983 |

|

SU1108442A1 |

| Устройство для буферизации команд | 1991 |

|

SU1789982A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

| Квадратор | 1986 |

|

SU1322273A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Устройство для интерполяции | 1984 |

|

SU1171807A1 |

| Декодирующее устройство линейного циклического кода | 1990 |

|

SU1718386A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1168930A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях. Целью изобретения является повышение достоверности за счет возможности работы в режиме самоконтроля операционной части устройства. Устройство содержит элементы НЕ 1 и 2, блок 3 управления, триггеры 4 и 5, коммутаторы 6 и 7, триггеры 8 и 9, регистры аргумента 10, 11, коммутаторы 12 и 13, буферный регистр 14, коммутатор 15, сумматоры 16 - 18, схемы 19 сравнения, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 20, триггер 21, коммутатор 22 и имеет входы 23 и 24 первого и второго аргументов, тактовый вход 25, вход 26 разрешения самоконтроля, выход 27 результата, выход 28 признака неисправности, выход 29 признака самоконтроля. 2 ил,

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1254478A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления модуля комплексного числа | 1981 |

|

SU1001085A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-11-23—Публикация

1989-07-19—Подача