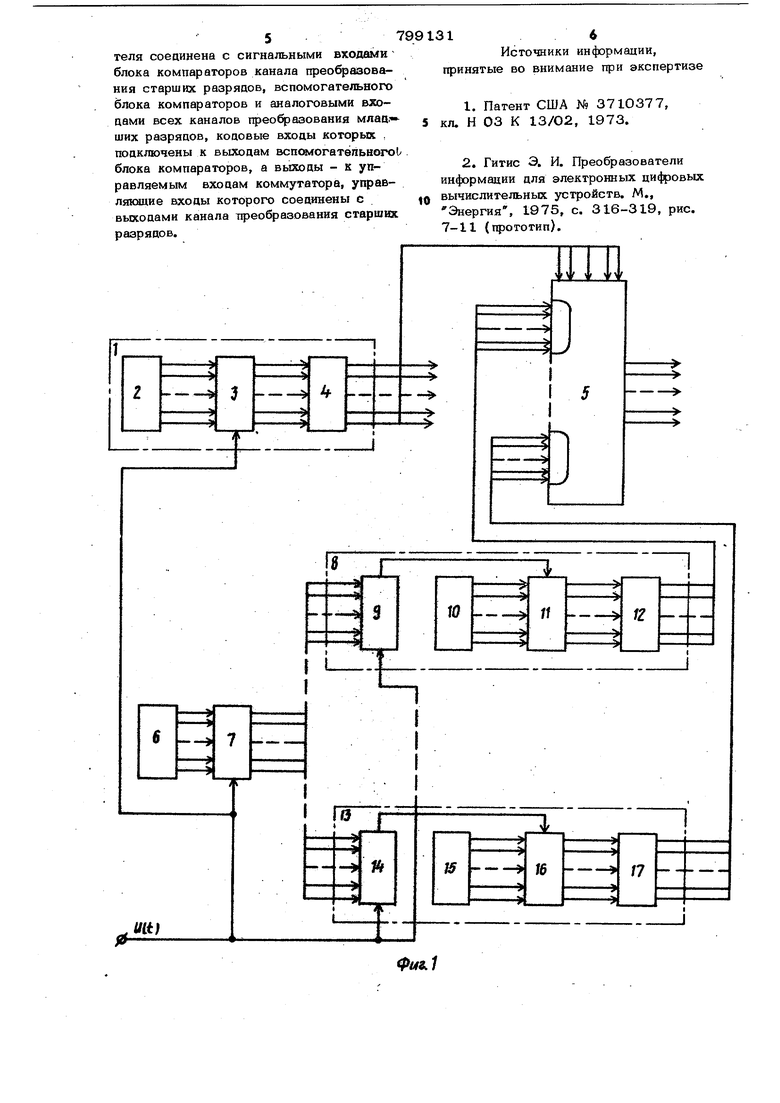

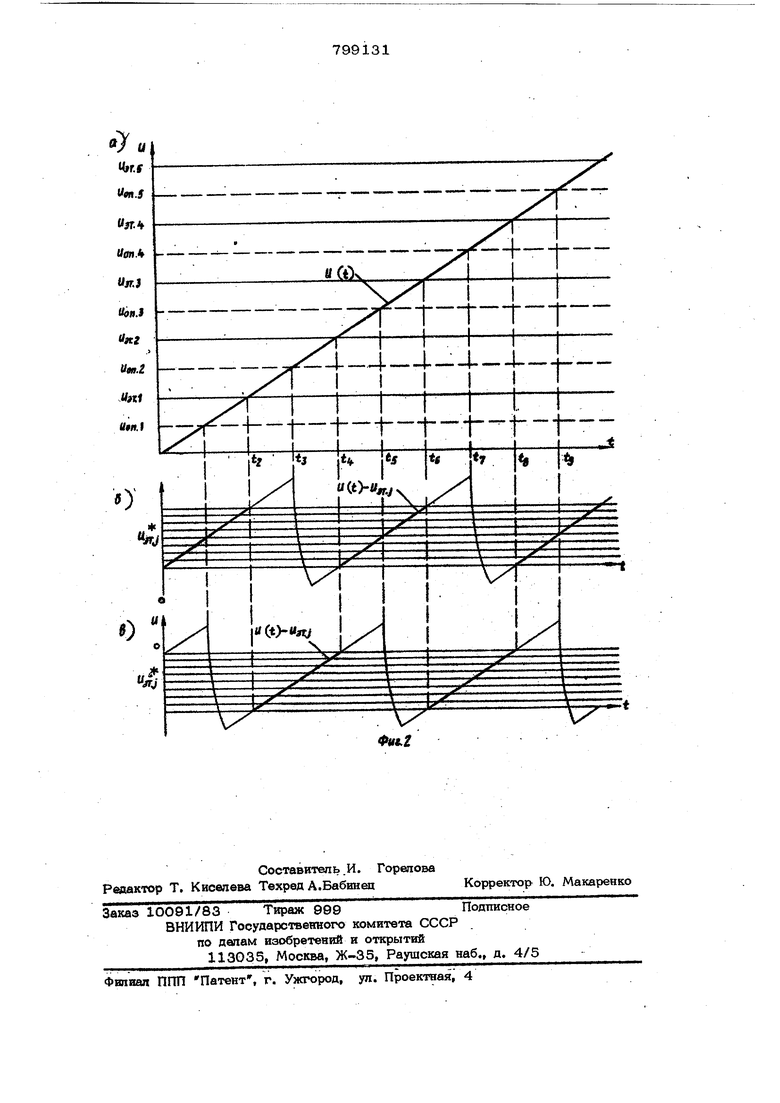

Изобретение относится к информационно-измерительной технике и может быть использовано в осцилографах, автоматиз1фоввнных системах сбора информации, ввооных устройствах ЦВМ и т.и Известны преобразователи на(1ряжш1ия в коа, реализуквдие способ параллельнотюслеоовательного тфеобразования, иэ которых наибольшего быстродействия достигает преобразователь разомкнутого типа fl . Но в таком преобрюователе минималь ное время прео азования ограничено длительностью перехояных процессов в блоке формирования разностного сигнала, неизбежно возникающих в моменты вы- 4fc читания эталонных напр:1жений из нагфяжения гфеофазуемого сигнала. Наиболее близким к данному TexHHHec кому решению является параллельно-последовательный преобразователь напряжения в код, соаержаший канал преобразо-т вания старших разрядов, состоящий из . последовательно соединенньпс источника эталонных напряжений, блока компараторов и шифратора, и канал преобразования млацших разрядов, состоящий из формирователя разностного напряжения, истгочника эталонных напряжений, блока компараторов и шифратора 2J . Такой преобразователь также не обеспечивает необходимого быстродействия из-за влияния переходных процессов на скорость преобразования. Цель изобретения - повышение быстродействия преобразования. Поставленная цель достигается тем, что в параллельно-последовательный преобразователь напряжения в код, содержащий канал преобразования старших разрядов, состоящий из последовательно соединенных источника эталонных напряжений, блока компараторов и шифратора, и канал преобразования младших разрядов, состоящий из формирователя разностного напряжения, источника эталонных напряжений, блока компараторов и шифратора, введены вспомогагельный источник опорных напряжени с блоком компараторов, аополнительные каналы преобразования младших разрядов и : цифровой коммутатор каналов, причем входная клемма преобразователя соединена с сигнальными входами блока компараторов канала преобразования старших разрядов, вспомогательного блока компараторов и аналоговы ми входами всех каналов преобразования младших разрядов, кодовые входы которых подключены к выходам вспомогатель ного блока компараторов, а выходы - к управляемым входам коммутатора, управ. ляющие входы которого соединены с выхо дами канала преобразования старших разрядов. На фиг. I показана функциональная бл схема параппепьно-поспедсжатепьного преобразователя напряжения в код; на фиг. 2 проиллюстрирован {фоцесс кодирования линейно-нарастакяцего напряжения гфи использовании двух каналов преофазования младших разрядов. Устройство содержит канал 1 преобразования старших разрядов, сбЬтояций из последовательно соединеяньк источника 2 эталонных напряжений, .блока 3 компаратора и шифратора 4, шина старших разрядов которого подключена к цифровому коммутатору 5 каналов, вспомогательный источник 6 опорных напря1кетий, подключенный к блоку 7 компараторов, выходы которого соединены с кан лом 8 преофазования младших разрядов, состоящим из формирователя 9 разнос ного сигнала и последовательно соединен ньсс источника 10 эталонных напряжение блока 11 компараторов и шифратора 12, тфичем выход формирователя 9 соешшен со вторым входом блока 11 компараторо Выходы блока 7 компараторов подключены также к вспомогательному канаду 13 разования младших разрядов, содержащих аналоговые блоки: формирователь 14 разностного сигнала, источник 15 эталонных напряжений, блок 16 компараторов и шифратор 17, соединенных также как в канале S. Блоки 3 и 7 компараторов и формирователи 9 и 14 подключены к входной клемме преобразователя. Выходы шифраторов 12 и 17 подключены ко входам коммутатора 5 каналов, выход которог является выходом устройства. Ус1ройство .работает следукшим образом. Преобразуемое напpяжeннeU{t)поступает на блок 3 компараторов канала 1, где срапнивается с набором эталонных напряжений старшей группы: (фиг. 2 а). По состоянию компараторов в шифраторе 4 формируется код старших разрядов. Одновременно напряжение (J(4) поступает на блок 7 компараторов, где сравнивается с опорными напряжениями Uonl (. 2 а). По состоянию компараторов формируются разностные напряжения U(fc)-U5T каждого канала преобразования младших разрядов. Разностные напряжения (фиг. 2 б, в) через формирователи 9 и 14 поступают на блоки 11 и 16 компфаторов, где сравгпшаются с эталонными напряжениями Ugy сформированными источниками 10 и 15 эталонных напряжений. По состоянию компараторов шифраторами 12 и 17 в каждом канале формируется код младших разрядов. Но достоверным этот код будет лишь в канале, где разностное напряжение в этот момент не выходит из зоны эталонных напряжений (толстые линии на фиг. 2 б). Поэтому код Младших разрядов на выход устройства поступает из разли%1ых каналов. Подключение канала для съема кода осуществляется компаратором 5 в соответствии с кодами, поступающими с шифратора 4. Введение нескольких каналов преобразования младших разрядов и организапия тюочередной работы каналов позволяют исключить влияние длительности переходных {фоцессов на скорость преобразования и тем самым повьюить быстродействие устройства. ормула изобре тения Параллельно-последовательный преобразователь на фяжения в код, содержащий канал прео€ 1азования старших разржов, состояций из последовательно соединенных источника эталонньрс напряжений, блока компаратора и шифратора, и канал феофазования младших разрядов, состояпнй из формирователя разностного на1фяжения, источника эталонных напряжений, блока компараторов и шифратора, отличающийся тем, что, с целью повышения быстродействия тфео азования в него введены вспомогательный источник опорных напряжений с блоком компараторов, дополнительные каналы преобразования младших разрядов и цифровой коммутатор , каналов, входная клемма преобразователя соединена с сигнальными входами блока компараторов канала преобразования старших разрядов, вспомогательно го блока компараторов и аналоговыми вхоцами всех каналов преобразования млац, ших разрядов, кодовые входы которых , подключены к выходам вспс 4огатвпьногоЬ блока компараторов, а выходы - к управляемым входам коммутатора, управляющие входы которого соединены с выходами канала преобразования старших разрядов.

Источники информации, принятые во внимание при экспертизе

1.Патент США Ms 3710377, кл. Н 03 К 13/О2, 1973.

2.Гитис Э. И. Преобразователи информации для электронных цифровых вычислительных устройств. М., Энергия, 1975, с. 316-319, рис. 7-11 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ преобразования напряжения в код и устройство для его реализации | 1980 |

|

SU892706A1 |

| Способ преобразования напряжения в циклический код | 1977 |

|

SU978338A2 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1982 |

|

SU1069156A1 |

| Способ параллельно-последовательногопРЕОбРАзОВАНия НАпРяжЕНия B КОд | 1977 |

|

SU819954A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1983 |

|

SU1193809A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1984 |

|

SU1282326A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1981 |

|

SU1039025A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1983 |

|

SU1211881A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1152088A1 |

| Цифровой фазометр | 1985 |

|

SU1298687A2 |

Фиг.1 7« a ax ylff - «- T -I I I 1 I 1 1 T„-t-r T-T-T I , I J I

Авторы

Даты

1981-01-23—Публикация

1977-03-01—Подача