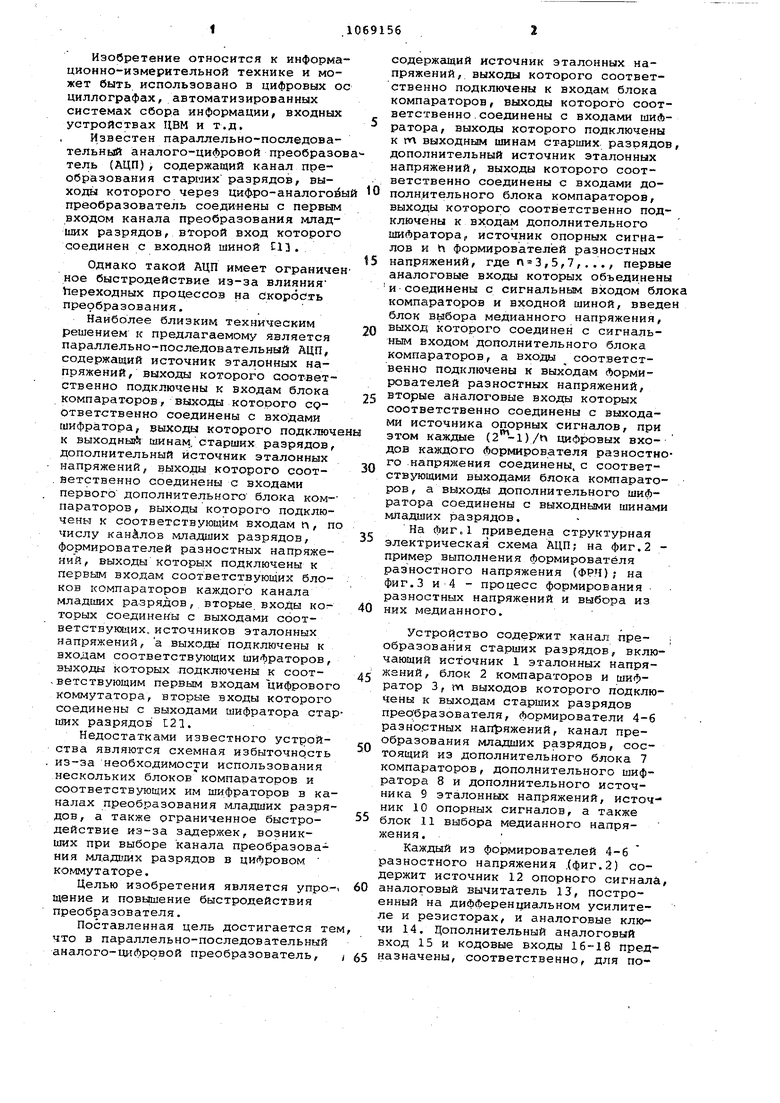

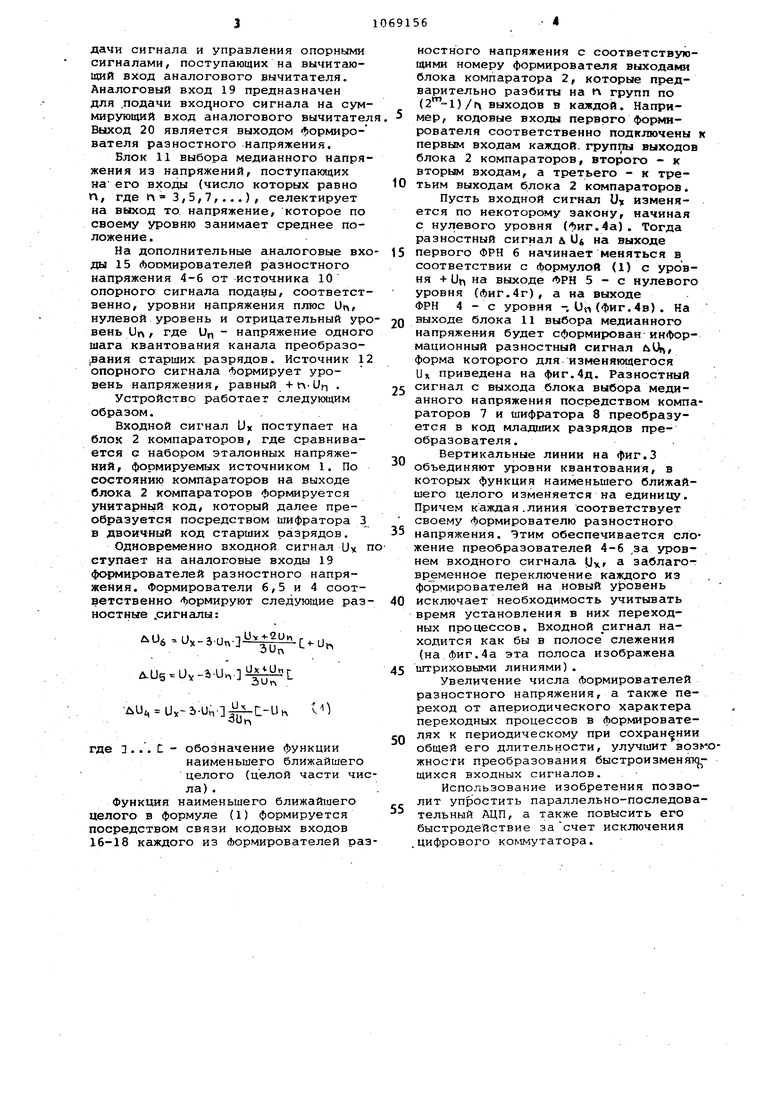

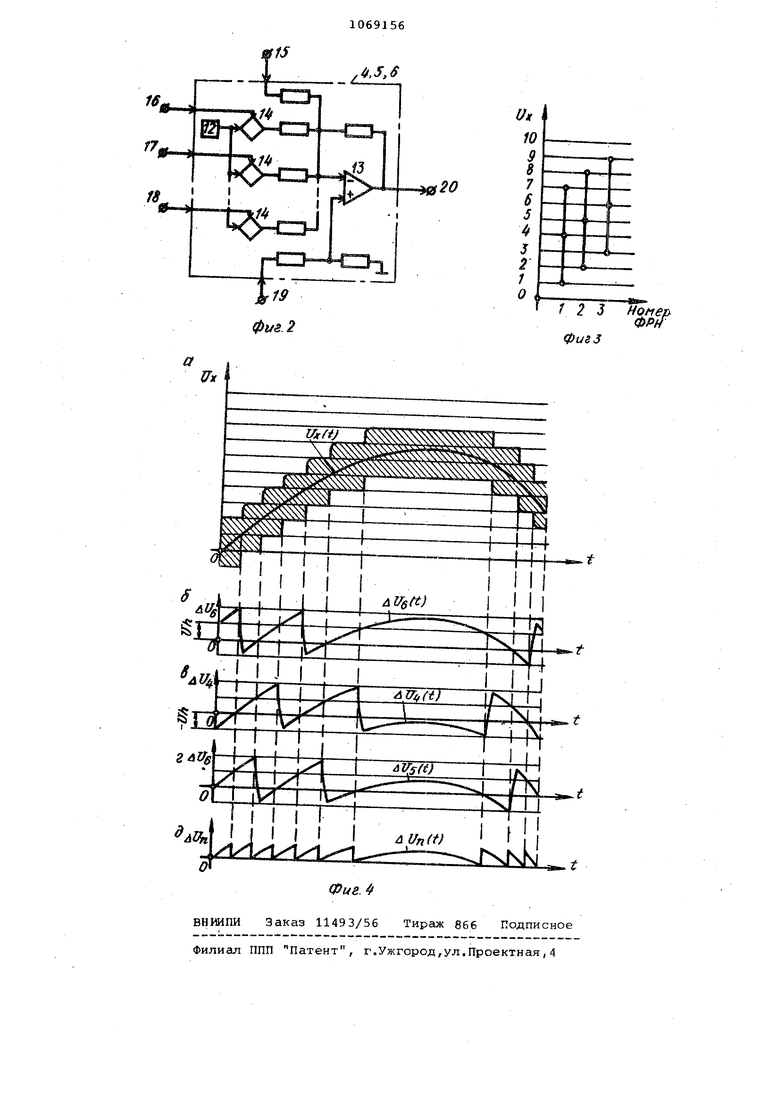

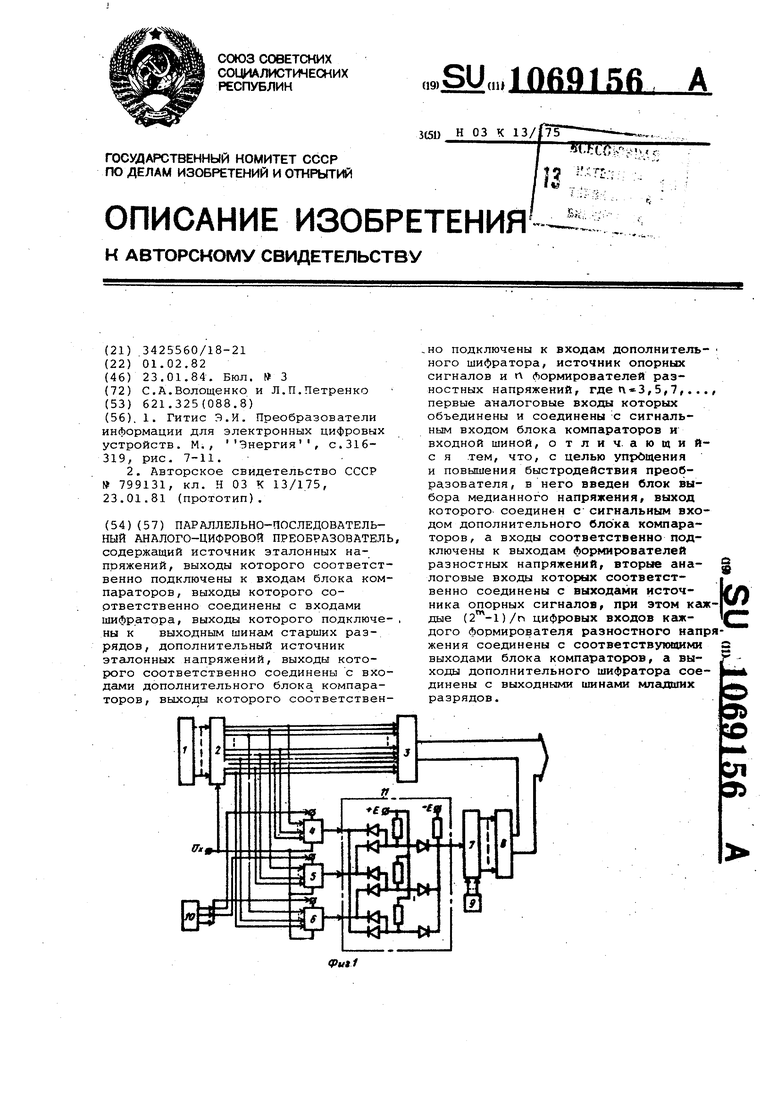

Изобретение относится к информа ционно-измерительной технике и может быть использовано в цифровых о циллографах, автоматизированных системах сбора информации, входных устройствах ЦВМ и т.д. Известен параллельно-последовательный аналого-цифровой преобразо тель (АЦП), содержащий канал преобразования старших разрядов, выходы которого через цифро-аналогой преобразователь соединены с первым входом канала преобразования младших разрядов, второй вход которого соединен с входной шиной С13. Однако такой АЦП имеет ограниче ное быстродействие из-за влияния переходных процессов на Скорс5йть преобразования. Наиболее близким техническим решением к предлагаемом является параллельно-последовательный АЦП, содержащий источник эталонных напряжений, выходы которого соответственно подключены к входам блока компараторов, выходы которого CQОтветственно соединены с входами шифратора, выходы которого подключ к выходныА шинам, старших разрядов, дополнительный источник эталонных напряжений, выходы которого соответственно соединены с входами первого дополнительного блока компараторов, выходы которого подключены к соответствующим входам п, п числу каналов младших разрядов, формирователей разностных напряжений, выходы которых подключены к . первым входам соответствующих блоков компараторов каждого канала младЕяих разрядов, вторые вхоДы ко торых соединены с выходами соответствукядих. источников эталонных напряжений, а выходы подключены к входам соответствующих шифраторов, выходы которых -подключены к соот-ветствующим первьм входам цифровог коммутатора, вторые входы которого соединены с выходами шифратора ста изих разрядов 121. Недостатками известного устройства являются схемная избыточность из-за необходимости использования нескольких блоков компараторов и соответствующих им шифраторов в ка налах преобразования младших разря дов , а также ограниченное быстродействие из-за задержек, возникших при выборе канала преобразования младамх разрядов в цифровом коммутаторе. Целью изобретения является упро щение и повышение быстродействия преобразователя. Поставленная цель достигается т что в параллельно-последовательный аналого-цифровой преобразователь, содержащий источник эталонных напряжений, выходы которого соответственно подключены к входам блока компараторов, выходы которого соответственно .соединены с входами шифратора, выходы которого подключены к m выходным шинам ст-арших разрядов, дополнительный источник эталонных напряжений, выходы которого соответственно соединены с входами дополнительного блока компараторов, выходы которого соответственно подключены к входам дополнительного шифратора,, источник опорных сигналов и h формирователей разностных напряжений, где ,5,7,..., первые аналоговые входы которых объединены и соединены с сигнальным входом блока компараторов и входной шиной, введен блок выбора медианного напряжения, выход которого соединен с сигнальным входом дополнительного блока компараторов, а входы соответственно подключены к выходам Формирователей разностных напряжений, вторые аналоговые входы которых соответственно соединены с выходами источника опорных сигналов, при этом каждые ()/п цифровых входоз каждого формирователя разностного напряжения соединены, с соответствующими выходами блока компараторов, а выходы дополнительного шифратора соединены с выходными шинами младших разрядов. На фиг.1 приведена структурная электрическая схема АЦП; на фиг.2 пример выполнения формирователя разностного напряжения (ФРН); на фиг.З и-4 - процесс формирования разностных напряжений и выбора из них медианного. Устройство содержит канал пре- ; образования старших разрядов, включающий источник 1 эталонных напряжений, блок 2 компараторов и шифратор 3, m выходов которого подключены к выходам старших разрядов преобразователя, формирователи 4-6 разнортных нап яжений, канал преобразования младших разрядов, состоящий из дополнительного блока 7 компараторов, дополнительного шифратора 8 и дополнительного источника 9 эталонных напряжений, источник 10 опорных сигналов, а также блок 11 выбора медианного напряжения. Каждый из формирователей 4-6 разностного напряжения ,(Фиг.2) содержит источник 12 опорного сигнала, аналоговый вычитатель 15, построенный на дифференциальном усилителе и резисторах, и аналоговые ключи 14. Дополнительный аналоговый вход 15 и кодовые входы 16-18 предназначены, соответственно, для подачи сигнала и управления опорными сигналами, поступающих на вычитающий вход аналогового вычитателя. Аналоговый вход 19 предназначен для .подачи сигнала на сум мирующий вход аналогового вычитате Выход 20 является выходом формирователя разностного напряжения. Блок 11 выбора медианного напря жения из напряжений, поступающих на его входы (число которых равно П, где г 3,5,7,...), селектирует на выход то напряжение, которое по своему уровню занимает среднее положение. На дополнительные аналоговые вх ды 15 (Ьоомирователей разностного напряжения 4-6 от источника 10 опорного сигнала подауы, соответст венно, уровни напряжения плюс U, нулевой уровень и отрицательный ур вень Ur, где и - напряжение одног шага квантования канала преобразо|Вания старших разрядов. Источник опорного сигнала формирует уровень напряжения, равный +n-Un . Устройство работает следукидим образом.. Входной сигнал Ux поступает на блок 2 компараторов, где сравнива ется с набором эталонных напряжений , формируемых источником 1. По состоянию компараторов на выходе блока 2 компараторов формируется унитарный код, который далее преобразуется посредством шифратора в двоичный код старших разрядов. Одновременно входной сигнал Uy ступает на аналоговые входы 19 формирователей разностного напряжения. Формирователи 6,5 и 4 соот ветственно формируют следующие ра ностные .сигналы: ., U5 Uv-a.U. AU:, Uy-5-Un-3 t-Un vM где П... С - обозначение функции наименьшего ближайшего целого (целой части чи ла) . Функция наименьшего ближайшего целого в формуле (1) формируется посредством связи кодовых входов 16-18 каждого из Формирователей р ностного напряжения с соответствующими номеру формирователя выходакш блока компаратора 2, которые предварительно разбиты на п групп по () / ( выходов в каждой. Например, кодовые входы первого формирователя соответственно подключены к первым входам каждой- группы выходов блока 2 компараторов, второго - к вторым входам, а третьего - к третьим выходам блока 2 компараторов. Пусть входной сигнал U изменяется по некоторому закону, начиная с нулевого уровня .4а) . Тогда разностный сигнал д О на выходе первого ФРН 6 начинает меняться в соответствии с формулой (1) с уровня + Uii на выходе ФРН 5 - с нулевого уровня (фиг.4г), а на выходе ФРН 4 - с уровня -, Очч {фиг.4в) . На выходе блока 11 выбора медианного напряжен ия будет сформирован информационный разностный сигнал (Оц, форма которого для. изменяющегося Ux приведена на фиг.4д. Разностный сигнал с выхода блока выбора медианного напряжения посредством компараторов 7 и шифратора 8 преобразуется в код младших разрядов преобразователя.. Вертикальные линии на фиг.З объединяют уровни квантования, в которых функция наименьшего ближайшего целого изменяется на единицу. Причем каждая.линия соответствует своему формирователю разностного напряжения. Этим обеспечивается сложение преобразователей 4-6 ,за уровнем входного сигнала (J, а заблаговр менное переключение каждого из формирователей на новый уровень исключает необходимость учитывать время установления в них переходных процессов. Входной сигнал находится как бы в полосе слежения (на фиг.4а эта полоса изображена штриховыми линиями). Увеличение числа формирователей разностного напряжения, а также переход от апериодического характера переходных процессов в формирователях к периодическому при сохранении общей его длительности, улучшит возможности преобразования быстроизменяк щихся входных сигналов. Использование изобретения позволит упростить параллельно-последовательный АЦП, а также повысить его быстродействие за счет исключения .цифрового коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельно-последовательный аналого-цифровой преобразователь | 1981 |

|

SU1039025A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1984 |

|

SU1282326A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1983 |

|

SU1193809A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1181144A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1983 |

|

SU1211881A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1193808A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1202055A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1986 |

|

SU1383500A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU980276A1 |

| Параллельно-последовательский пре-ОбРАзОВАТЕль НАпРяжЕНия B КОд | 1977 |

|

SU799131A1 |

ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛ содержащий источник эталонных напряжений, выходы которого соответст венно подключены к входам блока ком параторов , выходы которого соответственно соединены с входами шифратора, выходы которого подключе ны к выходным шинам старших разрядов, дополнительный источник эталонных напряжений, выходы которого соответственно соединены с вхо дами дополнительного блока компара торов, выходы которого соответстве но подключены к входам дополнитель- ного шифратора, источник опорных сигналов и п ЛормирователеЯ разностных напряжений, где , 5,7,. .., первые аналоговые входы которых объединены и соединены -с сигнальным входом блока компараторов и входной шиной, о тлич. ающийс я тем, что, с целью упрбщения и повышения быстродействия преобразователя, в него введен блок выбора медианного напряжения, выход которого соединен с сигнальным входом дополнительного блока компараторов, а входы соответственно подключены к выходам формнрювателей разностных напряжений, вторые аналоговые входы которых соответственно соединены с выходами источника опорных сигналов, при этом кгигдые ()/п цифровых ВХОДОВ каждого формирователя разностного напряжения соединены с соответствующими а выходами блока компараторов, а выходы дополнительного шифратора соединены с выходными шинами младших разрядов.

| , 1 | |||

| Гитис Э.И | |||

| Преобразователи информации для электронных цифровых устройств | |||

| М., Энергия, с.316319, рис | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Параллельно-последовательский пре-ОбРАзОВАТЕль НАпРяжЕНия B КОд | 1977 |

|

SU799131A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-01-23—Публикация

1982-02-01—Подача