; i:joo;:4rreiiue относитгя к вычис.111тельисй и из :ери ejibiiijH технике и молгет бгиЧь использова110 в азтомаTHSHpoiiannLix 1 форУ:а :1,51оино-измеритель1 ых системах,

Целью изобретени) является yMOSibiiieHHt; погрешностн гтреибраэораник цн(1к;рмлци11 ..

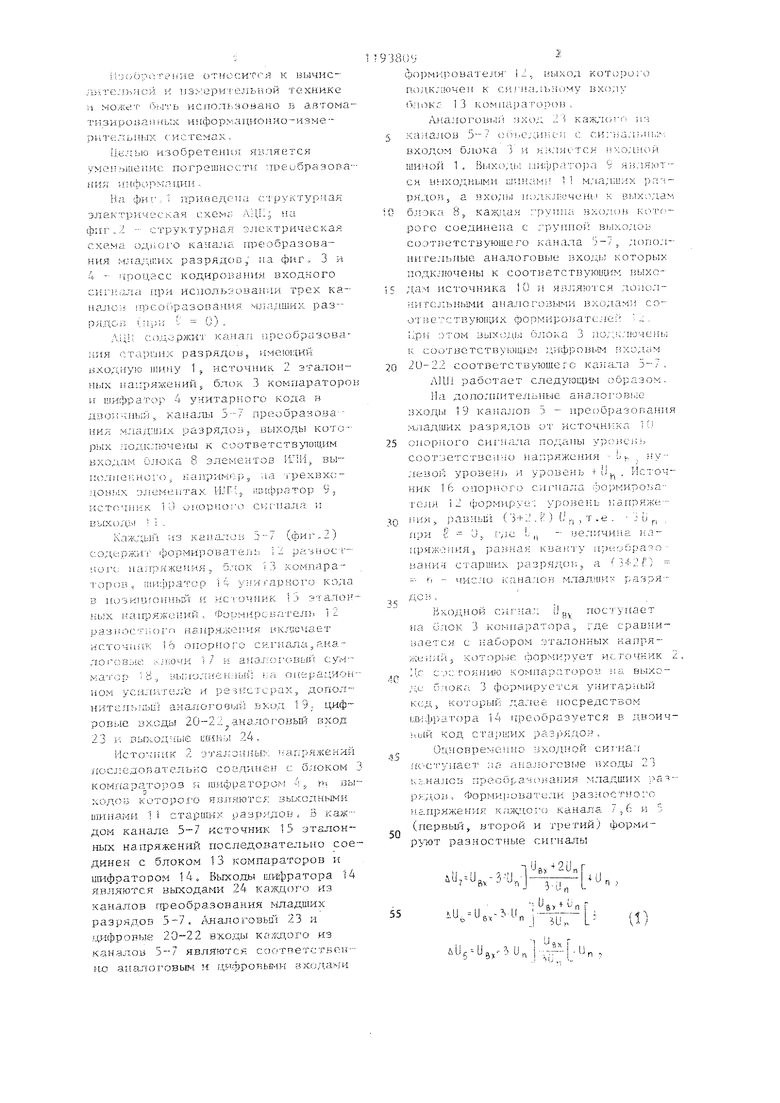

Нл. фиг 1 припедоиа сп рчлегурнак электрическая схем;: ЛЦП; на фигл- - структурная злсктркч.ескак схема oдJ;olo канала преооразовання мла;;11.их разрядов, на . 3 и 4 - чроцасс коднровуния входного при исиользинапии трех ка-налои 1п:)со(фазоваяия младших раз-РЯДОУ; iCipH I 0) .

Д.Ц1:. сл)ДС:ржк1 канал 1Г еобрг13оваиия стариих разрядов, ямеюишк иходиую шипу 1. источник 2 эталонных налрЯлсений S блок 3 компараторо if иифратор 4 унитарного кода в двои-;:нь:й, ка1;а,лы 5---7 преобразова-НИЛ млад:иих разрядов, выходы котоpi)ix лодкл;оче(ы к соответствующим вхо;лам илока 8 элеЕ-шнтов выi:o:jtieHHor( i каиримир. ла ч рехвходоных : jieMeiiTax lUrU lUJitjjpaTop 9,, источник 1U oiiopfioro олПала и

ВЪСХОДЫ i ; .

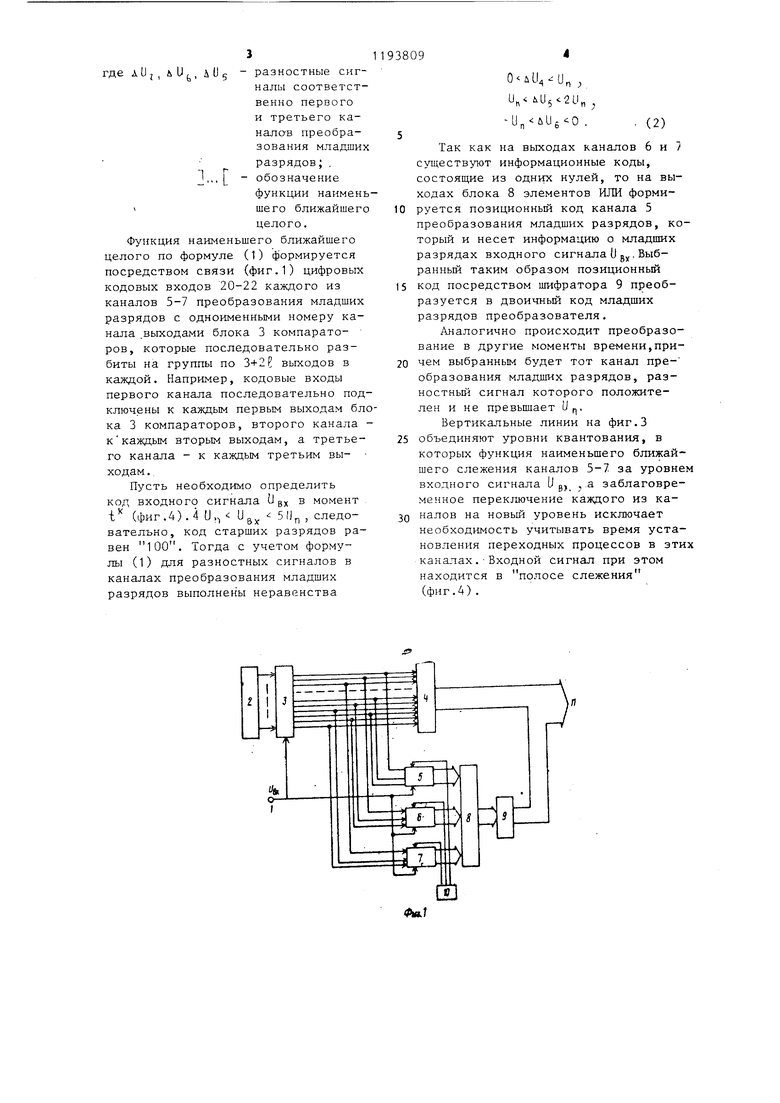

Каж;;ьш из ка1.алоы П / фиглх,) сод :ржи: формнровате) i -: разнос г;;огс налряжсния,, блок i 3 хомпа.раTOTu;i , п(;)1Шгор 14 уми1-аркого кода в позиционный и iJ зтало jibsx ка1фяЖ1. , ФормирС1;ате/и. 1 с разнос: иого нзлря/к зпня нклслает HCTO4iiiiK 16 опорно О сигнала 5 акаЛОГОВЬ ;:; ;-.ЛЮЧИ 1/ ; .-1:ОИС;ВЫЙ С;уМ MaiOp ; уыло:1нь ниый г;а Г иара;.;иониом yc;ij iiTej;c и ре пгс гсрах, дополните л bibni a;- anoroGbiii вхсД 19; цифроВЛС входы 20--22 анадоговый иход 23 и вьо;.одлые шплл 24,

Исто-литк 2 эгал:олиьп: иаг;ряжений иоследояательг о соедина} с OJIOKOM комиараторов я Ш11фратором 4 ., П . выходоц KOTOpofo «Б.пяютc : выходными шинами 1 i старших разрядов. 3 каж-дом канале 5-7 источник 15 эталонных напряжений последователы-ш соединен с блоком 13 компараторов и цшфратором 14. Выхр,аь шиг рагора 14 являются выходэ-ми 24 каждого из каналов гфеобразонания младших разрядов 5-7. /шалоговьй 23 и дифровь е 20-22 входы каждого из каналов 5--7 являются, с-аотпетственно аналоговым и Г1,ифропьн- входами

пол,к.люче11 к си;налгл-юму вхол, блоке 3 комнаратоттов .

AiiaJioBOBi.iJi ВХ11Д 2 i каждсл-ri ия

халалов 5--. с;б, с; си:}1альн),; входом блока 3 и ;нля1,-тся н :СДлсиЧ шиной 1 . Вых( 1.1И:Ьрато)а 9 я;5ЛЯ от- СИ В:-1ходными шпкМИ 1 i M:ia;uui x jja-ря.доп j а Bxo;i i 1(одкл:очен1 к вьходам

6j;oKa 8, грунла }зходон кот(--рого соединена с rpynnofi вь1ходоь соот} етствую1дего канала 3-7, дадюлнительиые аналоговые входь; которьзх подключены к соотнетствукичим Bbixoдам источника К) и явJ:я;olcя доиоллитсльными аналоговыми в :одами сооГ есствую11;их формирователей .:,. При этом въ1хо;1Ы блока 3 л.о;,;ключснь: V. соотвстству101ци; ;;ифро зь м 1ходг1м

2U-22 соответствующего каяа,ла 5-7. ЛИ, рабОТает следующш- образом. Н; доло.лиитеотьные aiiaлотовою зх:оды 19 каналов 5 - преобразования разрядов от источника i О

олорлого сигнала поданы уровень соответственно налряжения - -v. ну-лево -; урсжен)) и урове гь U | , Источ ник 1 6 опо 1ного сиглага ;Ьормиро агел |2 (рормируе: уровень нанриже ЛЯ., (3+2.i-j ;..,, т.е. 3 и ., яри t и,, гд,с LI, - величина нанряжония, рав;1ая Kuairry Hpixjopa o

: - число 1саналов млад 1И-: разря-Вкодной ciiix-aji iJ „ ноетунает на илок 3 ког-н аратора, где сравнивается с набором эталонных напрял;еллй,, KOTopbie (Ьормирует источник Цс гоянию компараторов на выходе . 3 формируется у 1итарный кед к(Г1Х;рый ;;алее посредством Ь-0-;фр;атора 14 нрес)бразуется в двоичiiijiA код старших раз1 ядо}.

Одновременно входной сигнал 1КС|уиае7 ла ;яналоговые входы 23 иг.налов преобра- ова 1ИЯ ладших ,o}, Формирователи разносTJJо го напряжеьг -1Я каж,;ого канала и 3 (первьш, второй и третий; формир -от разностные сигна.аы

«.«-3М 5и1.|.и,

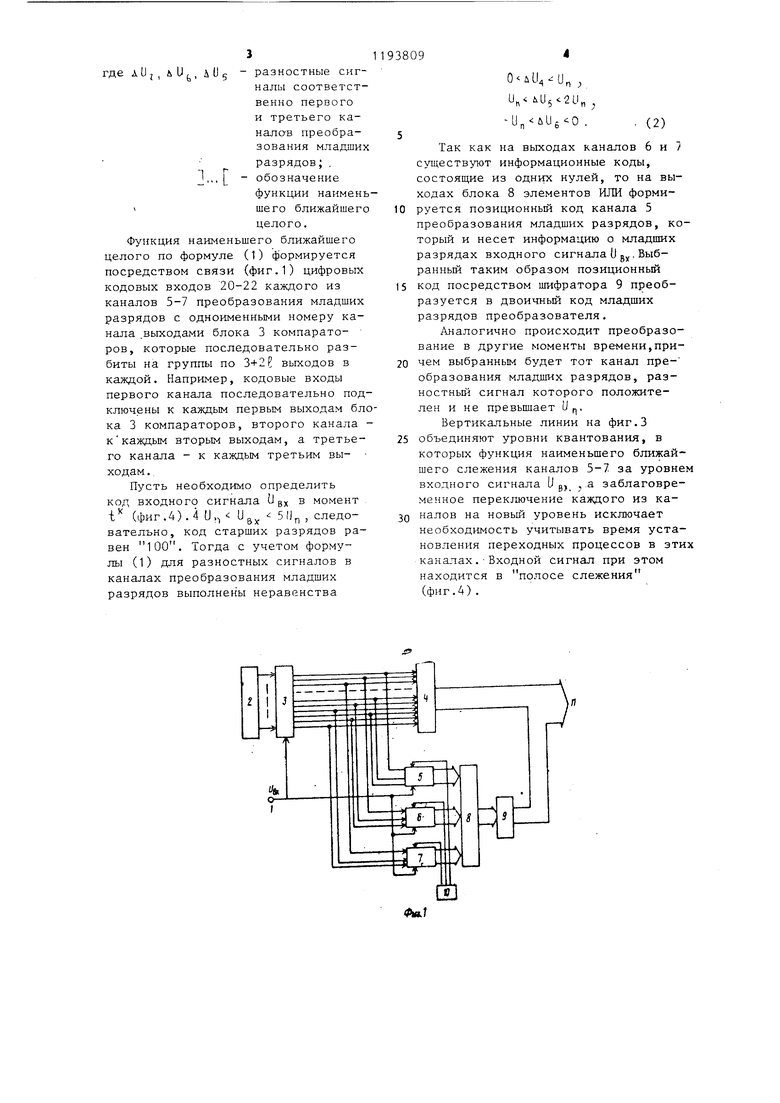

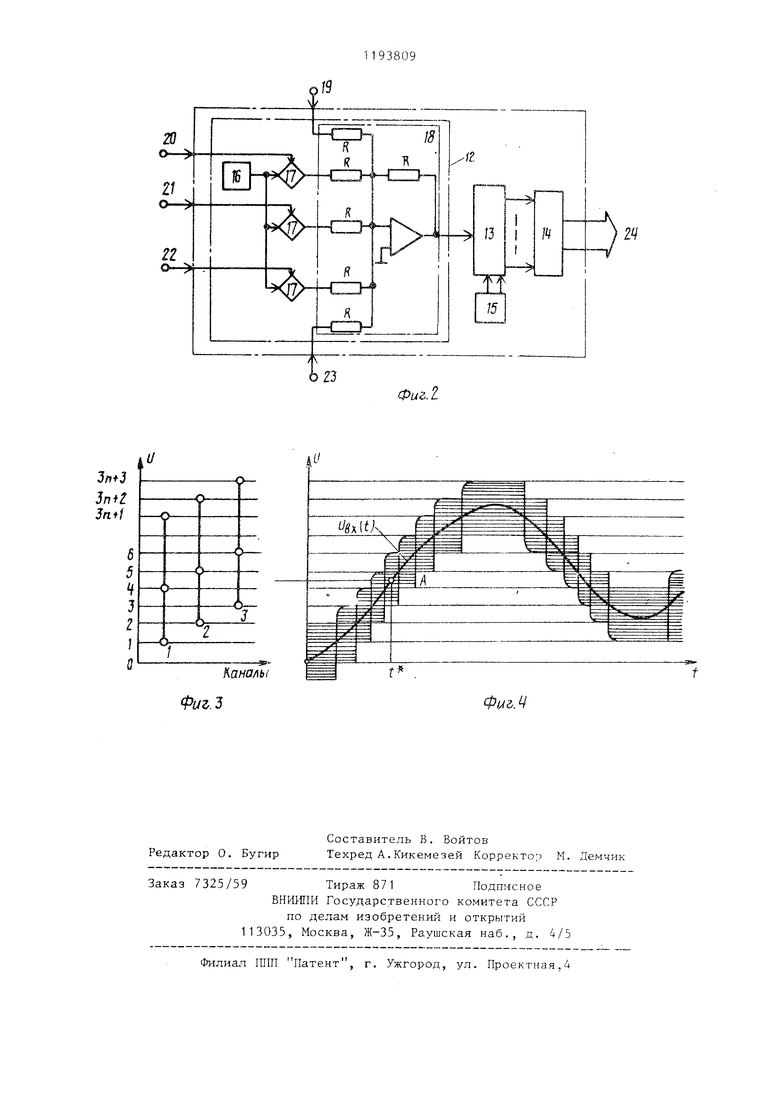

(1) 3 где .AUg разностные сиг налы соответст венно первого и третьего каналов преобразования младши разрядов;, - обозначение функции наимен шего ближайшег целого. Функция наименьшего ближайшего целого по формуле (1) формируется посредством связи (фиг.1) цифровых кодовых входов 20-22 каждого из каналов 5-7 преобразования младших разрядов с одноименными номеру канала .выходами блока 3 компараторов, которые последовательно разбиты на группы по 3+21 выходов в каждой. Например, кодовые входы первого канала последовательно под ключены к каждым первым выходам бл ка 3 компараторов, второго канала ккаждым вторым выходам, а третье го канала - к каждым третьим выходам ., Пусть необходимо определить код входного сигнала вх в момент i (фиг.4). 4 и,-, Ug 51 , следовательно, код старших разрядов ра вен 100. Тогда с учетом формулы (1) для разностных сигналов в каналах преобразования младших разрядов выполнены неравенства 9 ,и, , Так как на выходах каналов 6 и 7 существуют информационные коды, состоящие из одних нулей, то на выходах блока 8 элементов ИЛИ формируется позиционный код канала 5 преобразования младших разрядов, который и несет информацию о младших разрядах входного сигнала (J g. Выбранный таким образом позиционный код посредством шифратора 9 преобразуется в двоичный код младших разрядов преобразователя. Аналогично происходит преобразование в другие моменты времени,причем выбранным будет тот канал преобразования младших разрядов, разностный сигнал которого положителен и не превышает U , Вертикальные линии на фиг.З объединяют уровни квантования, в которых функция наименьшего ближайшего слежения каналов 5-7 за уровнем входного сигнала U gj .а заблаговременное переключение каждого из каналов на новый уровень исключает необходимость учитывать время установления переходных процессов в этих каналах.Входной сигнал при этом находится в полосе слежения (фиг.4).

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельно-последовательный аналого-цифровой преобразователь | 1984 |

|

SU1282326A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1982 |

|

SU1069156A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1983 |

|

SU1211881A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1981 |

|

SU1039025A1 |

| Способ следящего аналого-цифрового преобразования и устройство для его осуществления | 1983 |

|

SU1229954A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1193808A1 |

| Параллельно-последовательский пре-ОбРАзОВАТЕль НАпРяжЕНия B КОд | 1977 |

|

SU799131A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1181144A1 |

| Способ преобразования напряжения в код и устройство для его реализации | 1980 |

|

SU892706A1 |

| Параллельный аналого-цифровой преобразователь | 1986 |

|

SU1332533A1 |

ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЬЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий канал преобразования старших разрядов, выполненный на последовательно соеди1 еннь х источнике эталонных напряжений, блоке компараторов и шифраторе унитарного кода в двоичный, m выходов которого являются выходньми шинами старших разрядов, h ( П 3,5,7...) каналов преобразования младших разрядов, каждый из которых выполнен на формирователе разностного напряжения и последовательно соединенных источнике эталонных напряжений, блоке компараторов и шифраторе унитарного кода в позиционный, выходы которого являются выходами канала преобразования младдшх разрядов, аналоговый и цифровые входы которого являются соответственно аналоговым и цифровым входами формирователя разностного напряжения, выход кото- . рого подключен к сигнальному входу блока компараторов канала преобразования младших разрядов, причем аналоговые входы всех каналов преобразования младших разрядов объединены с сигнальным входом блока компараторов канала преобразования старших разрядов и являются входной тиной, и источник опорных сигна:юв, отличают и и с я Тем, что, с целью уменьшения погрешности преобразования ижЬормации, в него введет-. блок элементов МЧИ и шифратор позиционгюго кода в двоич}1ЫЙ, выходы которого являются выходными шинами младших разрядов, i а входы подключены к соответствуюW щим выходам блока элементов liTM, входы которого соединены с выходами соответств тошлх каналов преобразования младших разрядов, дополнительные аналоговые входы которых подключены к соответствуюци 4 выходам источника опорных сигналов и являются дополнительными аналоX) говыми входа.ми соответствующих СлЭ 00 формирователей разностных напряжений каналов преобразования младших ра зрядов, при этом ; -и цифровой вход -го канала преобразования младших разрядов, где j 1,2,...,()/п, j 1,2,..., п подключен к соответств тощему (i-1)fi+ (}-му выходу блока ком- параторов канала преобразования старших разрядов.

и

о-

ex(t)У

От

Мналы

Фиг.З

,

Г .

.

| Статистические измерения и алгоритмизация измерений | |||

| Вып | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Рязань, 1978, с | |||

| Деревянный торцевой шкив | 1922 |

|

SU70A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Бахтиаров Г.Д | |||

| и др | |||

| Аналогоцифровые преобразователи | |||

| М., 1980, с | |||

| Мяльно-трепальный станок для обработки тресты лубовых растений | 1922 |

|

SU200A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1985-11-23—Публикация

1983-12-27—Подача