.(54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК СИСТЕМ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ

та «исключительное ИЛИ-НЕТ, а другой вход через блок задержки соединен с выходом счетчика, а выход блока управления подключен к другому входу блока задержки, при этом анализатор выполнен в виде объединенных по первому второму и третьему входам обнаружителя ложного фазирования, обнаружителя ложного выхода из синхронизма, счетчика, блока определения времени отсутствия синхронизма, блока определения времени поиска, выход которого через элемент ИЛИ подключен к входу регистратора, а также пороговый блок, соединенньш с блоком сравнения, входы которого соединены соответственно с выходами блока определения времени поиска элемента ИЛИ, блока определения времени отсутствия синхронизма и другим входом элемента ИЛИ, причем выходы обнаружителя ложного фазирования, обнаружителя ложного выхода из синхронизма, счетчика, блока определения времени поиска и блока сравнения подключены к входам регистратора, при этом входы блока определения времени поиска и вход блока сравнения являются входами анализатора.

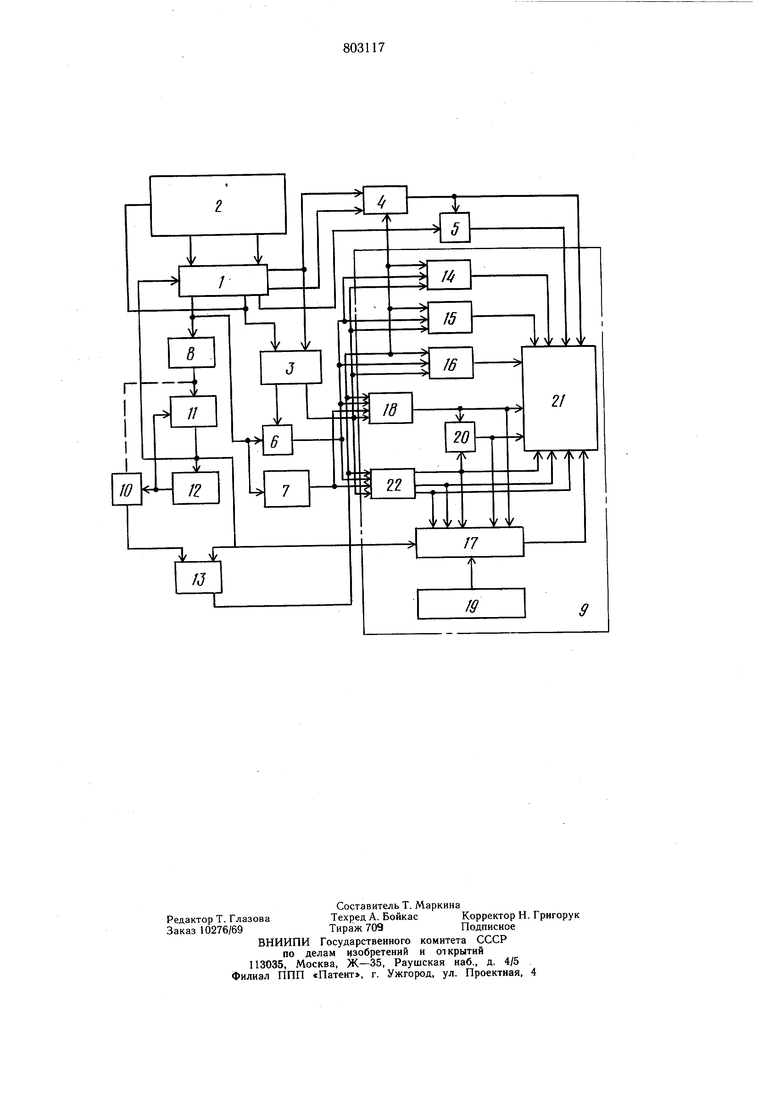

На чертеже дана структурная электрическая схема предложенного устройства.

Устройство содержит формирователь 1 имитационных сигналов, формирователь 2 сигналов трансформации символов, исследуемый объект 3, элемент «исключительное ИЛИ-НЕТ 4, элементы И 5 и 6, хронизатор 7, блок 8 управления, анализатор 9, блок 10 задержки, формирователь 11 импульсов сбоя, счетчик 12, триггер 13. Анализатор 9 состоит из обнаружителя 14 ложного фазирования, обнаружители 15 ложного выхода из синхронизма счетчика 16, блока 17 сравнения, блока 18 определения времени отсутствия синхронизма порогового блока 19, элемента ИЛИ 20, регистратора 21 и блока 22 определения времени поиска. Устройство работает следующим образом. Управляющая последовательность, период которой заведомо превыщает время воестановления потерянного синхронизма, с выхода блока 8 поступает на вход формирователя 11, обеспечивающего формирование импульсов сбоя, число которых соответствует числу испытаний, определяемому счетчиком 12. По заполнении счетчика 12 выдается сигнал, запрещающий дальнейщее формирование импульсов сбоя. Общее время проводимых измерений определяется состоянием триггера 13, который подготавливается первым же импульсом сбоя с выхода формирователя 11, а сбрасывается импульсом с выхода счетчика 12, задержанным на период следования управляющей последовательности на блоке 10.

Импульсы сбоя с выхода формирователя 11 поступают также на формирователь 1, изменяя временное положение синхросимволов в групповом сигнале. В качестве сигналов, передаваемых на информационных позициях цикла, используется псевдослучайная последовательность с выхода формирователя 2. Подключение дополнительных п выходов формирователя 2 позволяет трансформировать символы группового имитационного сигнала с заданной вероятностью Р (0,5)

Входным сигналом формирователя 2 являются тактовые импульсы с одного из выходов формирователя 1.

Формирователь 1 формирует искаженный и неискаженный с вероятностью Р (0,5) групповой сигнал, а также вспомогательные последовательности, соответствующие цикловым импульсам и временному положению синхросигнала. Тактовые импульсы и групповой сигнал с заданной вероятностью сбоев символов являются входными сигналами исследуемого объекта 3, выходными сигналами которого являются импульс фазирования (цикловой импульс) и сигнал ндикaции состояния синхронизма. Элемент И 6 служит для определения синхронизма или расхождения фаз системы цикловой синхронизации и циклового импульса с выхода формирователя 1, который служит также для синхронизации. На выходе элемента «исключительное ИЛИ-НЕТ 4 появляются импульсы, которые за время измерения определяют вероятность сбоя символов группового сигнала. Эти импульсы, простробированные с помощью элемента И 5, последовательностью, соответствующей временному положению синхросигнала, свидетельствуют о вероятности сбоев синхросимволов.

Обнаружение ложных фиксаций состояния синхронизма производится обнаружителем 14, если исследуемый объект 3 переходит в режим синхронизма раньще, чем на соответствующем входе обнаружителя 14 появились импульсы с выхода элемента И 6.

Число этапов поиска определяется с помощью счетчика 16. Если в процессе поиска индицируемого исследуемым объектом 3, импульсы с выхода элемента И 6 появляются, а затем пропадают и это происходит неоднократно, причем в конце концов синхронизм достигается, то это и есть этапы поиска.

Измерение характеристик быстродействия т.е. времени восстановления синхронизма его составляющих, а также дифференциальной и интегральной функции распределения указанных характеристик осуществляется с помощью блоков 18, 22, 17, 19 элемента ИЛИ 20.

Время обнаружения отсутствия синхронизма определяется числом меток времени, появивщихся на входе блока 18 с момента исчезновения импульсов на выходе элемента И 6 до момента перехода системы цикловой синхронизации исследуемого объекта 3 в режим поиска. Промежуток времени с момента перехода в поиск до появления импульсов на выходе элемента И 6 определяют время поиска синхросигнала с момента появления импульсов на выходе элемента И 6 до перехода исследуемого объекта 3 в режим синхронизма (время фиксации состояния синхронизма), а промежуток времени пока исследуе мый объект 3 индицирует поиск (суммарное время поиска и фиксации состояния синхронизма). Метки времени, появляющиеся на выходах блока 22 соответствуют упомянутые выше промежутки времени. Просуммированные на элементе ИЛИ 20 метки времени, соответствующие времени обнаружения отсутствия синхронизма и суммарному времени поиска и фиксации состояния синхронизма, определяют общее время восстановления синхронизма. С помощью порогового блока 19 устанавливается необходимая цифра, соответствующая аргументу дифференциальной или интегральной функции распределения. На выходе блока 17 сравнения появляется определенное число импульсов, соответствующих восстановлению потерянного синхронизма за строго определенное время или же за время не превышающее времени, соответствующего установленному аргументу функции распределения. Измеряемые с помощью предложенного устройства вероятностные характеристики быстродействия и помехоустойчивости систем цикловой синхронизации и имитируемого группового сигнала подаются на вход регистратора 21. Таким образом, предложенное устройство позволяет получить при автономных исследованиях систем цикловой синхронизации достаточно полную картину вероятностных характеристик помехоустойчивости и быстрот действия процессов восстановления синхронизма. Оно обладает расширенными функциональными возможностями по сравению с устройством-прототипом и обеспечивает измерение различных вероятностных характеристик быстродействия цикловых синхронизаторов как при неискаженном групповом сигнале, так и при сбоях его символов. Формула изобретения Устройство для измерения характеристик систем цикловой сиихронизации, содержащее последовательно соединенные формирователь имитационных сигналов, блок управления, формирователь импульсов сбоя и счетчик, выход которого подключен к другому входу формирователя импульсов сбоя а также анализатор, первый и второй входы которого соединены с выходами исследуемого объекта и хронизатора, а первый и второй выходы формирователя имитационных импульсов подключены к входам хронизатора и исследуемого объекта, отличающееся тем, что, с целью повышения точности измерения, введены триггер, формирователь импульсов трансформации символов, блок задержки, элемент «исключительное ИЛИНЕТ и два элемента И, при этом второй выход формирователя имитационных сигналов подключен к входу формирователя импульсов трансформации символов, выходы которого подключены к входам формирователя имитационных сигналов, выходы которых подключены соответственно к входам первого и второго элементов И и элемента «исключительное ИЛИ-НЕТ, выход которого подключен к другому входу второго элемента И и третьему входу анализатора, четвертый вход которого соединен с входом счетчика, другим входом формирователя имитационных сигналов и входом триггера, выход которого подключен к пятому входу анализатора, другому входу элемента «исключительное ИЛИ-НЕТ. а другой вход через блок задержки соединен с выходом счетчика, а выход блока управления подключен к другому входу блока задержки. 2. Устройство по п. 1, отличающееся тем, что анализатор выполнен в виде объединенных по первому, второму третьему входам обнаружителя ложного фазирования, обнаружителя ложного выхода из синхронизма, счетчика, блока определения времени отсутствия, блока определения времени поиска, выход которого через элемент ИЛИ подключен к входу регистратора, а также пороговый блок, соединенный с блоком сравнения, входы которого соединены соответственно с выходами блока определения времени поиска, элемента ИЛИ, блока определения времени отсутствия синхронизма и другим входом элемента ИЛИ, причем выходы обнаружителя ложного фазирования, обнаружителя ложного выхода из синхронизма, счетчика, блока определения времени поиска и блока сравнения подключены к входам регистратора, при этом входы блока определения времени поиска и вход блока сравнения являются входами анализатора. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР по заяв е № 2566018/18-09, кл. Н 04 L 7/02, 1977.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения вероятностных характеристик процессов восстановления синхронизма по циклам | 1977 |

|

SU738183A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| Устройство синхронизации по циклам | 1990 |

|

SU1809543A1 |

| Устройство синхронизации по циклам | 1976 |

|

SU618858A1 |

| Устройство синхронизации по циклам | 1975 |

|

SU544160A1 |

| Устройство групповой тактовой синхронизации | 1982 |

|

SU1022325A2 |

| Устройство синхронизации по циклам | 1980 |

|

SU944135A1 |

Авторы

Даты

1981-02-07—Публикация

1979-04-02—Подача