(54) УСТРОЙСТВО СИНХРОНИЗАЦИИ ПО ЦИКЛАМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации по циклам | 1988 |

|

SU1690209A1 |

| Устройство цикловой синхронизации | 1980 |

|

SU907838A2 |

| Устройство для синхронизации по циклам | 1991 |

|

SU1811019A1 |

| Устройство цикловой синхронизации | 1987 |

|

SU1510104A1 |

| Устройство цикловой синхронизации | 1981 |

|

SU987836A1 |

| ЦИФРОВАЯ СИСТЕМА ПЕРЕДАЧИ С ДВУСТОРОННИМ СОГЛАСОВАНИЕМ СКОРОСТИ | 1991 |

|

RU2022476C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| Устройство цикловой синхронизации | 1977 |

|

SU668100A2 |

39

Ноль изобретения - повышение помехзащищенности.

Цель достигается тем, что в устройство синхронизации по циклам, содержащее последовательно соединенные регист сдвига, деши(|ратор, первый анализатор и первый накопитель, последовательно соединенные анализатор и накопитель, к входуСброскоторого подключен выход первого накопителя, а также элемент И, триггер и генераторное оборудование, первый выход которог подсоединен к первому входу второго анализатсра, а второй выход - к втором входу первого анализатора, введены последовательно соединенные первый дешифратор искажений и втароА дешифратор искажений, первый и второй выходы котсфого подсоединены к первому и второму входу элемента И, к третьему входу которого подсоединен второй выход первого дешифратора искажений, первый вход которого подключен к входу регистра сдвига и является входом ycivройства, а второй вход подключен к

третьему выходу генераторного оборудования к первому и второму входам которого подключены соответствующие выходы триггера, первый вход которого подключен к выходу первого накопителя, а второй вход подключен к выходу второго накопителя и входу Сброс первого накопителя, при этом выход регистра сдвига подсоединен к второму входу BTqporo дешифратора искажений, а выход элемента И подсоединен ко второму входу второго анализатора.

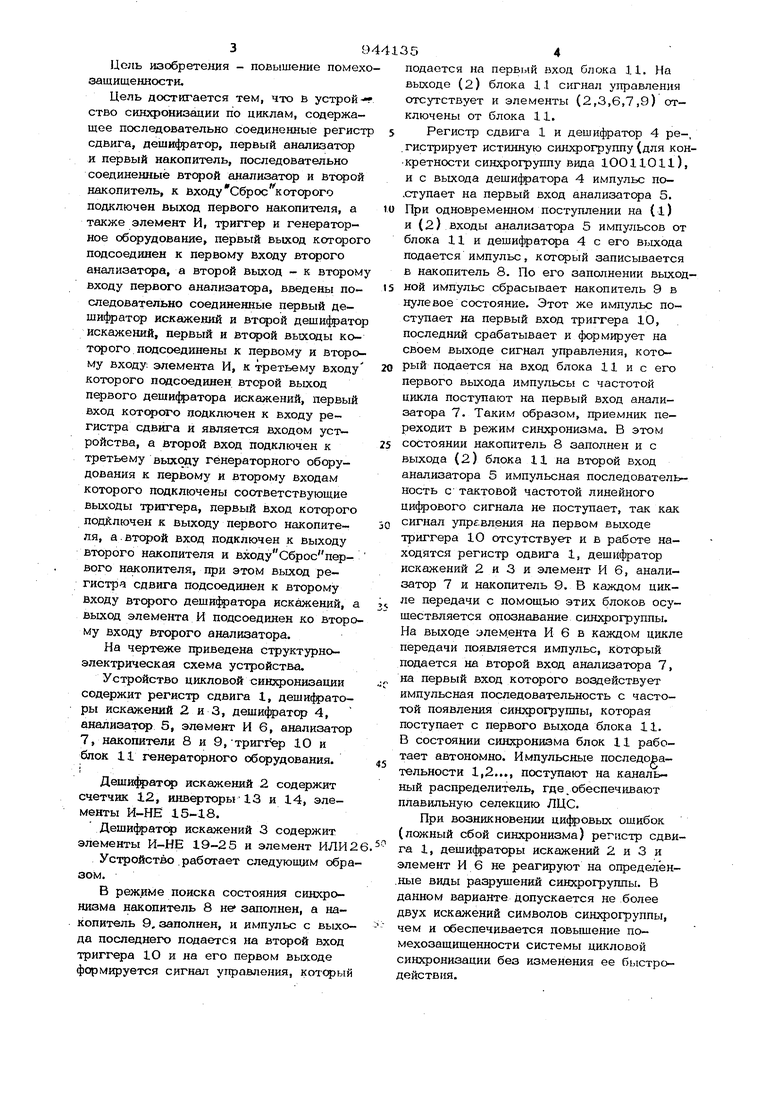

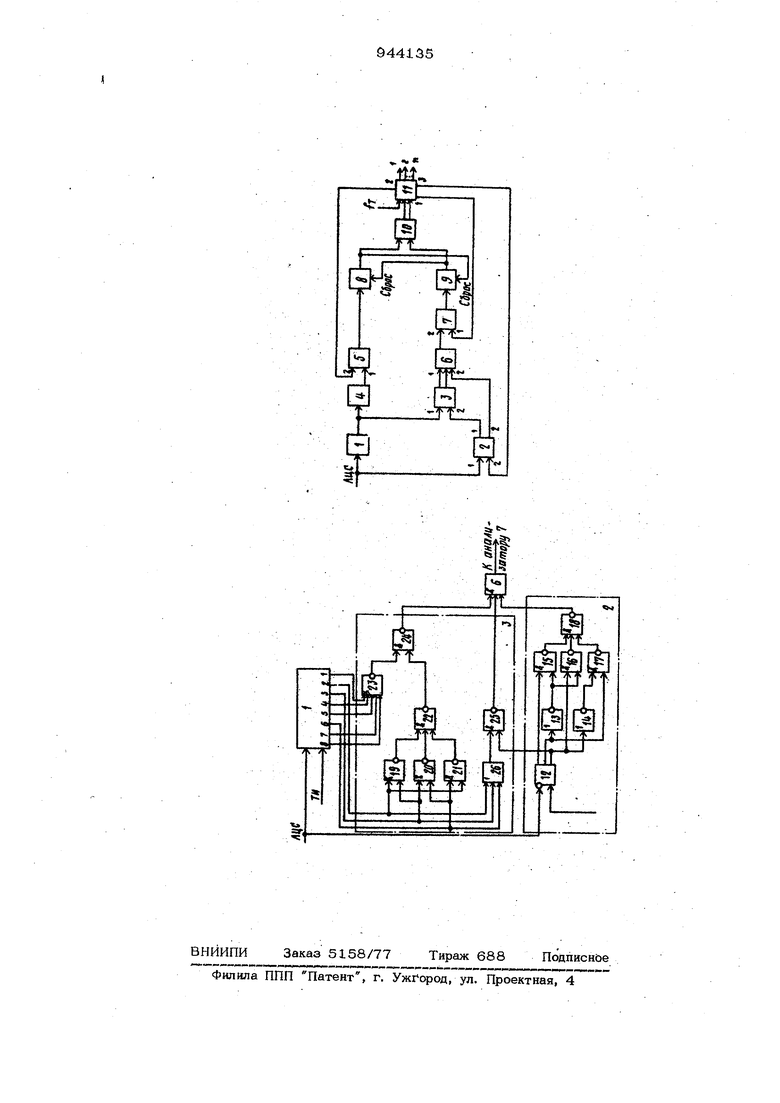

На чертеже приведена структурноэлектрическая схема устройства.

Устройство цикловой синхронизации содержит регистр сдвига 1, деши45 аторы искажений 2 и 3, дeшифpaтqз 4, анализатор 5, элемент И 6, анализатор 7, накопители 8 и 9,-триггер 10 и блок 11 генераторного оборудования.

Деши45 атор искажений 2 содержит счетчик 12, инверторы 13 и 14, элементы И-НЕ 15-18.

Дешифратор искажений 3 содержит элементы И-НЕ 19-25 и элемент ИЛИ2

Устройство . работает следующим образом.

В режиме поиска состояния синхронизма накопитель 8 не заполнен, а накопитель 9, заполнен, и импульс с выхода последнего подается на второй вход триггера Ю и на его первом выходе формируется сигнал уггравления, который

54

одается на первый вход блока 11. На ыходе (2) блока 1.1 сигнал управления отсутствует и элементы (2,3,6,7,9) отлючены от блока 11.

Регистр сдвига 1 и дешифратор 4 ре-, гистрирует истинную синхрогруппу (для конкретности синхрогруппу вида lOOllOll), и с выхода деши4ратора 4 импульс по- ступает на первый вход анализатс а 5. При одновременном поступлении на (l) и (2) входы анализатора 5 импульсов от блока 11 и дешифратора 4 с его выхода одается импульс, котсрый записывается в накопитель 8. По его заполнении выходной импульс сбрасывает накопитель 9 в нулевое состояние. Этот же импульс поступает на первый вход триггера 10, последний срабатывает и формирует на своем выходе сигнал управления, котоый подается на вход блока 11 и с его ервого выхода импульсы с частотой цикла поступают на первый вход анализатора 7. Таким образом, приемник переходит в режим синхронизма. В этом состоянии накопитель 8 заполнен и с выхода (2) блока 11 на второй вход анализатора 5 импульсная последовательность с тактовой частотой линейного цифрового сигнала не поступает, так как сигнал управления на первом выходе триггера 1О отсутствует и в работе находятся регистр одвига 1, дешифратор искажений 2 и 3 и элемент И 6, анализатор 7 и накопитель 9. В каждом цикле передачи с помощью этих блоков осуществляется опознавание синхрогруппы. На выходе элемента И 6 в каждом цикле передачи появляется импульс, который подается на второй вход анализатора 7, на первый вход которого воздействует импульсная последовательность с частотой появления синхрогруппы, которая поступает с первого выхода блока 11. В состоянии синхронизма блок 11 работает автономно. Импульсные последовательности 1,2..,, поступают на канальный распределитель, где,обеспечивают плавильную селекцию ЛЦС.

При возникновении цифровых ошибок (ложный сбой синхронизма) регистр сдвига 1, дешифраторы искажений 2 и 3 и элемент И 6 не реагируют на определенные виды разрушений синхрогруппы. В данном варианте допускается не более двух искажений символов синхрогруппы, чем и обеспечивается повьпиение помехозащищенности системы цикловой синхронизации без изменения ее быстродействия. Как при ложном сбое синхронизма (возникновение цифровых ошибок), так и при истинном сбое синхронизма, (временной сдвиг импульсной последовательности не менее чем на од1Ш тактовый интервал ЛЦС относительно соответствующей импульсной последовательности блока 11 возможны две ситуации: при искажении трех и б.олее единиц или трех нулей в синхрогруппе на втором выходе дешифратора искажений 2 при искажений двух и более нулей и хотя бы одной единицы или двух и более единиц и хотя бы одногЪ нуля на первом выходе дешифратора искажений 3 О. Дешифратор искажений 2 управляется сигналами с блока 11 и начинает работать с приходом первого разряда синхрогруппы и заканчивает работу после прихода последнего разряда синзфогруппы. В случае хотя бы одной из ситуаций на выходе элемента И G нуль, который поступает на второй вход анализатора 7 на первый вход которого воздействует импульсная последовательность с часто- той появления синхрогруппы. Это объясняется тем, что в состоянии синхронизма накопитель 8 заполнен, вследствие чего на второй вход блока 11 воз действует сигнал управления триггера 1 На выходе анализатора 7 появляется импульс, который записывается в накопитель 9, и по его заполнении с выхода подается сигнал на второй вход триггера 10. На первом выходе триггера 1О формируется сигнал управления, которым осуществляется фазирование блока 11 и, кроме того, импульсная последовательность с ЛЦС через блок 11. поступает н второй вход анализатора 5, а импульсная последовательность с частотой появления синхрогруппы на первьй вход ан лизатора 7 не поступает. Одновременно сигнал с выхода накопителя 9 сбрасывает накопитель 8 в нулевое состояние и устройство синхронизации по циклам переходит в режим поиска. При одновременном искажении двух и более нулей и хотя бы одной единицы и при одновременном искажении двух и более единиц и хотя бы одного нуля, т.е. при наличии трех и более искажений в сШ1хрогруш1е на одном из выходов дешифратора искажений 3 О. При искажении трех и более единиц или трех нулей в синхрогруппе, на выходе дешифратора искажений 2 О. Все выходы деши4раторов искажений 2 и 3 подаются на входы трехвходового логического элемента И 6, Достаточно одного Нуля на входе этого элемента И 6, как на его выходе ноль. Счетчик 12 управляется сигналами с блсжа 11. Счетчик 12 начинает считывание нулей с 1ФЯХОДОМ первого разряда синхрогруппы и заканчивает счет нулей после прихода последнего разряда синхрогруппы. Данное устройство сшсфонизацни по циклам позволяет существенно повысить помехозащ1аценность при допустимых иокажениях символов синхрогруппы. Формула изобретения Устройство синхронизации по циклам, содержащее последовательно соединенные регистр сдвига, дешифратор, первый аналнзатор и первый накопитель, последовательно соединенные втсрой анализатор и второй накопитель, к входу Сброс которого подключен выход накопителя, а также элемент И, триггер и генератсрное оборудование, первый выход которого подсоединен к первому входу второго анализатора, а агорой выход - к втсрому входу первого анализатора, о т л ич а ющееся тем, что, с целью повьшхе™ помехозащищенности, введены последовательно соединенные первый дешифратор искажений и Второй дешифратор искажений, первый и второй выходы ко торого подсоединены к н второму входу элемента И, к третьему входу которого подсоединен второй выход первого дешифратора искажений, первый вход которого подключен к входу регистра сдвига и является входом устройства, а второй вход подключен к третьему выходу генераторного обсрудовання, к первому н второму входам которого подключены соответствующие выходы триггера, первый вход которого подключен к выхо«У первого наксшИтеля, а второК вход подключен к выходу накопителя и входу Сброс первого накопителя, ирп ЭТОМ выход регистра сдвига подсоединен к второму входу второго дешифратора искажений, а выхса элемента И подсоедниен к второму входу второго анализатора. Источники инфqpмaции, 1финятыв во внимание при экспертизе 1. Авторское свидетельство СССР № 661836, кл. Н О4Ь 7/О8, 1977. 2. Левин Л. С, и Плоткин М. А. Основы построения цифровьтх систем передачи. М., Связь, 1975, с. 119, рис. 4,2 (хрототип).

Авторы

Даты

1982-07-15—Публикация

1980-12-22—Подача