54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СУММАТОРА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения чисел с контролем | 1978 |

|

SU885995A1 |

| Устройство для обнаружения и исправления ошибок сумматора | 1982 |

|

SU1038946A1 |

| Устройство для контроля на четность двоичной информации | 1981 |

|

SU1015388A1 |

| ДВОИЧНЫЙ СУММАТОР С КОНТРОЛЕМ ПО МОДУЛЮ 3 | 1972 |

|

SU358697A1 |

| Устройство для контроля арифметических операций по модулю | 1987 |

|

SU1499351A1 |

| Устройство для умножения | 1985 |

|

SU1291975A1 |

| Арифметико-логическое устройство связного процессора | 1978 |

|

SU765808A1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ИНФОРМАЦИИ С ОБНАРУЖЕНИЕМ ДВОЙНЫХ ОШИБОК | 2009 |

|

RU2403615C2 |

| Устройство для деления | 1990 |

|

SU1721603A1 |

| Устройство для контроля информации на четность | 1985 |

|

SU1339898A1 |

1

Изобретение относится к вычислительной технике, а именно к устройствам контроля сумматоров ЦВМ.

Известны устройства для контроля сумматора, в которьах вырабатываются и сравниваются основные и дополнител ные значения каждого разряда результата с помощью схем сложения по модулю два. В этом устройстве разряды слова-результата выдаются параллельно по основным и дополнительным шина и сравниваются l .

Недостаток этого устройства - болшое количество контролирующей аппаратуры и, как следствие, низкая на-т дежность.

Наиболее близким техническим решенией к изобретению являзтся устройство для контроля сумматора, содер-, жащее первую схему сложения по моду лю два, п входов которой соединены с первыми входами устройства, а выход с4:ервым выходом устройства, блок дл образования дополнительных сумм, 2п входов и (2п 1)-ый вход которого соединены соответственно со вторьми и третьим входами устройства. В состав устройства входят также вторые схемы сложения по модулр два, число которых соответствует числу контролируемых разрядов, т.е. п, причем первые входы этих схем соединены с первыми входами устройства, вторые входы - с соответствующими выходами блока для образования дополйительных сумм, а выходы - через элемент ИЛИ со вторым выходом устройства. Ка первые входы устройства поступают значения основных сумм, на вторые входы - входные операнды, а на третьи входы - перенос с предыдущих разрядов. При несовпадении значений основных и дополнительных сумм вырабатывается сигнал ошибки 2.

Недостатками устройства являются относительная сложность, определяемая тем, что производится сравнение всех разрядов конечных сумм , и относительно низкая эффективность контроля, так как неисправности в самой схеме контроля, точнее во вторых схемах сложения по модулю два и в элемент ИЛИ, приведут к потере сигнала ошибки.

Цель изобретения - упрощение устройства.

Поставленная цель достигается тем что в устройство для контроля сумматора, содержащее первый блок сложения по модулю два, элемент ИЛИ, блок

формирования дополнительных сумм и группу схем сравнения, п входов первого блока сложения по модулю дьа соединены с выходами суммы контролируемого сумматора, информационные входь блока формирования дополнительных сумм соединены со входами операндов сумматора вход переноса с предьщущих разрядов сумматора является управляющим входом устройства, выход первого блока сложения по модулю два является первым, выходом устройства, выход элемента ИЛИ является вторьвл выходом устройства, выходы-кашдой схемы сравнения группы соединены с соответствующим входом элемента .ИЛИ, введен второй блок сложения по модулю два, выход которого соединен с (п+1)-м входом первого блока сложения по модулю два, каждый нечетный выход блока формирования дополнительной суммы соединен с liepвым входом соответствующей схемы сравнения, второй вход каждой схемы сравнения соединен с соответствующим нечетным выходом суммы контролируемого сумматора, выход блока формирования дополнительных сумм соединен с соответствующим входом второго блока сложения по модулю два.

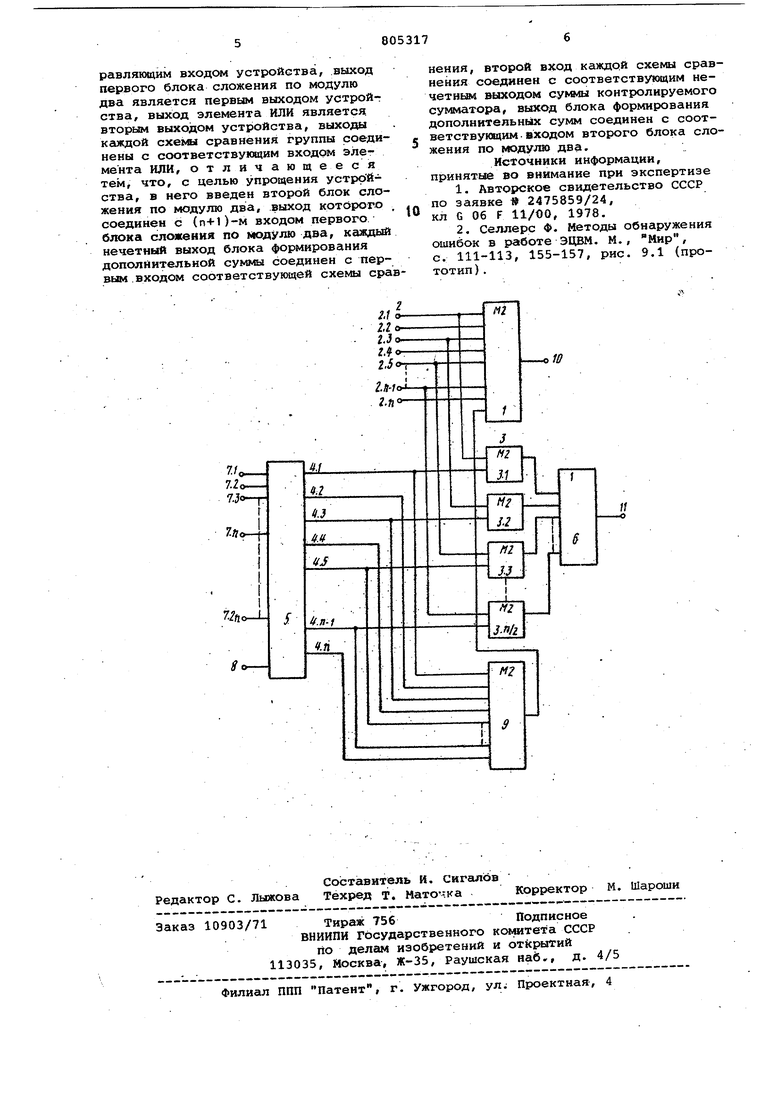

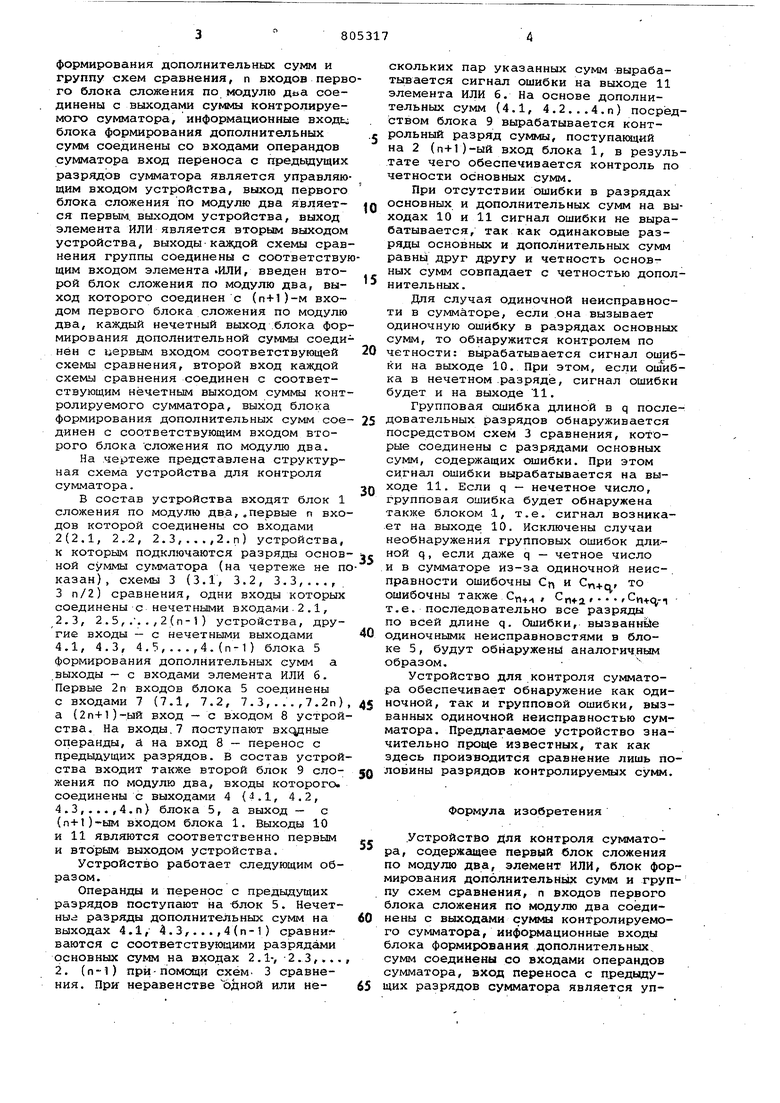

На чертеже представлена структурная схема устройства для контроля сумматора.

В состав устройства входят блок 1 сложения по модулю два,„первые п входов которой соединены со входами 2(2.1, 2.2, 2.3,...,2.п) устройства, к которым подключаются разряды основной суммы сумматора (на чертеже не показан) , схемы 3 (3.1, 3.2, 3.3,..., 3 п/2) сравнения, одни входы которых соединены-с нечетными входами-2.1, 2,3, 2 . 5, .. . , 2(п-1) устройства, другие входы - с нечетными выходами 4.1, 4.3, 4.5, ., . ,4.(п-1) блока 5 формирования дополнительных сумм а выходы - с входами элемента ИЛИ б. Первые 2п входов блока 5 соединены с входами 7 (7.1, 7.2, 7.3,...,7.2п) а (2п+1)-ый вход - с входом 8 устройства. На входы,7 поступают входные операнды, а на вход 8 - перенос с предыдущих разрядов. В состав устройства входит также второй блок 9 сложения по модулю два, входы которого, соединены с выходами 4 (4.1, 4.2, 4.3,...,4.п) блока 5, а выход - с (п+1)-ым входом блока 1. Выходы 10 и 11 являются соответственно первым и вторым выходом устройства.

Устройство работает следующим образом.

Операнды и перенос с предьвдущих разрядов поступают на -блок 5. Нечетны -г разряды дополнительных сумм на выходах 4.1, 4. 3,. .., 4 (п-1 ) сравнит ваются с соответствующими разрядами основных сумм на входах 2.1-, -2.3,... 2. (п-1) при-помощи схеМ 3 сравнения. При неравенстве одной или нескольких пар указанных сумм -вырабатывается сигнал ошибки на выходе 11 элемента ИЛИ б. На основе дополнительных сумм (4.1, 4.2...4.П) посредством блока 9 вырабатывается контрольный разряд суммы, поступающий на 2 (п-И)-ый вход блока 1, в результате чего обеспечивается контроль по четности основных сумм.

При отсутствии ошибки в разрядах основных и дополнительных сумм на выходах 10 и 11 сигнал ошибки не вырабатывается, так как одинаковые разряды основных и дополнительных сумм равны друг другу и четность основных сумм совпадает с четностью дополнительных.

Для случая одиночной неисправности в сумматоре, если .она вызывает одиночную ошибку в разрядах основных cyiviM, то обнаружится контролем по четности: вырабатывается сигнал ошибки на выходе 10. При этом, если ошибка в нечетном .разряде, сигнал ошибки будет и на выходе 11.

Групповая ошибка длиной в q последовательных разрядов обнаруживается посредством схем 3 сравнения, которые соединены с разрядами основных сумм, содержащих сииибки. При этом сигнал ошибки вырабатывается на выходе 11. Если q - нечетное число, Групповая ошибка будет обнаружена также блоком 1, т.е. сигнал возникает на выходе 10. Исключены случаи необнаружения групповых ошибок длиной q, если даже q - четное число и в сумматоре из-за одиночной неис-. правности ошибочны С и , то ошибочны также С„+ , С, , .. . ,С„.ц,-1 т.е. последовательно все разряды по всей длине q. Ошибки, вызванное одиночными неисправновстями в блоке 5, будут обнаружень аналогичным образом.

Устройство для контроля сумматора обеспечивает обнаружение как одиночной, так и групповой ошибки, вызванных одиночной неисправностью сумматора. Предлагаемое устройство значительно проще известных, так как здесь производится сравнение лишь половины разрядов контролируемых сумм.

Формула изобретения

.Устройство для контроля сумматора, содержащее первый блок сложения по модулю два, элемент ИЛИ, блок формирования дополнительных сумм и группу схем сравнения, п входов первого блока сложения по модулю два соединены с выходами суммы контролируемого сумматора, информационные входы блока формирования дополнительных сумм соединены со входами операндов сумматора, вход переноса с дредыдущих разрядов сумматора является управляющим входом устройства, выход первого блока сложения по модулю два является первым выходом устроит ства, выход элемента ИЛИ является вторым выходом устройства, выходы кгикдой схемл сравнения группы соединены с соответствукицим входом элемента ИЛИ, отличающееся тем что, с целью упрощения устройства, в него введен второй блок сложения по модулю дв1а, выход которого соединен с (п+1)-м входом первого блока сложения по модулю два, каждый нечетный выход блока формирования дополнительной суммы соединен с первым.входом соответствующей схемы сра нения, второй вход каждой схемы сравнения соединен с соответствующим нечетньм выходом сумма контролируемого сув«иатора, выход блока формирования дополнительных сумм соединен с соответствующим входом второго блока сложения по 1«}дулю два. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР по заявке 2475859/24, кл G 06 Г 11/00, 1978, 2.Селлерс Ф. Методы обнаружения ошибок в работе ЭЦВМ. М., Мир, с. 111-113, 155-157, рис. 9.1 (прототип) .

Авторы

Даты

1981-02-15—Публикация

1978-06-01—Подача