n-f -t- i I г я I г II

U

LJ.L|J4- -U -J

74

V

СО

00

ел

fl33db&

г г л ГЛ/ w I «f I 1

I- ГД лг I л/ I га Jf Jf J

Л|

Фиг.1

п

3149

Изобретение относится к автоматике и вычислительной технике и может бьпъ использовано при построении надежных цифровых блоков..

Целью изобретения является рас- ширение области применения устройства.

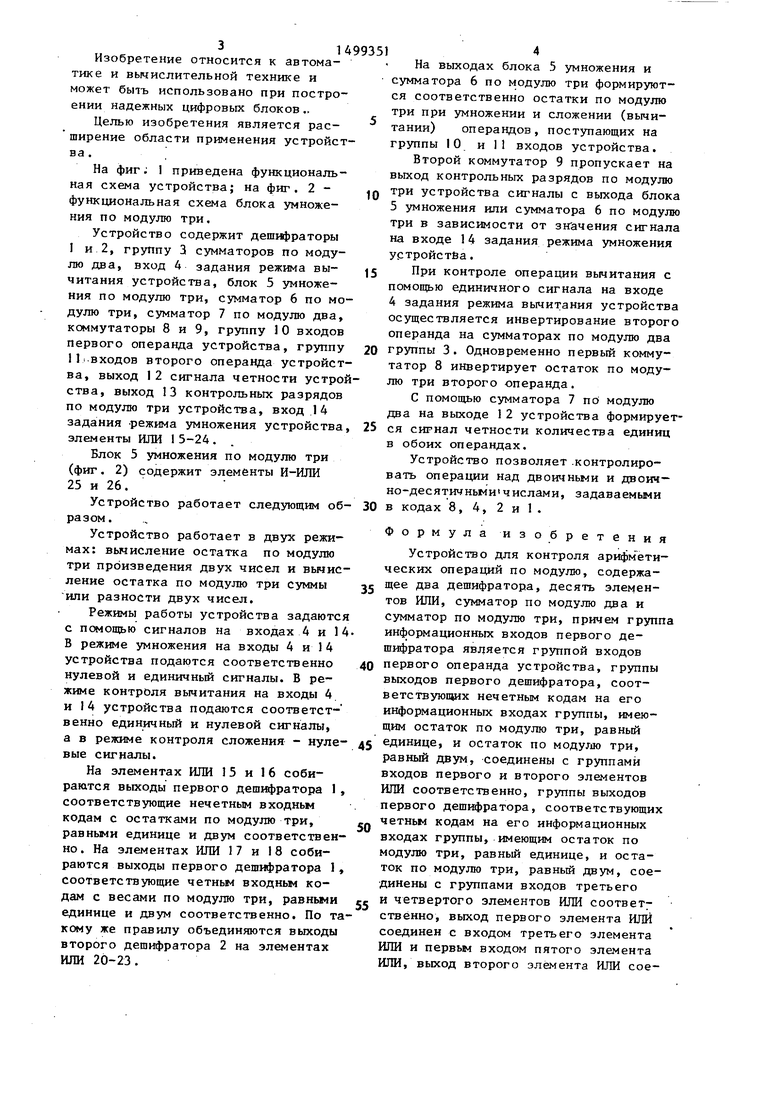

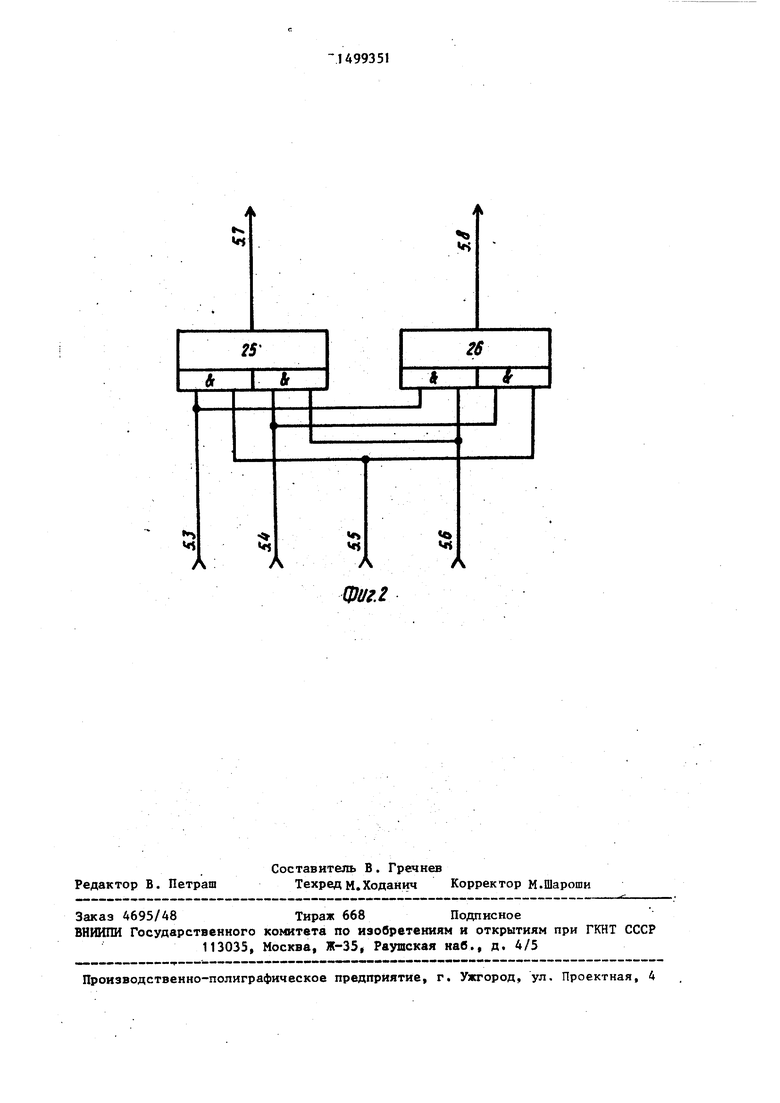

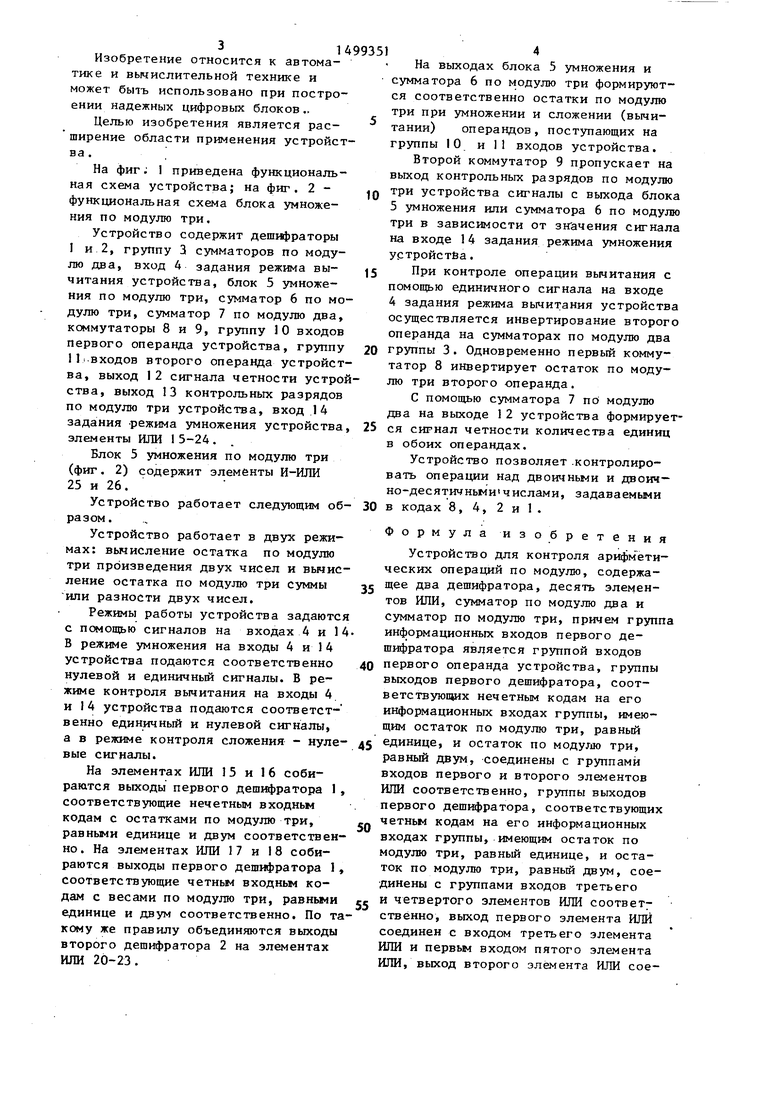

На фиг; 1 приведена функциональная схема устройства; на фиг. 2 - функциональная схема блока умножения по модулю три.

Устройство содержит дешифраторы I и 2, группу 3 сумматоров по модулю два, вход 4 задания режима вычитания устройства, блок 5 умножения по модулю три, сумматор 6 по модулю три, сумматор 7 по модулю два, коммутаторы 8 и 9, группу 10 входов первого операнда устройства, группу Mi.входов второго операнда устройства, выход I 2 сигнала четности устройства, выход 13 контрольных разрядов по модулю три устройства, вход 14 задания -режима умножения устройства, элементы ИЛИ 15-24.

Блок 5 умножения по модулю три (фиг. 2) содержит элементы И-ИЛИ 25 и 26.

Устройство работает следующим об- разом.

Устройство работает в двух режимах: вычисление остатка по модулю три произведения двух чисел и вьнис- ление остатка по модулю три суммы или разности двух чисел.

Режимы работы устройства задаются с псмощью сигналов на входах 4 и 14 В режиме умножения на входы 4 и 1 4 устройства подаются соответственно нулевой и единичньй сигналы. В режиме контроля вычитания на входы 4 и 14 устройства подаются соответст- венно единичный и нулевой сигналы, а в режиме контроля сложения - нуле- вые сигналы.

На элементах ИЛИ 15 и 16 соби- рак1тся выходы первого дешифратора I , соответствующие нечетным входньм кодам с остатками по модулю три, равными единице и двум соответственно . На элементах ИЛИ 17 и 18 собираются выходы первого дешифратора 1 , соответствующие четньм входным кодам с весами по модулю три, равньии единице и двум соответственно. По такому же правилу объединяются выходы второго дешифратора 2 на элементах ИЛИ 20-23.

0

5

0

51

5

0

5

0 Б

j

0

На выходах блока 5 умножения и сумматора 6 по модулю три формируются соответственно остатки по модулю три при умножении и сложении (вычитании) операндов, поступающих на группы 10 и 11 входов устройства.

Второй коммутатор 9 пропускает на выход контрольных разрядов по модулю три устройства сигналы с выхода блока 5 умножения ипи сумматора 6 по модулю три в зависимости от значения сигнала на входе 14 задания режима умножения устройстйа.

При контроле операции вьнитания с помощью единичного сигнала на входе 4 задания режима вычитания устройства осуществляется инвертирование второго операнда на сумматорах по модулю два группы 3. Одновременно первый коммутатор 8 инвертирует остаток по модулю три второго операнда.

С помощью сумматора 7 по модулю два на выходе 12 устройства формируется сигнал четности количества единиц в обоих операндах.

Устройство позволяет .контролировать операции над двоичньми и двоич- но-десятичньми числами, задаваемыми в кодах 8, 4, 2 и 1.

Формула изобретения

Устройство для контроля арифметических операций по модулю, содержащее два дешифратора, десять элементов ИЛИ, сумматор по модулю два и сумматор по модулю три, причем группа информационных входов первого дешифратора является группой входов первого операнда устройства, группы выходов первого дешифратора, соот- ветствую1цих нечетным кодам на его информационных входах группы, имеющим остаток по модулю три, равный единице, и остаток по три, равный двум, соединены с группами входов первого и второго элементов ИЛИ соответственно, группы выходов первого дешифратора, соответствующих четньм кодам на его информационных входах группы, имеющим остаток по модулю три, равный единице, и остаток по модулю три, равньй двум, соединены с группами входов третьего и четвертого элементов ИЛИ соответ7 ствённо, выход первого элемента ИЛИ соединен с входом третьего элемента ИЛИ и первьм входом пятого элемента ИЛИ, выход второго элемента ИЛИ соединен с входом четвертого элемента ИЛИ и вторьм.входом пятого элемента ИЛИ, выход которого соединен с пер- вьм входом сумматора по модулю два, выходы третьего и четвертого элементов ИЛИ соединены с соответствующими входами первой группы сумматора по модулю три, группы выходов второго дешифратора, соответствующих нечет- ньм кодам на его информационных входах группы, имеющим остаток по модулю три, равный единице, и остаток по модулю три, равный двум, соединены с группами входов шестого и седьмого элементов ИЛИ соответственно, группы выходов второго дешифратора, соответствующих четньм кодам на его ин- формационньпс входах группы, имеющим остаток по модулю три, равный единице, и остаток по модулю три, равный двум, соединены с группами входов восьмого и девятого элементов ИЛИ соответственно, выход шестого элемента ИЛИ соединен с соответствующим входом восьмого элемента ИЛИ и пер- вьм входом десятого элемента ИЛИ, выход седьмого элемента ИЛИ соединен с соответствующим входом девятого элемента ИЛИ и вторьм входом десятого элемента ИЛИ, выход которого соединен с вторым входом сумматора по модулю два, отличающее- с я тем, что, с целью расширения области применения устройства, в него введены группа сумматоров по модулю два, блок умножения по модулю три и два коммутатора, причем

первые входы сумматоров по модулю два группы образуют группу входов второго операнда устройства, выходы сумматоров по модулю два группы со- . единены с группой информационных входов второго дешифратора, выходы третьего и четвертого элементов ИЛИ соединены с первой группой информа0 ционных входов блока умножения по модулю три, выходы восьмого и девятого элементов ИЛИ соединены соответственно с первьм и вторым информационными входами первой группы пер5 вого коммутатора, выходы девятого и восьмого элементов ИЛИ соединены соответственно с первым и вторьм информационными входами второй группы первого коммутатора, группа выхо0 дов которого соединена с второй группой входов сумматора по модулю три и с второй группой информационных входов блока умножения по модулю три, выходы блока умножения по модулю

5 три и сумматора по модулю три соединены соответственно с первьм и вторьм информадионньми входами второго коммутатора, выход которого является выходом контрольных разрядов по

0 модулю три устройства, выход сумматора по модулю два является выходом сигнала четности устройства, управляющий вход первого коммутатора подключены к входу задания режима вьми5 тания устройства, управляющий вход второго коммутатора подключен к входу задания режима умножения устройства.

ф1/г.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Устройство для контроля умножения по модулю три | 1982 |

|

SU1072049A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для сложения и вычитания чисел по модулю | 1990 |

|

SU1755275A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1988 |

|

SU1621182A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ЧИСЕЛ ПО МОДУЛЮ | 1998 |

|

RU2145112C1 |

| Арифметическое устройство | 1979 |

|

SU849206A2 |

| Устройство диагностики многопроцессорного вычислительного комплекса | 1988 |

|

SU1548792A1 |

| Матричное устройство для умножения | 1979 |

|

SU842800A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ЧИСЕЛ ПО МОДУЛЮ | 1991 |

|

RU2018935C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении надежности цифровых блоков. Цель изобретения - расширение области применения устройства. Устройство содержит дешифраторы 1,2, группу 3 сумматоров по модулю три, блок 5 умножения по модулю три, сумматор 6 по модулю три, сумматор 7 по модулю два, коммутаторы 8,9, элементы ИЛИ 15 - 24. Устройство позволяет формировать на выходе 13 устройства остаток по модулю три произведения, суммы и разности чисел, подаваемых на группы 10,11 входов первого и второго операндов устройства. Управление режимом работы устройства осуществляется с помощью сигналов, поступающих на входы 4,14 задания режимов вычитания и умножения устройства соответственно. На выходе 12 сигнала четности устройства формируется сигнал четности двух чисел. 2 ил.

| Устройство для контроля умножения по модулю три | 1982 |

|

SU1072049A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля информации по модулю | 1985 |

|

SU1285480A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-07—Публикация

1987-04-17—Подача