(54) СУММИРУЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2022339C1 |

| ОДНОКАНАЛЬНЫЙ КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ЧАСТОТНЫХ ИСКАЖЕНИЙ | 2009 |

|

RU2393491C2 |

| Универсальный операционный блок | 1990 |

|

SU1714585A1 |

| Микропроцессор | 1977 |

|

SU717772A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| УСКОРЕННЫЙ УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2006 |

|

RU2322688C2 |

| Устройство для алгебраического сложения чисел | 1986 |

|

SU1339552A1 |

| Последовательный сумматор | 1989 |

|

SU1709298A2 |

| Вычислительное устройство | 1988 |

|

SU1647553A1 |

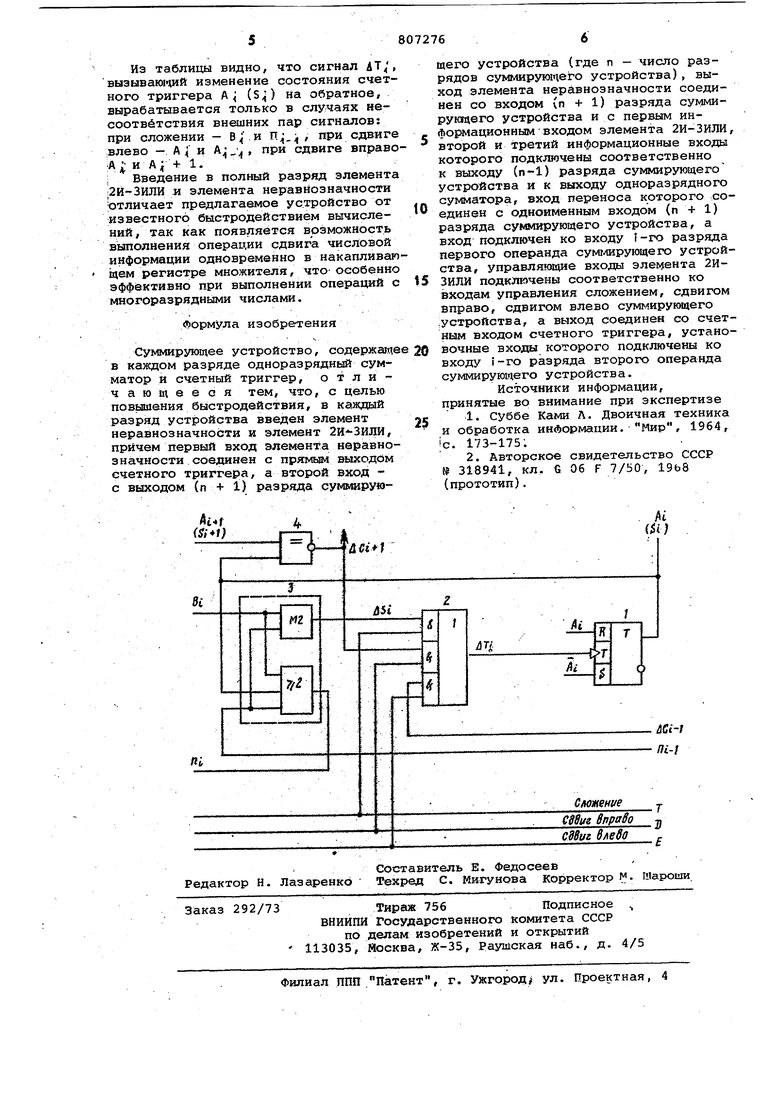

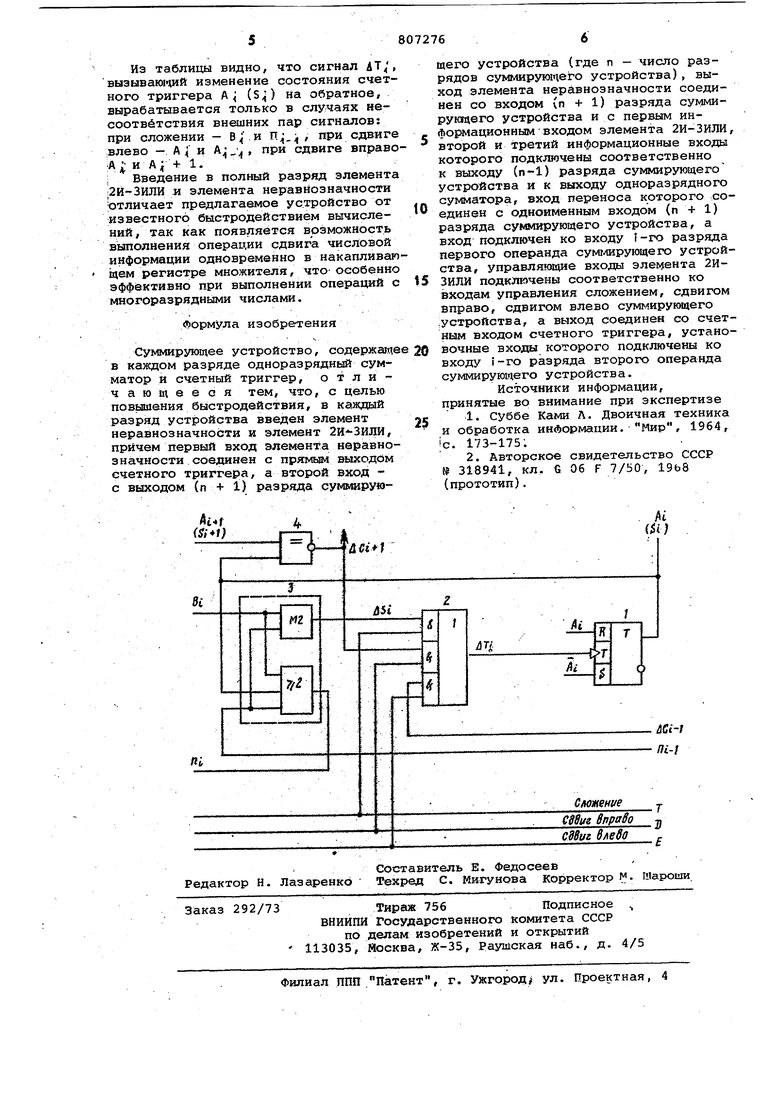

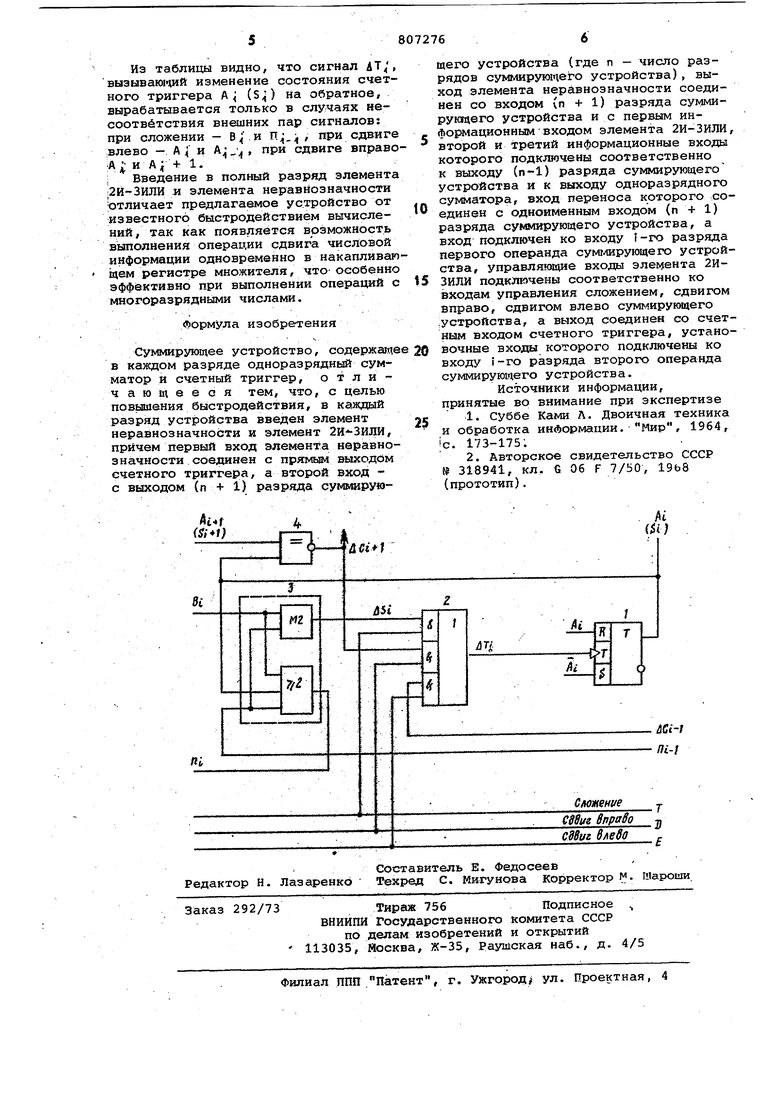

Изобретение относится к цифровой вычислительной технике и может быть использовано в составе арифметических устройств ЦВМ. Известно суммирующее устройство со сдвигом, содержащее сугучмируютдий регистр, сумматор-вычислитель и промежуточный регистр, В суммируклцем регистре применен триггер типа RST, у которого счетный вход используется только при сдвиге информации, а уста новочные входы с помощью логической схемы типа 2И-4ИЛИ служат для записи информации с промежуточного регистр при организации кольца, с кодовых шин при приеме внешней информации, со смежных разрядов суммирующего регистра при выполнении сдвигов влево или вправо. Таким образом, сам регистр служит для приема, хранения, накопления информации и сдвига накопленной суммы. Суммирование (вычи тание) производится сумматором-вычи тателем. Накопленная сумма со сдвиг влево или вправо получена путем сое динения суммирующего регистра с сум матором- вычит-ател ем, включенным в цепь, идущую с выхода регистра на его вход 1Q . Однако такая схема замкнутой петли предполагает наличие.в ней дополнительного регистра, служащего для сохранения сигналов на входах суммирующего регистра на время перезаписи суммы, что уменьшает скорость вычис:лений. Наиболее близким по технической сущности к предлагаемому является суммирующее устройство, содержащее 3 каждом разряде одноразрядный сумматор и счетный триггер. Кроме того устройство содержит установочнь1е вентили, элементы И, ИЛИ, НЕ 2J. Однако известное устройство отличается низким быстродействием. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в суммирующее устройство, содержащее в каждом разряде одноразрядный сумматор и счетный триггер введены элемент неравнозначности и элемент 2И-ЗИЛИ, причем первый вход элемента неравнозначности соединен с прямым ;выходом счетного триггера, а второй вход - с выходом (п + 1) разряда суммирующего устройства (где п - число разрядов суммирующего устройства), выход элемента неравнозначности соединен со входом (п +1) разряда суммирующего устройства и с первым инЛо;. мационным входом элемента 2И-ЗИЛИ, второй и третий информационные входы которого подключены соответственно к выходу (п-1) разряда суммирующего устройства и к выходу одноразрядного сумматора, выход переноса которого соединен с одноименным входом (п + 1) разряда суммирующего устройства, а вход подключен ко входу i-ro разряда первого операнда суммирующего устройства, управляющие входы элемента 2ИЗИЛИ подключены соответственно ко вхо дам управления сложением, сдвигом вправо, сдвигом влево суммирующего устройства, а выход соединен со счет ным входом счетного триггера, устано вочные входы.которого подключены ко входу i-ro разряда второго операнда суммирующего устройства. На чертеже представлена схема i-г разряда суммирующего устройства. Устройство содержит счетный триггер 1/ элемент 2И-ЗИЛИ 2, одноразрядный сумматор 3, элемент 4 неравно значности. В счетном триггере применен триггер типа RST, у которого установочны входы используются для парафазного приема исходной цифры операнда А (А), а счетный вход используется дважды при сложении с цифрой операнда В и при сдвиге результата суммирования S. Элемент 2И-ЗИЛИ в цепи счетного входа счетного триггера вырабатывает раздельно сигнал дополнения до полной суммы в регистре Л S , или сигналы неравнозначности к преды дущему iC4-,( , или к последующему зависимости от сигнала разрешения в одной из шин управ ления сложением Т, сдвигом влево Е и сдвигом вправо О, Работа логических элементов опиЬывается следующими выраже,ниями: 2И-ЗИЛИ Д т; + + . EJ US. . + . ; сумматор П 4 А - В .п., элемент неравнозначности дС + - . i 1 Операция сложения операндов А и В, для случая A.i С9ответствует логической 1, Bjf - i и пА.- С, выполняются путем выработки схемой сло7 жения по модулю 2 сигналов В и П. результата АS|, равного 1, который через 2И-ЗиЛИ при наличии разрешающего сигнала Т поступает на счетный вход триггера , изменяя его состояние на О, рри этом схема логического порога на 2 вырабатывает сигнал переноса П| в последующий разряд . равный 1, i Операции сдвига влево операнда Л для случая А - 1 и А - О выполняется путем выработки элементом Неравнозначности сигналов А) и А, результата &. , равного 1, который через элемент 2V, -ЗИЛИ при наличии разрешающего сигнала Е поступает на счетный вход счетнсэго триггера А| изменяя его состояние jHa О. Операция сдвига вправо операнда А выполняется аналогично сдвигу влево, путем выработки, элементом неравнозначности результата поступающего на триггер А через элемент 2И-ЗИЛИ при наличии Сигнала D, устройства Работа суммирующего при других возмохсных комбинациях внешних сигналов представлена в таблице .соответствия. |

Авторы

Даты

1981-02-23—Публикация

1979-04-11—Подача