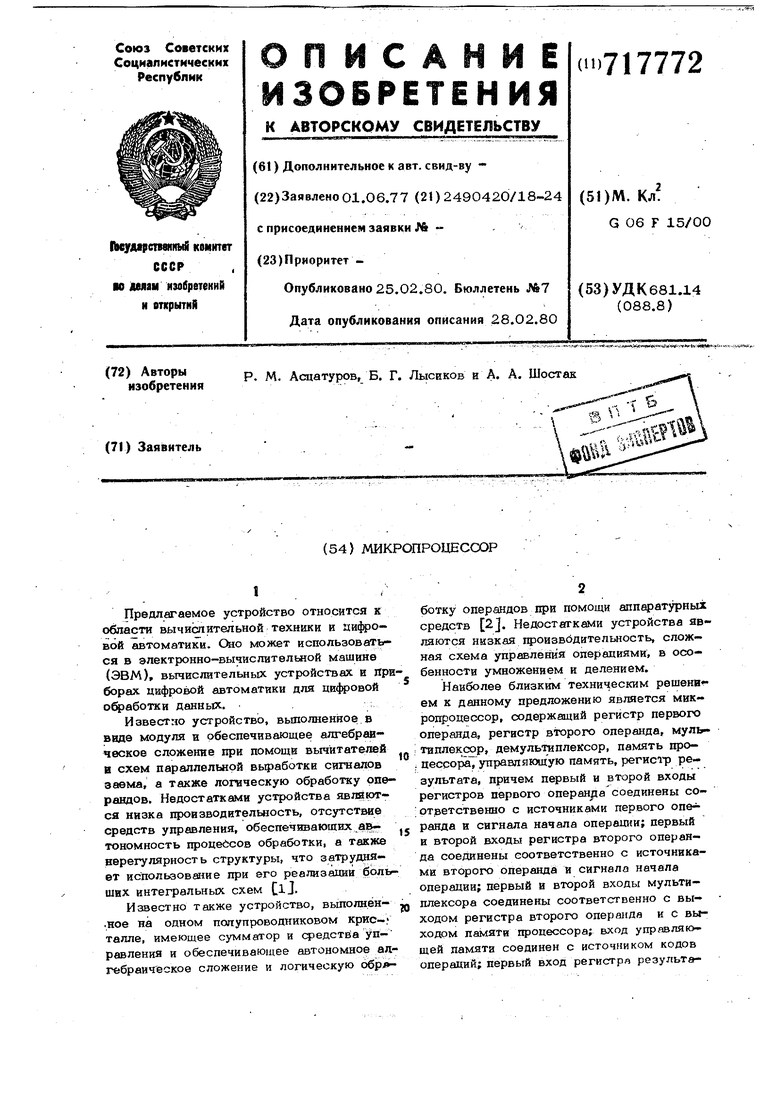

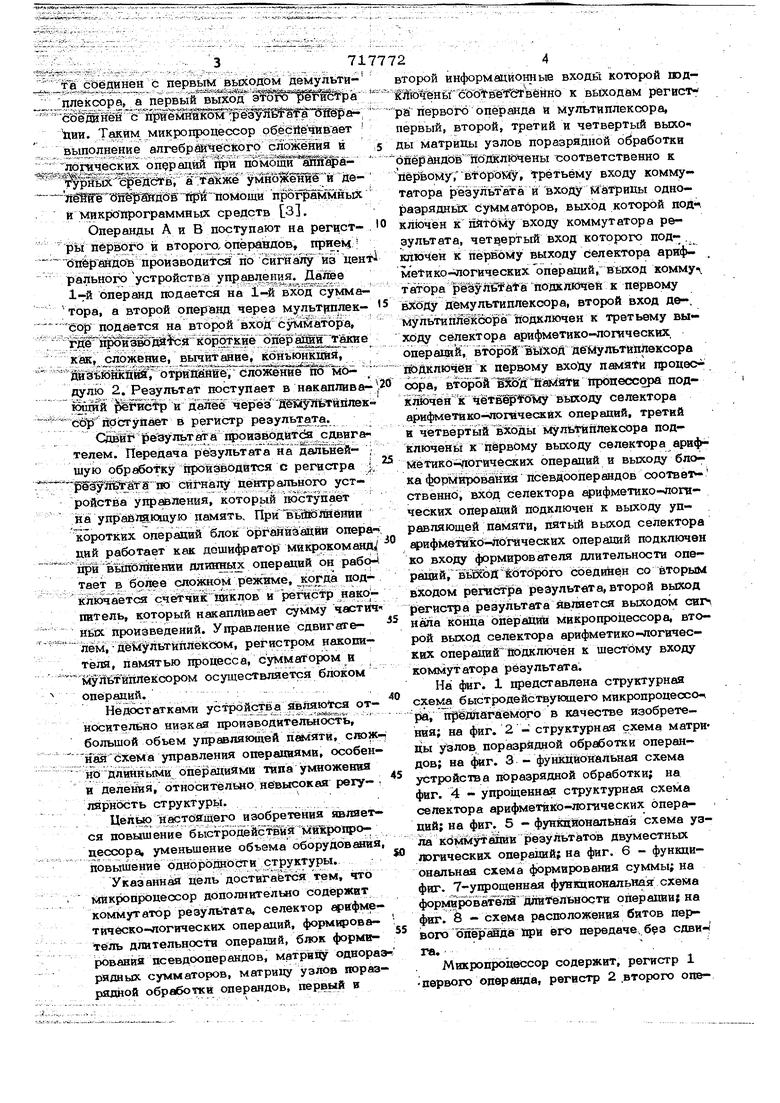

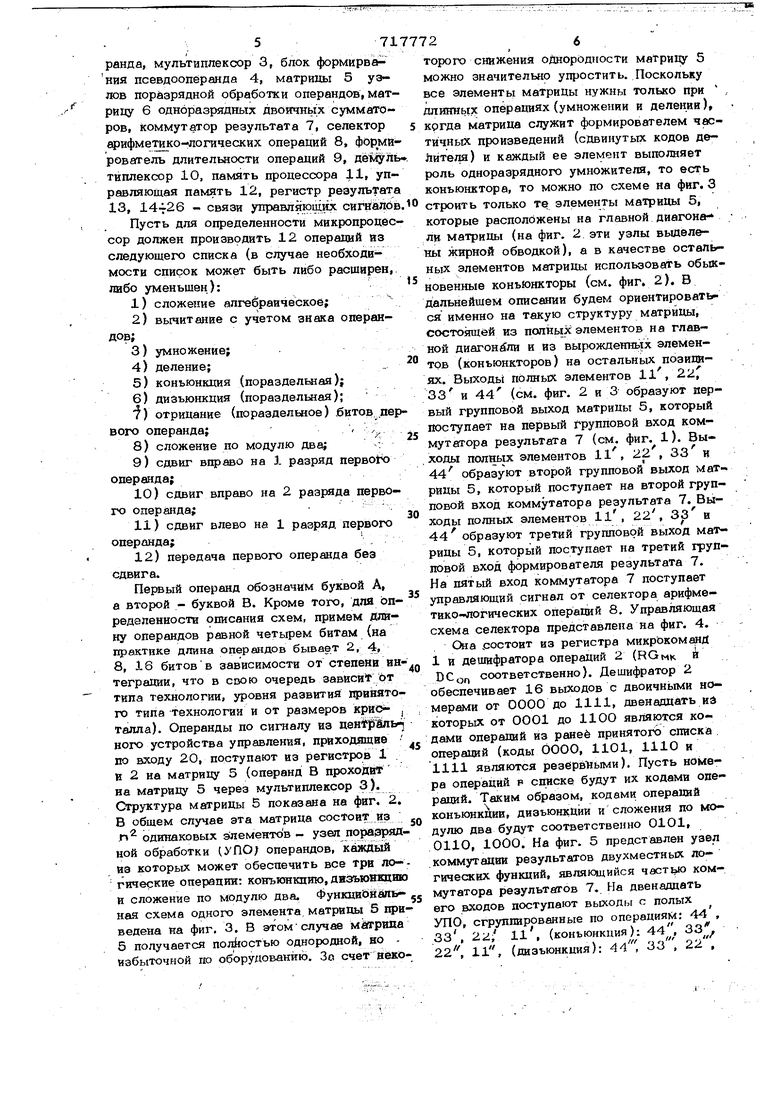

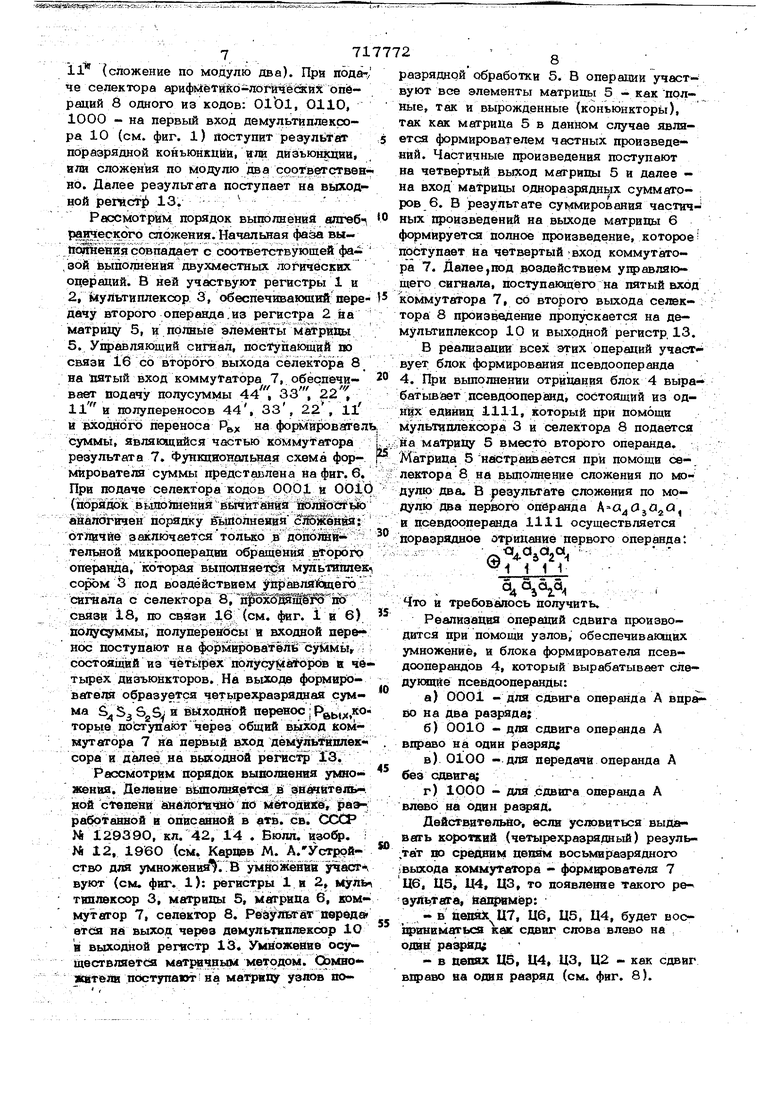

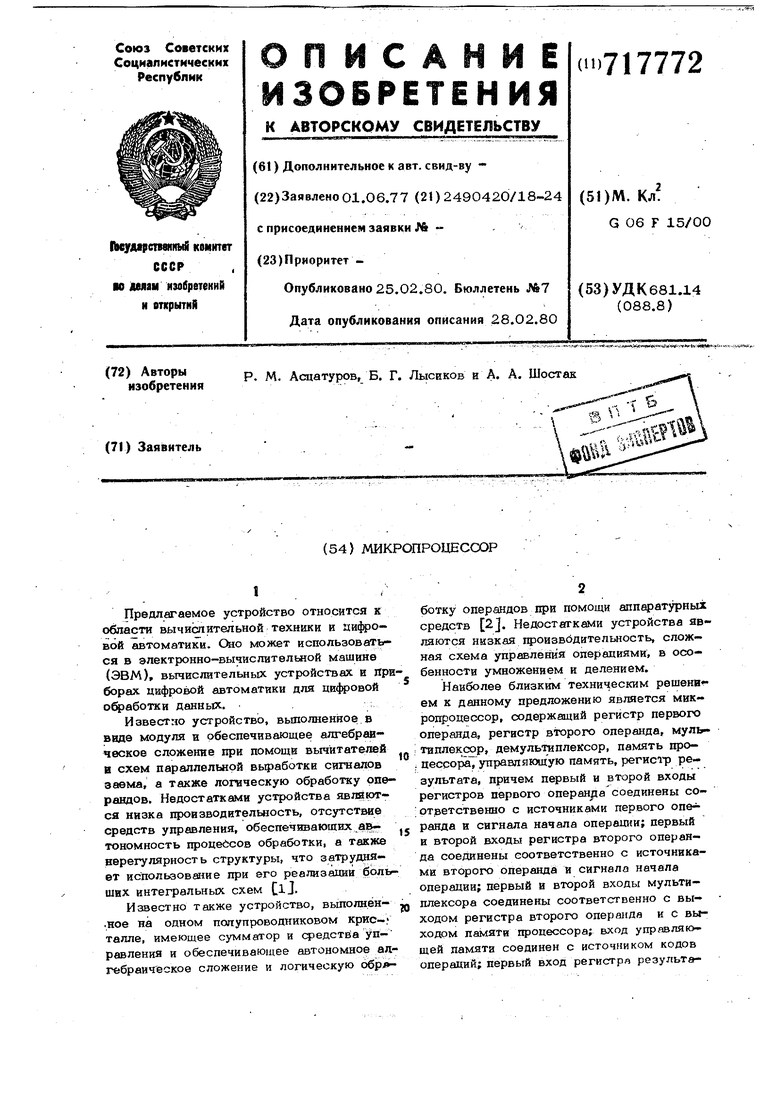

(54) МИКРОПРОЦЕССОР та соединен с первым выходом демульти i ., -ii -,-4,-jv - -«яда ьг иеиййлаи- дь.- -. плексора, a первый выход этогоПрегиа-ра Ли1СЛ чурся « . , сбе данён с HpVeMiJa SrpelSfnSfafa ffepaпии. Таким микропроцессор обесйечивает выполнение алгебраического сложения и t - tf h+ - jferte™,. логических операций При помощи пара p bix UcJTB, а Также умножениё и делёНГеШ ТШгдов Т1рй помощи программных И микркупрограммных средств З. Операнды Аи В поступают на регистliibi пёрвЬго и второго, операндов, приеЦ опёрйндов производится по сигнал из ценТД рольного устройства управления. Д(аШе 1-й операнд подается на I-и вход сум суммаперанд подается на J.-M BA«JM v,jri«i«cia второй операнд через мультрплек ТОра, - ., . .-,.-.-.-,,-.,.-„,вь,,„:,;4 г - -. ;,-v ,: .:.-- л,-л-г::,-:- ;.ч;А;-: : Шр подается на второй вход сумматора, тЗда л биЩШаЗтШ кор кие кик, сгюжение, вычиТ е, ШМыйя, Ш йШШШ7 {ШйШ Вложение Ш моаййШМкйия.оТрйцШйё, сложение по . зультат поступает в накапливаiimm S S . е рпосггупаёт в регистр результ;ата. Сдвй 1рё ЗультЙа П рс извсЩ1а телем. Передача результатана д;альней- ; Шую обработку производится с регистра р зулегата по сигналу центрального устройства у пршленйя, который поступает на управта ющую память. При Ъьйюлнении коротких операций блок организация операций работает как дешифратор микрокоманд при вьшолнении длинных операций он рабсЯ тает в более сложном режиме, „когда подключается счетчик 1ШКЛОВ и регистр нако питель, который накапливает сумму частич HKix произведений. Управление сдвигаге лем,-дё1 ультипЛёксом, регистром накопителя, памятью процесса, сумматором и ЙуЖт йпЛёксором осуществляется блоком операций. Недостатками устроЙс в|1 явя носительйо низкая производительность, большой объем управляющей памяти, стаж -н йсХёМа управления операциями, особен Й5 ДЛИННЫМИ операциями типа умножения и деления, относительно невысокая регулярность структуры. Цепью; настоящего изобретения является повышение быстрБдейШйй Шкропроцессора. уменьшение объема оборудования повышение однор011ности;структуры. Указанная Цель Достигается тем, что микропроцессор дополнительно содержит коммутатор результата, селектор ернфме тичёско огических операций, формирователь длительнсзсти операций, блок формирования цсевдооперандов, матрицу однора рядных сумматоров, матрицу узлов пораз рядной обработай операндов, первый и 717 4 торой информационные входы которой пэдёШнйГсШтвШ ГвёНнЬ к вЬ1ход ам региста первого операнда и мультиплексора, ервый, второй, третий и четвертый выхо ы матрицы узлов поразрядной обработки пёрМдЬё пблЗкЛ10Чень1 соответственно к ё1)вому, бТоройу, Третьему входу коммуатора результаТа и BXbf МГатрицы одно- аарядньгх бумматбров, выход которой подч лючен к ййТШу входу коммутатора результата, четв.ертый вход которого под- , лючен к пёрвбму выходу селектора арнф меТико-чюгических операций,: выход коммул. татора pts nibfйТа ПоДкдЮчёй к первому . „,., , оду демультиплексора, второй вход д. йультийШйьора подключен к третьему выiaw,,.-rte 54 -i- ri« irTnptKntt tIftH К ТОВТЬеМУ ВЫ- ходу селектора арифметико-логических, операшй7 втфой тгхъд Мйультиплексора Шдкпючён к первому вхоДу памяти процес .. --- -- сора. втбрБй Wt ШйТй ТфОПёСсо ра подЙШчёГк вшоду селектора П... д. шъ .-«-«.. . о АмАтико-логическйх операций, третий арифметико-логических операций, третий в четвертый Входы мультиплексора подключены к первому выходу селектора арифйёТико- огических операций и выходу блока формирования псевдооперандов соответ ствённо, вход селектора арифметико-логических операций подключен к выходу управляющей памяти, цятьхй выход селектора арифмётйХО-ЯОгйчёских операций подключен ко входу формйроввгеля длительности операций, вьШэД&ото рого сОёди1аен со вторым входом регистра результвта, второй выход регистра результата является выходом си1 нала конца Опёраиш микропроцессора, второй выход селектора арифметико-логических операций подключен к шестОму входу коммуТатора результата. На фиг. 1 цредставлена структурная схема быстродействукяцего микpoпpoцecco jja, йрёВЙагЯёмОгЬ в качестве изобретения; на фиг. 2 - структурная схема матрицы узлов поразрядной обработки операндов; на фиг. 3 - функциональная схема устройства поразрядной обработки; на фиг. 4 - упрощенная структурная схема Селектора арифмётик;о-/югических операций; на фиг. 5 - функциональная схема узла кйЩ уТШ1йи|рёйуЛЬТйт6в двуместных логических операгшй; на фиг. 6 - функциональная схема формирования суммы; на фиг. 7-у1фощенная (нональная схема формирователю ДшТёЛЬнООТй операцйи{ на фиг. 8 - схема расположения битов первого оперЖДа йри его передаче, сдви- га. - . Микропроцессор содержит, регистр 1 первого опер«Ийда, регистр 2 .второго one;57ранда, мультиплексор 3, блок формирвания псевдоопёранда 4, матрицы 5 узлов поразрядной обработки операндов, мат рицу 6 одноразрядных двоичных сумматоров, коммутатор результата 7, селектор ифметико-логических операций 8, форми рователь длительности операций 9, деЩл тйплексор 10, память процессора 11, управляющая память 12, регистр результат 13, 14-;.26 - связи управляющих сигнало Пусть для определенности микропроцес сор должен производить 12 операций аз следующего списка (в случае необходимости список может быть либо расширен, пибо уменьшен): 1)сложение алгеёраическоб; 2)вычитание с учетом знака операндов;3)умножение; 4)деление; 5)конъюнкция (поразделшая); 6)дизъюнкция (пораздельная); 7)отрицание (пораздельное) битов пер вого операнда;, : V 8)сложение по модулю два;-i 9)сдвиг вправо на 1 разряд nepBOtX) операнда; 10)сдвиг вправо на 2 разряда перво- гю операнда;11)сдвиг влево на 1 разряд первого операнда; 12)передача первого операнда без сдвига. Первый операнд обозначим буквой А, а второй - буквой В. Кроме того, для опредаленности описания схем, примем длину операндов равной четырем битам (на практике длина операндов бьшает 2, 4, 8, 16 битов в зависимости от степени интеграции, что в свою очередь зависи 6т типа технологии, уровня развития принятого типа технологии и от размеров j талла). Операнды по сигналу из ного устройства управления, приходящие по входу 20, поступают из регистров 1 в 2 на матрицу 5 (операнд В проходит на матрицу 5 через мультиплексор 3). Структура матрицы 5 показана на фиг4 2. В общем случае эта матрица состоит из п одинаковых элементов - узел поразрядной обработки (УПО; операндов, каждый из которых может обеспечить все три ло-гические операции: конъюнкцию, дизъюнкцию и сложение по модулю два. ФункциЬЙйп ная схема одного элемента, матрицы 5 1фиведена на фиг, 3. В этом случае мйтрида 5 получается полйостью однородной, нО избыточной гю оборудованию. Зо счет вёко72торого снижения ойнородиости матрицу 5 можно значительно упростить. Поскольку все элементь матрицы нужны только при , длиннызс операциях (умножении и делении), когда матрица служит формирователем частичных произведений (сдвинутых кодов делителя) и каждый ее элемент выполняет роль одноразрядного умножителя, то есть конъюнктора, то можно по схеме на фиг. 3 строить только те элементы матрицы 5, которые расположены на главной диагонали Матрицы (на фиг. 2 эти узлы выделены жирной обводкой), а в качестве остальных элементов матрицы использовать обыкновенные коныонкторы (см. фиг, 2). В дальнейшем описании будем ориентировать ся именно на такую структуру матрицы, состоящей из полных элементов на главной диагонйли и из вырожденньтх элементов (конъюнкторов) на остальных позициях/Выходы полных элементов И , 22 33 и 44 (см. фиг. 2 и 3 образуют нервый групповой выход матрицы 5, который поступает на первый групповой вход коммутатора результата 7 (см. фиг. 1). Выходы полнь1Х элементов 11 , 22 , 44 образуют второй групповой выход матрицы 5, который поступает на второй групповой вход коммутатора результата 7. Выходы полных элементов 11 , 22/, 33 и 44 образуют третий групповой выход матрицы 5, который поступает на третий групповой вход формирователя результата 7. На пять1й вход коммутатора 7 поступает управляющий сигнал от селектора арифметико-логических операшй 8. Управляющая схема селектора представлена на фиг. 4. Она состоит из регистра микрокоманд 1 и дешифратора операций 2 (НОмк и DCQ, соответственно). Дешифратор 2 обеспечивает 16 выходов с двоичньгми номерами от 0000 до 1111, двенадцать ий которых от 0001 до 110О являются кодами операций из ранее принятого списка операций (коды ОООО, 1101, 1110 и 1111 являются резбрвными). Пусть номера операций Р списке будут их кодами операций. Таким образом, кодами операций конъюнк11 ии, дизъюнкции и сложения по модулю два будут соответственно 0101, ОНО, 1000. На фиг. 5 представлен узел коммутации результатов двухместных логических функций, являющийся частою комутатора результв(гов 7. На двенадцать его входов поступают выходы с полых УПО, сгруппированные по операциям: 44 , 11, (конъюнкция): 44 о о о-j 11 vnut-inuvTiiia ) 44 . ; / yi о } (дизъюнкция;: 44 , оо ii (сложение по модулю два). Пра ч е се лек тор а арифКсёТййо -логически Ъпёраций 8 одного из кодов: Olbl, ОНО, 1000 - на первый вход демультиплексора 10 (см. фиг. 1) поступит результат поразрядной коньюнкШан, иш дизъюнкции, или сложения по модулю два сортветсярвенно. Далее результата поступает на выходной регист 13. Рассмотрим порядок выполнения алгебр paw ecKoro сложения. Начальная фаёа вы- псмШёния совпадает с соответствующей фа- ,зой1выпопн(вния;даухместных логических оцераций. В ней участвуют регистры 1 и 2, Мультиплексор 3, обеспечивающий; передачу второго операнда.из регистра 2 на матрйцу 5, и полные элек1й1тымб рйцы 5. Управляющий сигнал, посТу1аакяциЙ по связи 16 со второго выхода селектора 8 на ПЯТЫЙ вход; коммутатора 7, обеспёчивает подачу полусуммы 44, ЗЗ, 22 , И и полупереносов 44, ЗЗ, 22, ll и входногчэ переноса Р на форж й юватель суммь, являющийся частью K(3MMyTffpopa результата 7. Функциональная схема формирователя суммы представлена на фиг. б, При подаче селектора кодов 0001 и ОО10 (порядок вьшо юеНия вычитайиа полностью аналогичен порядку вьшолнеиия 51юзквная: 6тличйе заключаетсятолько в допойнительной микрооперации обращения второго операнда, которая выполняется мультиплек сором 3 под воздействием управляйте го сигнала с селектора 8, 1Й связи 18, по связи 16; (см. фиг. 1 и 6) подусуммы, полупереносы и входной пере- нос поступают на ф6рМй р 6ватбАШоуймы состоадий из 46Tbijsex пЬпусуйа оров в четьфех дизъюнкторов. На выходе формирователя образуетря четырехразрядная сумма ёцЗз SgSy и вйходной перенос ;Рвых,к торые поступают через общий выход коммутатора 7 на первый Двмультаплексора и далее на выходной рехтас-ф 13. Рассмотрим порядок выполнения умножения. Деление вьшолня.ется в значительной степени анало1 ично по методи&е, рагирабртанной и описанной в атв. св. СССР W 129390, кл. 42, 14 . Бюлл, изобр. h& 12, 1960 (см. Карцев М. А.Устр йство для умножения.в умйожёнйй асгл вуют (см. фиг. 1): регистры 1 и 2, мульл типлексор 3, матрицы 5, матрица 6, юмМутегтор 7, селектор 8. РеауиБтат пвредй на выход через демультиплексор 10 в выходной регистр 13, Умножение осуiuecTBnaeTCa матричным методом. СЬмно зйвтели ноступакут на матрипу но712 разряднойобработки 5. В операции участвуют вее элементы матрицы 5 - как прлные, так и вырожденные (коньюнкторы), так как Матрица 5 в данном случае является формирователем частных произведений. Частичные произведения поступают на четвертый выход меггрнцы 5 и далее на вход матрицы одноразрядных сумматоров 6, В результате суммирования частичньтх щюизведеннй на выходе матрицы 6 формируется полное произведение, которое поступает и а четвертый-вход коммутато- ра 7. Далее,под воздействием угфавляющего сигнала, поступанадёго на пятый вход коммутатора 7, со второго выхода селектора 8 произведение пропускается на демультиплексор 10 и выходной регистр 13. В реализации всех этих операций участвует блок формирования псевдооперанда 4. При вьшолнении отрицания блок 4 вырабатывает псевдооперанд, состоящий из одних единиц 1111, который При помощи м:удьтя11лексора 3 и селектора 8 подается на матрицу 5 вместо второго операнда, , Матрица SнйстраиЬается при помощи се-, лектора 8 на в ьшолнение сложения по модулю два. В результате сложения по модулю два первого операнда d j а i и цсевдорперанда 1111 осуществляется поразрядное о трицание первого операнда t - 1 1 М 5 Что и требовалось получить. Реализация операций сдвига производится при помощи узлов, обеспечивающих умножение, и блока формирователя псевдооперандов 4, который вырабатывает следующие псевдооперанды: а)0001 - для сдвига операнда А вправо на два разряда; б)ООЮ - для сдвига операнда А вправо не один разряд; в)OiOO -.для передачи операнда А без сдвига;. г)IPOO - для .сдвига операнда А влево на один . ДеЙств:ИТельно, если условиться выдавать короткий (четырехразрядный) резуль,тат DO средним цепям восьмиразрядного выхода коммутатора - формфователя 7 Ц6, Ц5, Ц4, ЦЗ, то появление такого ре- эу111 тага, iafaiQWMep: -в ЦеняХ Ц7, Ц6, Ц5, Ц4, будет восщэинимэтьсв КЁОС сдвиг слова влево на один разряд; -в цепях Ш, Ц4, ЦЗ, Ц2 - как сдвиг вхфаво на один разряд (см. фиг. 8). 9 7 Не трудно видеть, что перемножение слова на один из псевдооперандов 0001, 0010, 1000 обеспечивает его сдвиг соответственно вправо на два разряда, впра во на один разряд и влево на один разряд. Естественно, что при обычном умножении вос1 иразрядное произведение долж но восприниматься как единое слово, идущее без сдвига, что легко селектируется кодом операции. Считывание информации с регистра результата 13 любой операции производится при помощи специального управляющего Сигнала конца операции (СКО), который поступает на второй вход регистра 13 с выхода формирователя длительйости опера ПИИ 9 (см, фиг. 1). Упрощенная функциональвая схема формирователя 9 приведена на фиг. 7, Схема составлена, исходя из следующих начальных положений: а) Все операции разбиты на две группы Ef соответствии с их длительностью короткие (сложение, вычитание, конъюнкция, дизъюнкция, отрицание, сложение по модулю два) и длинные (умножение, деление, сдвиг вправо на даа разрада, сдвиг вправо на три разряда, передача без сдвига, сдвиг влево на один разряд). Отметим, что в принципе тахсих групп может быть и больше: можно, например, подразделить первую группу на две в одну из которых войдут самые корбткие бпё ранив, а именно двухместные логические , а в другую - операции средней длительности (сложение и вычитание) и т.п б)Длительцость длинной операции равна удвоенной длительности короткой опера цив (что примерно соответствует действителыюсти). в)Имеется некоторый (внешний 11лй внутренний) генератор синхроимпулйсзоь с периодом, равнъ1М длительности коротких операций..; Основу схемы составляет двигвюшй трезфазрядный регистр. На его вход ий селектора 8 поступает сигнал начайа операции (CaiO) по связи 23. Этот сигнал переходит либо на первый три.гтер Т,либо на второй триггер Т в зависимости от того, какой код операции поступил из се- лектора 8. Коды коротких операций (ООО1 0010, 0101, ОНО, 0111,1000) прихо Л дят по связи 24 и открьшают конък)нктор на входе -(2, а коды длинных операций (О011, 01ОО, 10О1, 1011, 1100) приходзт по связи 25 и открывают коньюнктор на выходе Т. Таким , образом в рё- гистр записывается либо слово ОЮ, ли2бо слово 100 (если читать слово на схеме сверху вниз). Далее на схему подают.ся сдвигающие импульсы. Из схемы вид. но, что на выходе триггера Т. (связь 14) появится сигнал конца операции (СКО), отстоящий во времени от сигнала начала операции (СНО) на величину длительности короткой или длинной операции соответственно. Этот сигнал поступает- на второй вход регистра результата 13 для вьщачи результата операции на внешний приемник информации. Затем ОКО со второго выхода регистра 13 поступает на внешний приёмник уже как осведомленный .сигнал о готовности микропроцессора выполнять следующую операцию. Предлагаемое нзобретение обеспечивает уменьшение объема управляющей памяти, упрощение схемы управления операциями, повышение однородности структуры и повышение быстродействия микропроцессора. Объем управляющей памяти 12 уменьшается за счет того, что умножение и Деление, вследствие их аппаратурной реализации, переходят из разряда макроопераций в разряд микроопераций. Упрощение схемы управления операциями обеспечивается также за счет того, : что умножение и деление становятся микрооперациями: во-первых, в блоке организации операций отпадает необходимость, по меньшей мере, в.схеме анализа счетчика. Вонзторых, полностью отпадает необходимость в счетчике циклов. В результате вместо громоздкой схемы управления операциями в предлагаемом устройстве используется гфостой селектор арифметико-логических операций 8 (фиг. 4). Повышение регулярности структуры произошло потому, что основными узлами предлагаемого устройства являются матрица узлов подразрядной обработки операндов -5 и матрица одноразрядных двоичйых бумМаторов 6, которые вследствие матричного принципа их работы имеют полностью однородную структуру (фиг. 1, 2). Кроме того, матркчиай структура устраняет мноxJKpaTHOCTb работы микропроцессора при обработке длинных операций, что повышает быстродействие микропроцессора и упющает согласование временной диаграмы работы микропроцессора с временной иаграммой работы сопрягаемых устройств Повышение производительности в принйпе также является следствием того. то макрооперации умножения и деления ереведены в разряд микроопераций. Поучаемый положительный э4|фект возника- 11717 счёт йпредёленного увеличения затрат оборудования, Эти затраты получаются достаточно умеренными за счет уменьшения аппаратуры, потребной на реализацйю jTipaBnHioiuefi памяти и схемы управления опэрациями.; Формул а и 3 о б р е т е ни я Микропроцессор, содержащий регистр первого операнда, регистр второго ойеран« дет, Мультиплексор, демультйплексор, упр&ёдайэйу to пшятк, йШятъ )п едёбЙ фа, регистр результата, причем информаднонныё входы регистров ,первого и второго операндов являются информационными вХоЙЙЙУ МЙ1фШроШйсораГ а управЛЙющ1не вхоч ды регистров первого и второго ёперандов подключены к первому угфавляющему входу микропроцессора, информаииодаьй вьгход демультнплексора подключен к инфор йацйоннЬму входу регистра результата, тервый и второй входы мультиплексора подключены соответственно к выходу регистра второго операнда и к выходу па1«ш тй процбсжора, ёь1Ход {Зё1йШ рарезуль является информацирниьш выходом микропроцесс раУ вход упревляющей памяти является вторым управляющим входом мик- ропроцессора, о т л и ч а ю щи и с я тем, что, с целью повышения быст микропроцессора, уменьшений объем оборуШванйй, повшйенйя однородноБтй структуры микропроцессора, в него до полHHfentHO введены комм татор реву1П1эТата,, селектор арифметико-логических опарахшй, формирователь длительности операций,блок пс еш9Ш§рйнЯов; аГ|1йца одноразрядных сумматоров, матрица узлов поразрядной обработки операндов, первый в второй информационные входь которой подключены соответственно к выходам ре- Гнстра первого ОперЖда и KiyiiwltifiKiiKCoW pa первый, второй, третий и четвертый 2 ыходы матрицы узлов поразрядной обработки операндов подключены соответственно к первому, второму, третьему входу коммутатора результата и входу матрицы одноразрядных сумматоров, выход которой подключен к пятому входу коммутатора результата, четвертый вход которого подключен ко второму выходу селектора арифметико-логических операций, выход коммутатора результата подключен к первому входу демупьтиплексора, второй вход демультиплексора подключён к третьему выхоДу селектора арифметикб-лргическйх операций, выход демультиппексора подключен к первому входу памяти процессора, второй вход памяти процессора подключен к четвертому выходу селектора арифметико-лог ических операций, третий и четвертый входы мультиплексора подключены соответственно к первому выходу селектора арифметикр- логич ских операций, и выходу блока формирования псевдо- операндов, вход селектора арифметико-логических операций подключен к выходу управляющей памяти, пятый выход селектора арифметико-сюгических операций подключен ко входу формирователя длительности операций, выход которого соединен со вторым входом регистра результата, второй вьгход регистра результата является выходом сигнала конца операции микропроцессора, источник сигнала входного переноса подключён к шестому входу коммутатора результата. Источники информации, принятые во внимание при экспертизе 1.Патент США М 3752394, АЛУ модульного типа , кл. 235-174, 1973. 2.Патент ОНА Ni 3757308, Однокристалшый щюцессор, кл. 340-172.5, 1973. 3.Барраклаф В., Цзян А., Сол В. Методы тестироваййяя микромашинных устч ройств, ТИИЭР & 6, июнь 1976 - прототип.

L/L Tzzrzs шНП

f

15 TT V-A J-V 4 Данные Управляю-, (Kve счгнам

(fiftЧу

-ff ijfOifibj}

.

-ffij- () -f(i/(aig.b) (-,,9

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1983 |

|

SU1141419A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Арифметико-логическое устройство | 1976 |

|

SU648979A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Арифметико-логическое устройство со встроенной диагностикой | 1984 |

|

SU1275426A1 |

| Устройство для выполнения арифметических и логических операций над словами | 1978 |

|

SU767757A1 |

| Процессор | 1977 |

|

SU691858A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Арифметико-логическая секция | 1987 |

|

SU1499333A1 |

Операционная часть

А9ресная часпи

0m f

Olio

0101

VT 0m S

0001

0 d 10

0011 01 00

1 001 1 01 0 1 01 1 1 100

7

Фu.f

9

717772

/

-I-I-

US

143

Ц

цг

Ц1

I 1ч Фиг. 8

Авторы

Даты

1980-02-25—Публикация

1977-06-01—Подача