(54) УСТРОЙСТВО ОТОЧЕТЛ ИНТЕРВАЛОВ ВРЕМЕНИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство отсчета интервалов времени | 1982 |

|

SU1103228A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU983707A1 |

| Устройство для редактирования информации | 1981 |

|

SU980099A1 |

| Устройство для контроля электропотребления | 1988 |

|

SU1566371A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для вычисления функции | 1984 |

|

SU1180884A1 |

| Устройство групповой тактовой синхронизации (его варианты) | 1982 |

|

SU1096760A1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| Устройство для анализа частоты использования блоков информации в вычислительных комплексах | 1990 |

|

SU1793442A1 |

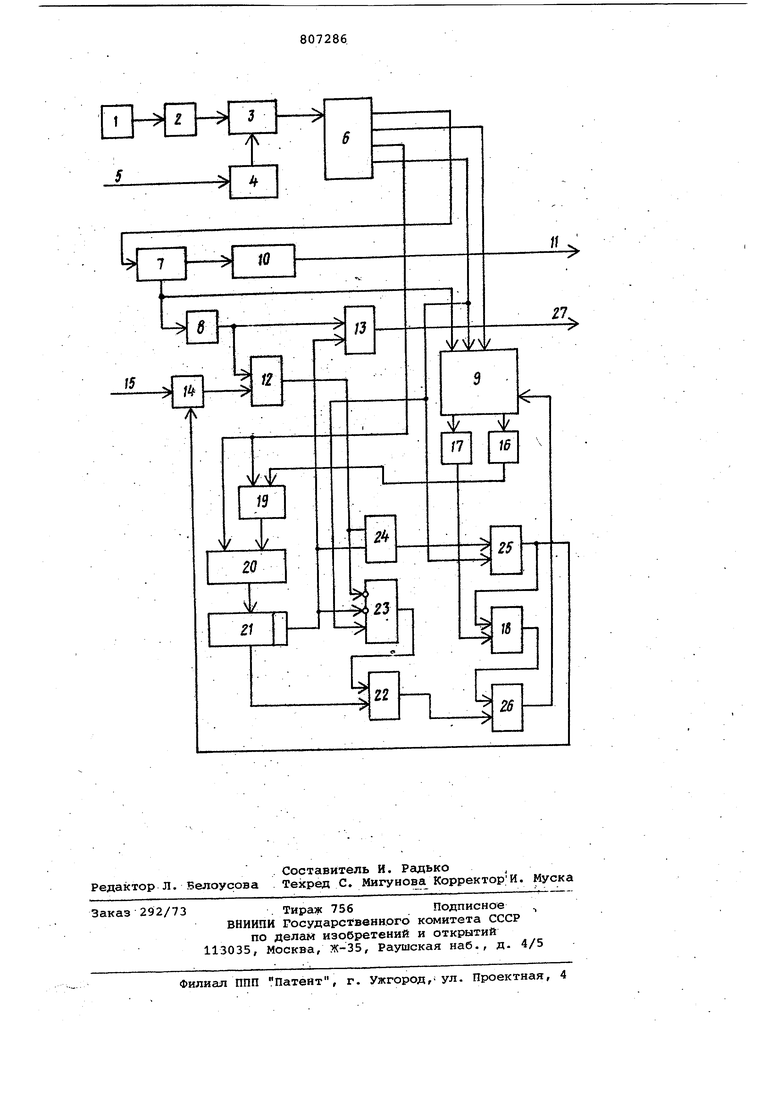

Изобретение относится к вычислительной технике и может быть использовано в вычислительных машинах и системах для управления вычислительным процессом в реальном масштабе времени. Известно программное временное устройст-во, содержащее-генератор импульсов и последовательно соединенные счет,чик импульсов, блок набора программы, дешифратор, элементы И и исполнительные элементы, несимметричный триггер и инвертор Л. , Недостатком известного устройства является то, что интервалы времени, отсчитываемые устройством синхронны, так как используется один аппаратурный счетчик, отсутствует коррекция частоты, Известно временное устройство, содержащее генератор импульсов, счетчик времени, узлы связи, линии задержки, блоки прерывания, коррекции, обнуления, запроса текущего интервала элемент ИЛИ, элемент совпадения, программные сумматор и таймер j2J. Недостатком этого счетчика единого времени является то, что коррекция осуществляется с помощью импульсов единого времени, отсчет интервалов времени осуществляется программным путем.в процессоре, в результате снижается производительность вычислительной машины. Целъ изобретения - расширение функциональных возможностей, организация многоканального отсчета интервалов времени ак циклически, так и по запросам, введение автономной коррекции для согласования кванта генератора и кванта отсчитываемого времени. Поставленная цель достигается тем, что в устройство, содержащее последовательно соединенные генератор импульсов, делитель частоты и счетчик текущего времени, в него дополнительно введены регистр коррекции, корректор, формирователь серии импульсов, счетчик адреса, дешифратор, регистр запроса, блок сравнения, блок памяти, коммутатор адреса, регистр текущих интервалов, регистр констант дополнений, коммутатор сумматора, комбинационный сумматор, регистр суммы, элемент И, элемент запроса, два коммутатора, блок ИЛИ и элемент ИЛИ, причем выход делителя частоты соединен с первым входом корректора, вто,рой вход которого подключен к вьтходу регистра коррекции, выход корректора соедин1ен с входом формирователя серии импульсов, первый выход которого соединен со входом счетчика адреса, выход переполнения которого соединен с входом счетчика текущего времени, выход счетчика адреса соединен с адресным входом блока памяти и с входом дешифратора, выход которого подключен к первому входу коммутатора адреса и первому входу блока сравнения, второй вход которой соединен с выходом регистра запроса, второй выход формирователя серии импульсов подключен к входу чтения блока памят выходы которого подключены к входам регистра констант дополнений и регистра текущих интервалов, выход ко1 орого подключен ко второму входу коммутатора сумматора, к первому входу которого и к первому входу, комбинаци онного сумматора подключен третий вы ход формирователя серии импульсов, ко второму входу комбинационного сум матора подключен выход коммутатора сумматора, выход комбинационного сум матора соединен со входом регистра сумми, выход которого соединен со вторым входом первого коммутатора, вы ход разряда переполнения регистра суммы соединен со вторым входом коммутатора адреса, со вторым входом элемента ИЛИ и вторым инверсным входом элемента запрета, выход блока сравнения подключен к первому входу элемента. ИЛИ и к первому инверсному входу элемента запрета, выход которо го соединен с первым входом первого коммутатора, четвертый выход формирователя серии импульсов подключен ко входу записи блока памяти, к третьему входу элемента запрета и кО второму входу элемента И, выход кото рого соединен со входом сброса регистра запроса и с первым входом второго коммутатора, ко второму входу которого подключен выход регистра констант дополнений, выходы первого .и второго коммутатора через блок ИЛИ .подсоединены к информационному входу блока памяти, выход элемента ИЛИ соедин н с первым входом элемента И. Ка чертеже приведена функциональная схема устройства отсчета интерва лоа времени, осуществляющего отсчет . интервалов реального времени цикличе ки и по запросам. Устройство содержит последователь но соединенные генератор 1 импульсов и делитель 2 частоты. Выход делителя 2 частоты соединен со входом корректора 3, осуществляющего согласование кванта генератора 1 импульсов и кван таинтервалов времени. Константа коррекции хранится в регистре 4 коррекции, куда записывается по щине 5. Вы ход корректора 3 соединен со входом формирователя 6 серии импульсов, управляющего работой устройства. Первы выход формирователя б серии импульсо соединен со счетным входом счетчика 7 адреса. Выход счетчика адреса 7 подключен ко входу дешифратора 8 и к адресному входу блока 9 памяти, а сигнал переполнения счетчика адреса 7Поступает на счетный вход счетчика 10 текущего времени. Выход счетчика 10 текущего времени шиной 11 соединен с устройством управления вычислительной машины. Выход дешифратора 8соединён со входами блока .12 сравнения и коммутатора 13 адреса. Второй вход блока 12 сравнения соединен с выходом регистра 14 запроса. Информация в регистр запроса заносится по шине 15. Второй выход формирователя 6 серии Импульсов соединен со входом чтения блока 9 памяти. Выходы блока 9 памяти Соединены со входами регистра 16 текущих .интервалов и ре гистра 17 констант дополнений. Выход регистра 17 констант дополнений соединен со вторым входом коммутатора 18. Выход регистра 16 текущих интервалов соединен йо вторым входом коммутатора сумматора 19, Третий выход формирователя 6 серии импульсов соединен с первым входом комбинационного сумматора 20 и с первым входом коммутатора сумматора 19. Выход комбинационного сумматора 20 соединен со входом регистра 21 суммы. Выход регистра. 21 суммы соединен со вторым входом коммутатора 22, а выход разряда переполнения регистра 21 суммы подключен ко второму входу коммутатора 13 адреса, ко второму входу элемента запрета 23 и ко второму входу элемента ИЛИ 24. Четвертый выход формирователя серии импульсов б подключен ко входу записи.блока памяти 9, к третьему входу элемента 23 запрета и ко второму входу элемента И 25. Выходы ко1«Еиутаторов 13 и 22 через блок ИЛИ 26 соединены с информационным входом блока 9 памяти. Выход ком-мутатора 13 адреса по шине 27 соединен с устройством управления вычислительной Машины. Выход элемента ИЛИ 24 соединен с первым входом элемента И 25. Выход элемента И 25 соединен с первым входом кОммутсгтораГ 18 и со входом сброса регистра 14 запроса.- ; . Устройство работает следующим образом. . . . : . В регистр коррекции 4 заносится константа коррекции по шине 5, которая определяется исходя из требований к частоте заполнения счетчиков вретни. Генератор 1 вырабатывает опорную частоту, которая через делитель 2 поступает на вход корректора 3. В корректоре 3 осутдествляется циклическое сложение константы коррек- сигналы переполнения с выхода корректора 3 выдаются с частотой, которая требуется для работь счетчиiKa 7 адреса. В формирователе серии импульсов 6, по приходу казвдого импульса с корректора 3, вырабатывается распределенная во времени серия импульсов, которая служит для управления устройства. Импульс с первого выхода Формирователя б серии импульсов поступает на вход счетчика 7 адреса/ на котором формируется адрес интервала, который поступает на адресный вход блока памяти. .При пригходе импульса со второго выхода формирователя б серии импульсов на вход чтения блока 9 памяти происходит счи тывание значения йременного интервал .в регистр 16 текущихинтервалов 16 и кода константы дополнения в регист 17 констант дополнений. Код текущего интервала поступает на вход коммутатора сумматора 19, с .приходом импуль са с третьего выхода формирователя б серии импульсов происходит суммирова ние значения текущего интервала с единицей, и образуется новое значение т кущего интервала, которое через комбинацирнный сумматор 20 записывается в регистр 21 суммы. Если не закончен отсчет интервала то в разряде переполнения.регистра 2 суммы будет ноль. Импульс с четвертого выхода формирователя б серии им пульсов через элемент запрета 23, при условии отсутствия сигнала запроса с блока 12 сравнения, откроет :.оммутатор 22 и через блок ИЛИ 26 код текущего интервала поступает на информационный вход блока 9 памяти. Одновременно импульс с четвертого выхода формирователя 6 серии импульсов поступает на вход записи блока 9 памяти, и произойдет запись нового значения текущего интервала. Если за кончен отсчет интервала, то сигнал с выхода разряда переполнений регистра суммы 21 запрещает прохо хдение импульса .через элемент запрета 23 и через элемент ИЛИ 24 откроет элемент И 25. На второй вход элемента И 25 проходит сигнал с четвертого выхода формирователя серии импульсов б. Сигчал с выхода элемента И 25 открывает коммутатор 18 и через блок ИЛИ 26 на информационный вход блока9 памяти поступает значение кода константы дополнения. Одновременно сигнал с четвертого выхода формирозватеяя серий импульсов 6 поступает на вход записи 1блока 9 памяти, где на место значения текущего интервала записывается константа дополнения. Сигнал с разряда переполнения регистра 21 суммы поступает на второй вход коммутатора 13 адреса, на первый вход кд орогр приходят сигналы, указывающие номер временного канала, с выходов деши раторе 8. В результате по шине 27,5выдается сигнал указывающий номер временного канала,-который закончил отсчет интервала времени. На этом работа первого временного канале устройства заканчивается. При выходе следующего импульса с корректора 3 на вход формирователя б серии импульсов, значение счетчика 7 адреса увеличивается на единицу. Работа второго временногр канала происходит аналогично работе первого канала. временных каналов устройства к 2, где я - разрядность счетчика адреса 7. при переполнении счетчика адреса 7, с выхода переполнения на вход .счетчика текущего времени поступает импульс, увеличивающий его содержание на единицу. Информация о текущем времени может сниматься со :счвтчика 10 текущего времени, а младшие разряды со счетчика 7 адреса. При переполнении счетчика TeKyiaero времени 10 по шине 11 высылаетсз сигнал, который поступает в устройство управления ЦВМ для соответствукж ей коррекции программно-организовавиого счетчика текущего времени. Запуск отсчета интервала времени рсущесзгвляется по шине 15. В регистре 14 запроса соответствующий разряд устанавливается в единицу. С выхода регистра 14 запроса сигналы поступают а вход блока сравнения 12 и при совпадении номера временного канала, установленного в счетчике адреса 7, с номером установленного разряда в регистре запроса 14, сигнал с выхода блока 12 сравнения поступит на коммутатор 18 через элемент ИЛИ 24 и элемент И 25. В результате, независимо от состояния выбранно1ч временного канала, прозойдет запись содержимогорегистра 17 констант дополнений в блок 9 памяти на место значения текущего интервале. .Это соответствует запуску соответствукадего временного канала. После запуска установленный разряд в регистре 14 запроса сбрасывается импульсом с выхода элемента И 25.- .; :., : , в результате любой временной канал может быть 3 апуаден с любого момента времени пй запросу. Использование коррекции частоты позволяе.т получить заданный квант отсчитываемого временного интервала независимо дт значения частоты генератора импульсов. Реалиэагщя функции многокангшьного . на одном оборудовании поз воляет уменьшить аппаратурные з атраты и отказываться от программного отсчета временных интервалов, что повышает производительность ЦВМ. Формула изобретения , Устройство отсчета интервалов вреени, содержащее последовательно содиненные генератор импульсов, делиель частоты и счетчик текущего времеи, отличающееся тем, то, с целью расширения функционаяь.ных возможностей, в него дополнитель введены регистр коррекции, коррггк т.ор, формирователь серии импульсов, счетчик адреса,.дешифратор, регистр запроса, блок сравнения, блок памяти коммутатор адреса, регистр текущих интервалов, регистр констант дополнений, коммутатор сумматора, комбинационный сумматор, регистр суммы, элемент И, элемент згшрета, два коммутатора, блок ИЛИ и элемент ИЛИ, причем .выход делителя частоты соединен с первым входом корректора, второй вход которого подключен к выходу регистра коррекции, выход корректора соединен с входом формирователя серии импульсов, первый выход ко.торого соединен со входом счетчика адреса, выход переполнения которого соединен с входом счетчика .его времени, выход счетчика адреса соединен с адресным входом блока памяти и с входом дешифратора, выход которого подключен к первому входу коммутатора адреса и первому входу блока сравнения , второй вход которой соединен с выходом регистра запроса, второй выход Формирователя серии импульсов подключен к входу чтения блока памяти, выходы которого подключены к входам регистра констант дополнений и регистра текущих интервалов, выход которого подключен ко второл у входу коммутатора сумматора, к первому вхо ду которого и к первому входу комбинационного сумматора подключен трети выход формирователя серии импульсов. ко второму входу комбинационного сумматора подключен .выход коммутатора сумматора, выход комбинационного сумматора соединен со входом, регистра суммы, выход которого соединен со BTopbiM входом первого коммутатора, выход разряда переполнения регистра. суммы соединен со вторым входом коммутатора адреса, со вторым входом элемента ИЛИ и втогидм инверсным входом элемента запрета, выход блока сравнения подключен к первому входу элемента ИЛИ и к первому инверсному входу элемента запрета, выход которого соединен с первым входом первого коммутатора, четвертый выход формирователя серии импульсов подключен ко входу записи блока памяти, к третьему входу элемента запрета и ко второму входу элемента И, выход которого соединен со входом сброса регистра запроса и с первым входом второго коммутатора, ко второму входу которо.го подключен выход регистра констант дополнений, выходы первого и второго коммутатора через блок ИЛИ подсоединены к информационному входу блока памяти, -выход элемента ИЛИ соединен с первым входом элемента И. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 532860, кл. 60 F 9/0,0. 2.Журавлев fo. Н. Системное проектирование управляющих ЦВМ. М., Соврадио , 1974., с. 271, (прототип) J

Авторы

Даты

1981-02-23—Публикация

1979-03-28—Подача