группой информационных входов четвертого сумматора, управляющий вход которого соединен с управляющим входом пятохо сумматора и с выходом сумматора по модулю два, второй вход которого соединен с управляющими входами третьего, шестого и седьмого сумматоров, выходы третьего регистра соединены с первой группой информационных ,входов третьего CiMbjaTopa, втор%я группа информационДых входов которого Соединена с выходами первого блока памяти, причем бло) управления содержит тенератор тактовых импульсов,, счетчик тактовых

i. МЧ

импульсов, три триггера, два элемента И элемент НЕ, элемент И-НЕ, формирователь импульсов, вход которого подключен к входу запуска блока и к синхронизирующему входу первого триггера, выход формирователя импульсов соединен с первым входом первого элемента И, выход которого соединен с входом сброса первого и второго триггеров и счетчика тактовых импульсов, выход первого триггера соединен с входом разрешения генератора тактовых импульсов, первый выход которого соединен с выходом синхронизации блока управления, второй выход генератора тактовых импульсов соединен с синхронизирующим входом второго триггера, первый выход которого с выходом разрешения записи блока управления, второй выход второго триггера соединен с первым входом элемента И-НЕ, второй вход которого соединен через элемент НЕ с входом задания режима блока управления, выходы номера текущей итераци которого соединены с выходами счетчика.выход переполнения которого соединен с вторым входом первого элемента И, синхронизирующий вход счетчика соединен с выходом второго элемента И, первый вход которого соединен с первым выходом генератора тактовых импульсов и с синхронизирующим входом третьего триггера инверсный выход которого

соединен с третьим входом второго элемента И, второй вход которого соединен с выходом элемента И-НЕ, отличающееся тем, что, с целью повышения быс;тродействия, оно дополнительно содержит второй и трртий блоки памяти, дешифратор, П - триг r-epcui коррекции, блок формирования порядка числа, блок анализа сходимости, а в блок управления дополнительно введены два элемента И, причем выходы номера текущей итерации блока управления подключены к адресным входам второго и третьего блоков памяти, выход коррекции блока управления соединен с стробирующим входом дешифратора, входы которого соединены с выходами второго блока памяти, а выходы - с входами установки триггеров, выходы которых соединены с второй группой адресных входов третьего блока памяти, выходы которого соединены с управляющими входами первого и второго коммутаторов, выходы блока синхронизации и управления записью блока управления соединены соответственно с входом синхронизации и входа выборки переменной вращения блока формирования порядка числа, вход знака операнда которого соединен с входом старшего разряда группы информационных входов устройства, первая, вторая и третья группы информационных входов блока формирования порядка числа соединены соответственно с выходами первого, второго и третьего сумматоров, вход кода вычисляемой функции блока формирования порядка числа соединен с входом кода вычисляемой функции устройства, выход кода переменной вращения блока формирования порядка числа соединен с управляющим входом третьего сумматора, а информационные выход блока формирования порядка числа с первой группой информационных входов блока анализа сходимости,вторая группа информационных входов которог соединена с выходами номера текущей итерации блока управления, вход сброса блока анализа сходимости соединен с первым входом блока управления, выходы синхронизации и управления сравнением кодов которого соединены соответственно с входами синхронизации и управления регистров блоха анализа сходимости, выход кото)ого соединен с входом признака оррекции блока управления, причем тервый вход третьего элемента И управления соединен с выходом лервого элемента И, второй тзход третьего элемента И подключен к вхп;1У признака коррекций блока ут.-п ипшя, вход признака окончания корхм п.ии

которого соединен с первым информационным входом третьего триггера, второй информационный вход которого соединен с прямым выходом этого тригера и с первым входом четвертого эмента И, выход которого подключен к выходу управленил коррекции блока управления, второй вход четвертого элемента И соединен с синхронизирующим входом третьего триггера и с первым выходом генератора тактовых Импульсов, вход сброса третьего тригера подключен к выходу третьего эмента И, третий выход генератора тактовых, импульсов соединен с выходом управления сравнением кодов блока управления, выход разрешения записи которого соединен с входами разрешения установки и триггеров коррекции и с входом управления выбором переменного п вращения блока формирования порядка числа, вход синхронизации которого соединен с выходом синхронизации блока управления, признак окончания коррекции которого соединен с выходом второго блока памяти, стробирующий вход которого соединен с выходом блока анализа сходимости входом признака коррекции блока управления, причем блок анализа сходимости содержитрегистр, схему сравнения, триггер условия, выход которого соединен с выходом блока анализа сходимости, а обнуляющий синхронизирующий и информационный входы триггера соединены соответственно с входами сброса, синхронизации блока анализа сходимости и выходом схемы сравнения, первая и вторая группы информационных входов которого соединены с информационными входами блока анализа сходимости и выходами регистра, информационные входы которого соединены с второй группой информационных входов блока анализа сходимости,а уравляющий вход регистра coem-tHeti.c входом управления анализа сходимсм.-ш а блок формирования порядка числа .( держит два мультиплексора,блок памяти триггер знака,регистр,п-1 сумматоров по модулю два (п - разрядность чисел), узел приоритета и шифратор, выходы и входы которого соответственно соединены с информационными выходами блока формирования порядка чис:ла и выходами узла приоритетов, входы которого соединены с выходами сумматоров по модулю два, первые входы которых соединены с выходом старшего разряда регистра, вторые входы сумматоров по модулю два соединены с выходами младших разрядов регистра,информационные входы которого соединены с выходами первого мультиплексора, первая., вторая и третья группы информационных входов которого соединены ,с первой,второй и третьей группами информационных входов блока формирования порядка числа, синхронизирующий вход регистра с синхронизирующим входом триггера знака, информационный вход которого соединен с выходом блока памяти, вход управления выбором переменной вращения блока формирования порядка чисел соединен с управляющим входом второго мультиплексора, первый информационный вход которого соединен с входом знака операнда блока формирования порядка чисел, вход кода вычисляемой функции которого соединен с первым адресным входом блока памяти и управляюшдм входом первого мульти-плексора,второй вход которого подключен к выходу второго мультигатексора, а вход синхронизации блока формирования порядка числа соединен с синхронизирующим входом триггера, выход которого соединен с выходом кода,переменной вращения блока формирования порядка числа.

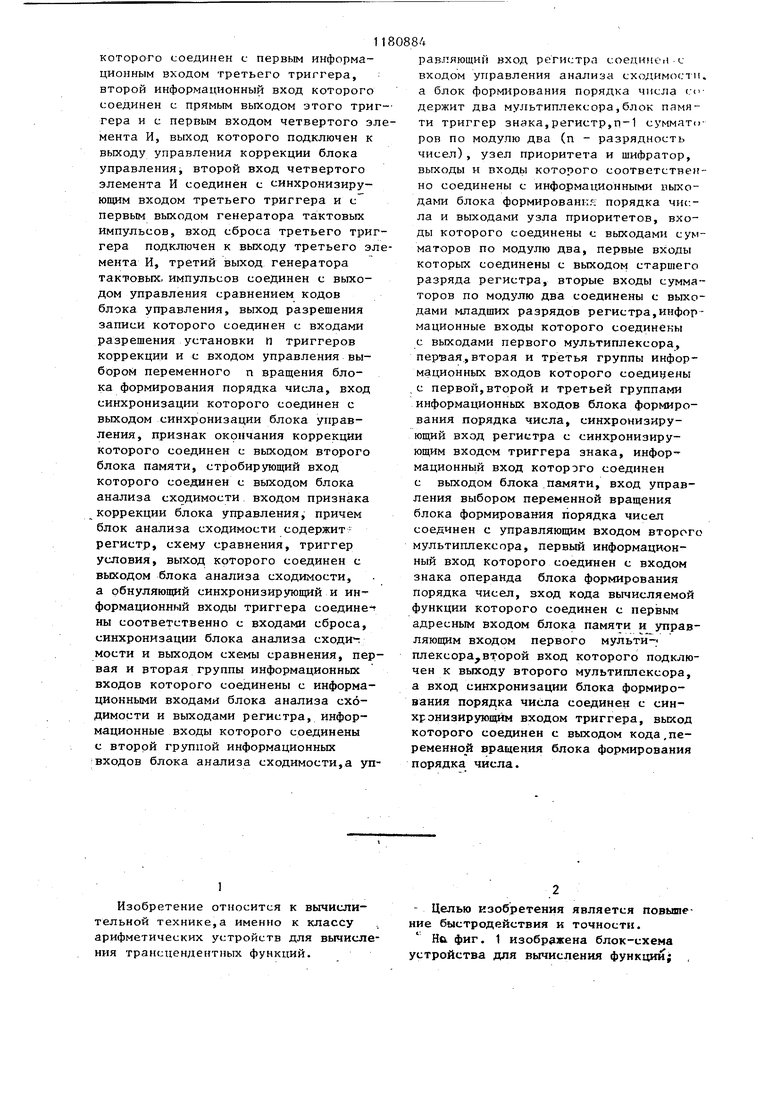

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1130861A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1332313A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1315999A1 |

| Устройство для преобразования координат | 1985 |

|

SU1254475A1 |

| Вычислительное устройство для поворота вектора | 1987 |

|

SU1520511A1 |

| Устройство для выполнения векторно-скалярных операций над действительными числами | 1990 |

|

SU1718215A1 |

УСТРОЙСТВО ДОЯ ВЫЧИСЛЕНИЙ ФУНКЦИЙ, содержащее три регистра, семь сумматоров, четыре сдвигателя, два коммутатора, сумматор по модулю два, первый блок памяти и блок управления, вход запуска которого соединен с входом запуска устройства, вход управления типом итерационных констант которого соединен с входом задания режима блока управления, первым ВХОДОМ сумматора по модулю . два, управляющими входами первого и второго сумматоров и с входом старшего разряда адреса первого блока памяти, входы младших разрядов которого соединены с управляющими входами всех сдвигателей и с выходами Номера текущей итерации блока управления выход синхронизации которого соединен с синхронизирующими входами первого, второго и третьего регистров, информационные входы которых соединены с информационным входом устройства, первая, вторая и третья группы информационных выходов которого соединены соответственно с выходами первого, второго и третьего сумматоров,, а также с информационными входами первого,,второго и третьего регистров, входы разрешения записи которых соединены с выходом разрешения записи блока управления, а выходы первого регистра - с информационными входами первого и второго сДвигателей и с первой груп-г пой информационных входов четвертого сумматора, выходы которого соединены с первой группой информационных входов первого сумматора, вторая группа информационных в содов которого соединена с выходами первого коммутатора, информационные входы которого соединены с выходами пятого сумматора, первая группа информационных входов (Л которого соединена с выходами первого сдвигателя и с первой группйй информационных входов шестого сумматора, выходы которого соединены с первой группой информационных входов второго сумматора, выходы второго регистра соединены с информационными входами третьего и четвертого сдвигателей и с второй группой инэо формационных входов щестого суммато00 4 ра, управляющий вход которого соединен с управляющим входом седьмого сумматора выходы которого соединены с информационными входами второго коммутатора, выходы которого соединены с второй группой информационных входов второго сумматора, выходы второго и третьего сдвигателей соединены соответственно с первой и второй группами информационных входов седьмого и пятого сумматоров, вторая группа информационных входов седьмого сумматора соединена с выходами четвертого сдвигателя и с второй

1

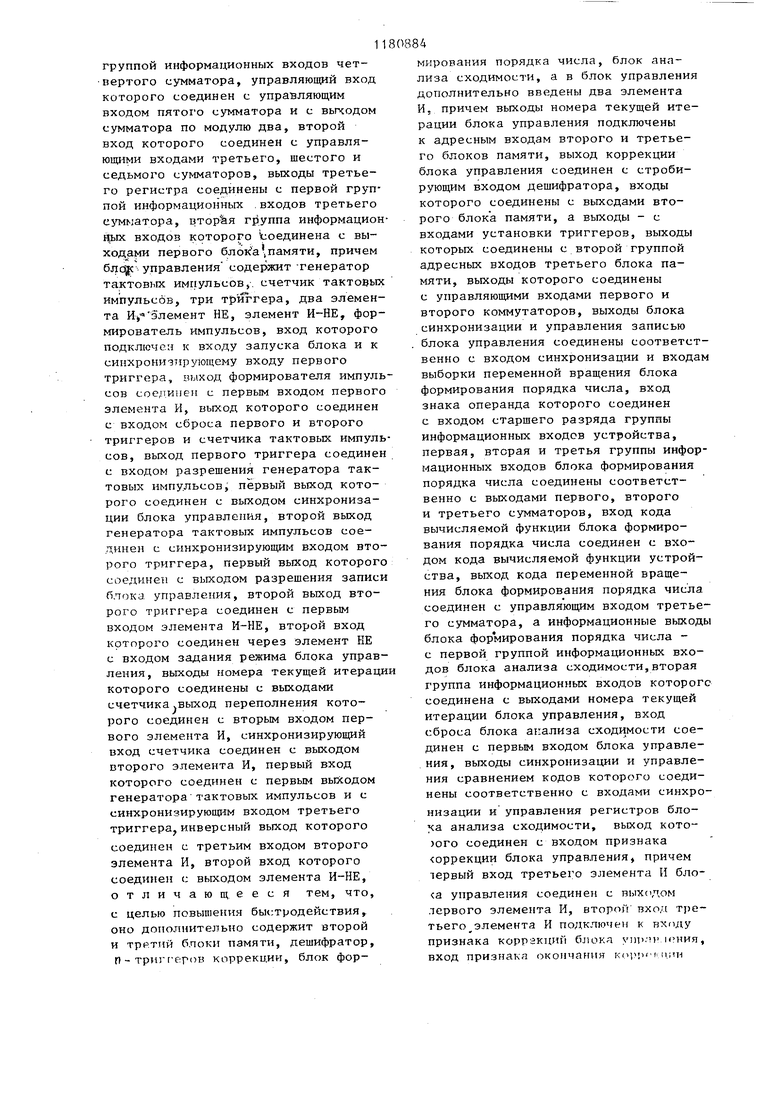

Изобретение относится к вычислительной технике,а именно к классу арифметических устройств для вычисления трансцендентных функций.

- Целью изобретения является повьвпение быстродействия и точности.

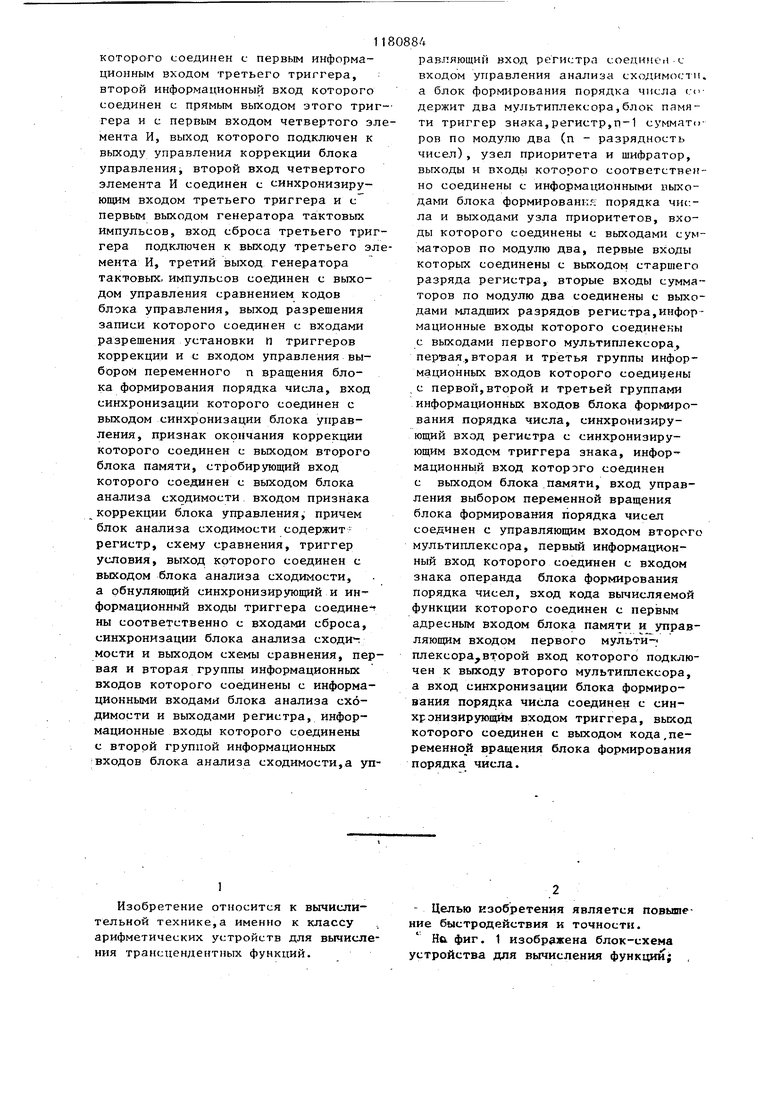

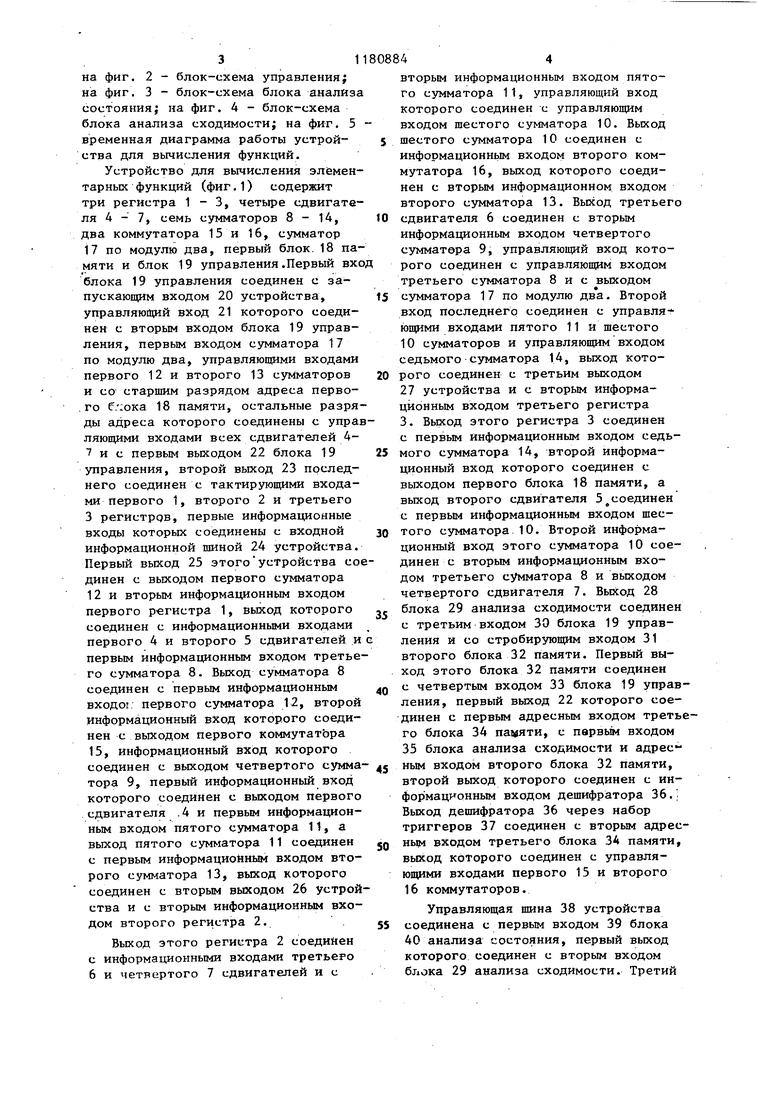

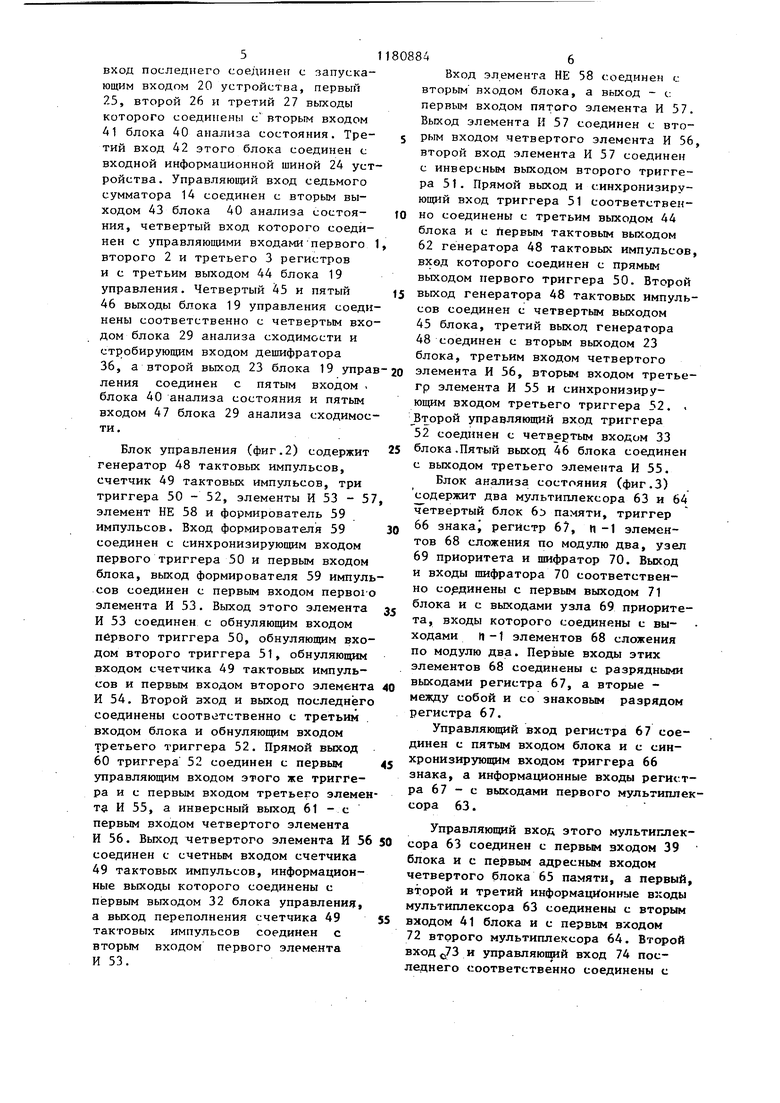

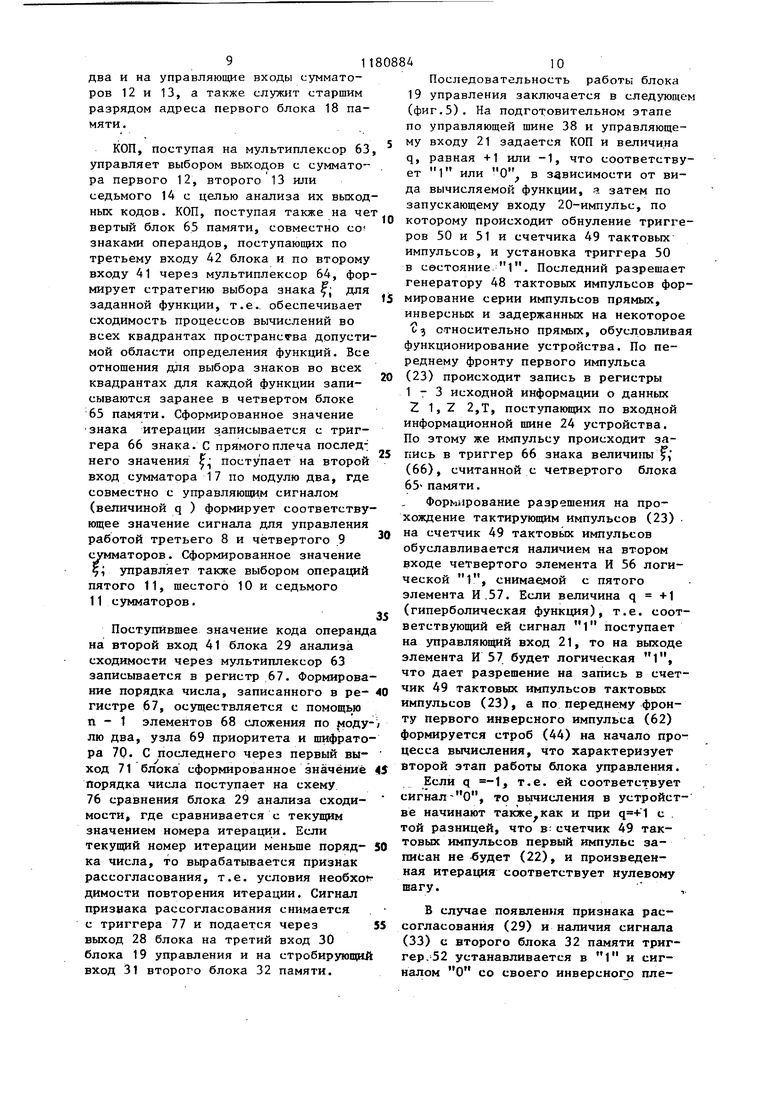

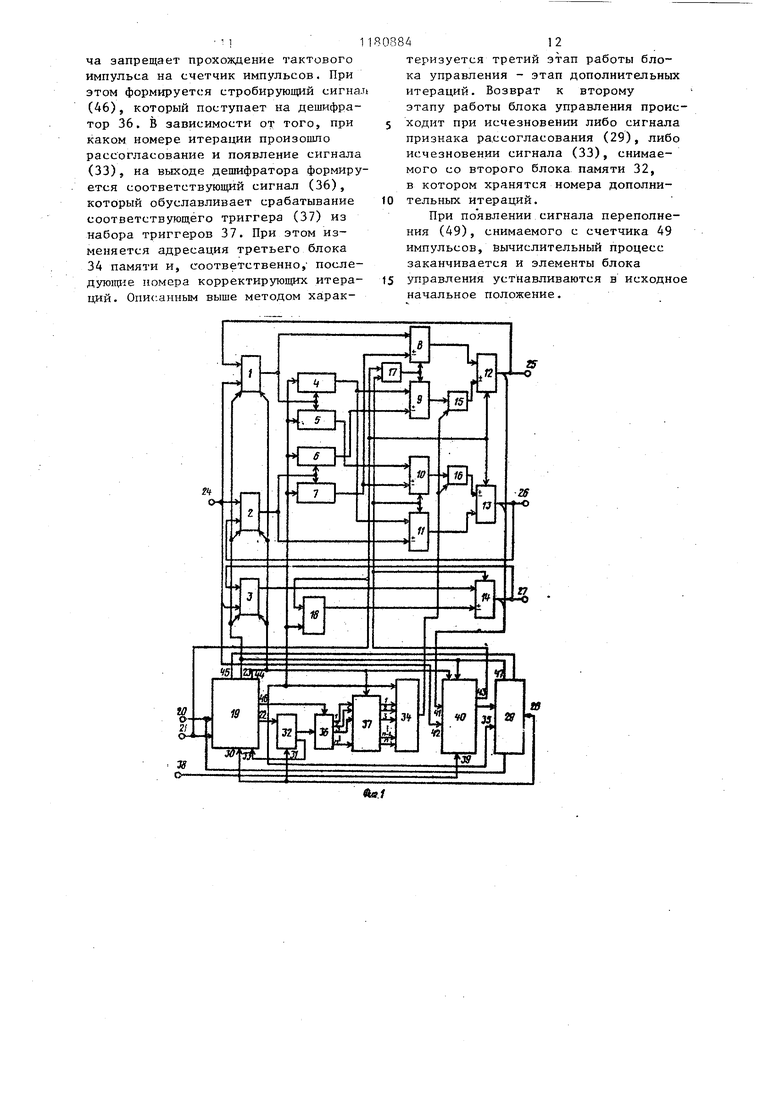

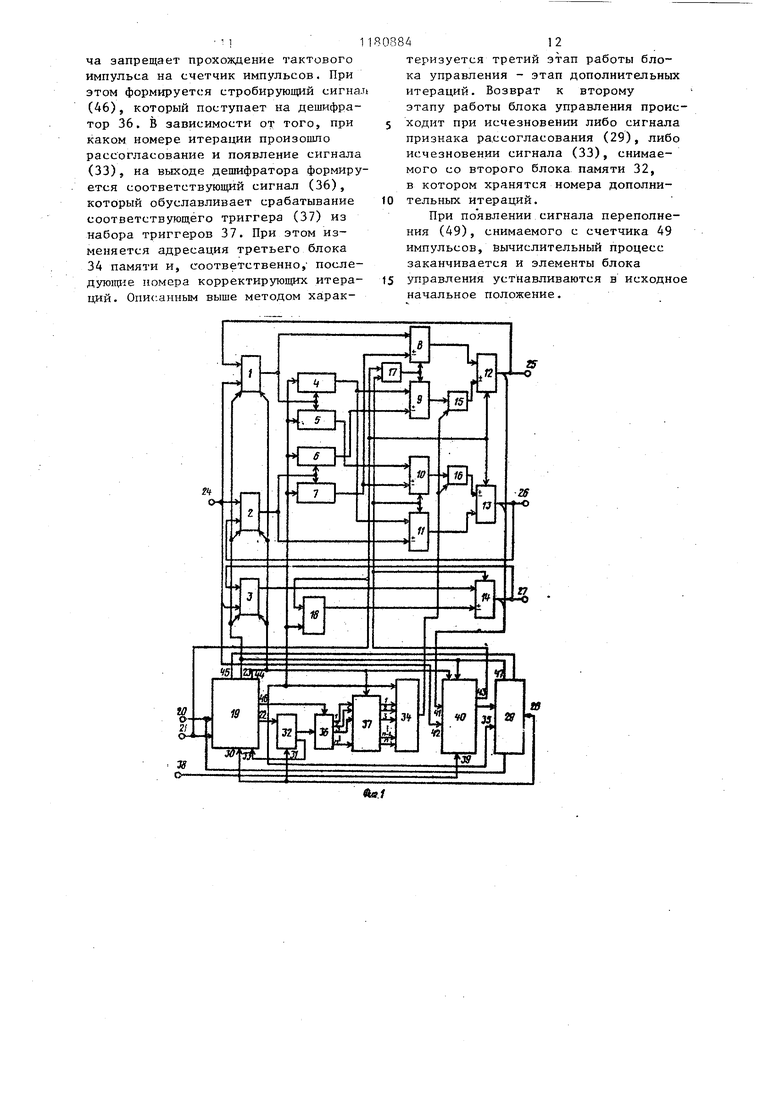

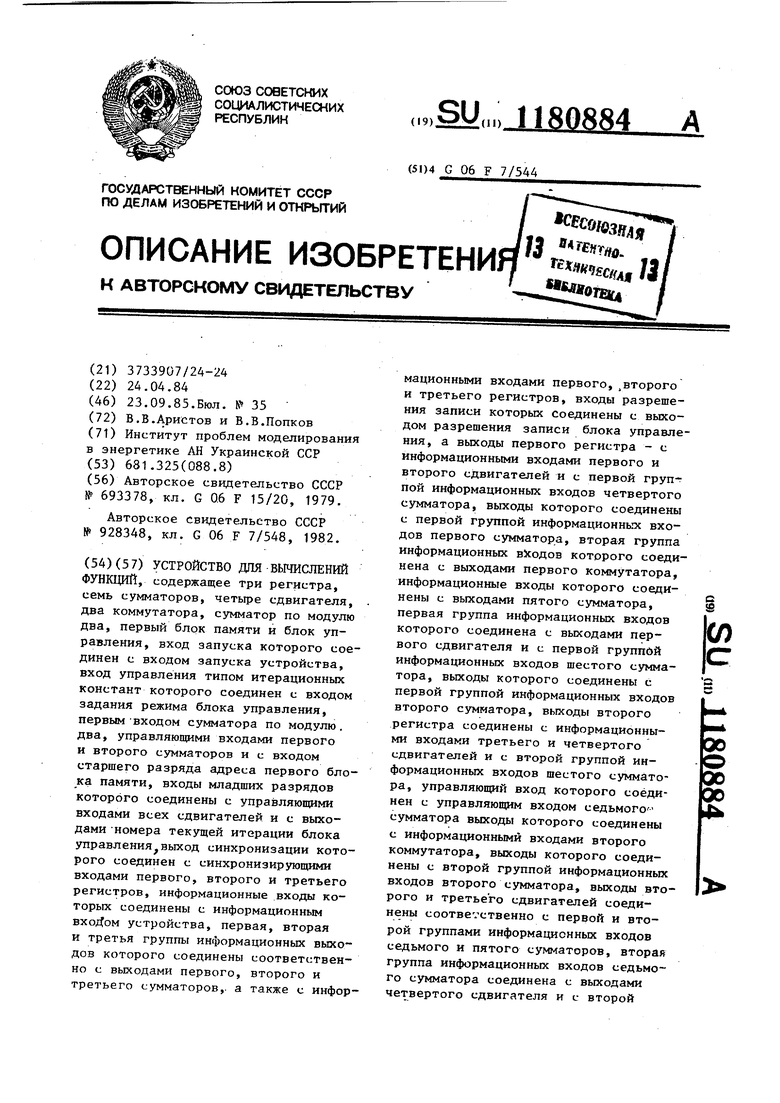

Ни фиг. 1 изображена блок-схема устройства для вычисления функции; на фиг. 2 - блок-схема управления; на фиг. 3 - блок-схема блока анализ состояния; на фиг. 4 - блок-схема блока анализа сходимости; на фиг, 5 временная диаграмма работы устройства для вычисления функций. Устройство для вычисления элемен тарных функций (фиг.1) содержит три регистра 1-3, четыре сдвигате ля 4 - 7, семь сумматоров 8-14, два коммутатора 15 и 16, сумматор 17 по модулю два, первый блок. 18 па мяти и блок 19 управления.Первый вх блока 19 управления соединен с запускающим входом 20 устройства, управляюаций вход 21 которого соединен с вторым входом блока 19 управления, первым входом сумматора 17 по модулю два, управляющими входами первого 12 и второго 13 сумматоров и со старпшм разрядом адреса перво. го б.;ока 18 памяти, остальные разря ды адреса которого соединены с упра ляющими входами всех сдвигателей 47 и с первым выходом 22 блока 19 управления, второй выход 23 последнего соединен с тактирующими входами первого 1, второго 2 и третьего 3 регистррв, первые информационные входы которьк соединены с входной информационной шиной 24 устройства. Первый выход 25 этогоустройства со динен с выходом первого сумматора 12 и вторым информационньм входом первого регистра 1, выход которого соединен с информационными входами первого 4 и второго 5 сдвигателей .и первым информационным входом третье го сумматора 8. Выход сумматора 8 соединен с первым информационным ВХОДО1 первого сумматора 12, второй информационный вход которого соединен с выходом первого коммутатора 15, информационный вход которого соединен с выходом четвертого сумма тора 9, первый информационный вход которого соединен с выходом первого сдвигателя .4 и первым информационным входом пятого сумматора 11, а выход пятого сумматора 11 соединен с первым информационным входом второго сумматора 13, выход которого соединен с вторым выходом 26 устрой ства и с вторым информационным входом второго регистра 2. Выход этого регистра 2 соединен с информационными входами третьего 6 и четвертого 7 сдвигателей и с вторым информационным входом пятого сумматора 11, управляющий вход которого соединен с управляющим входом шестого сумматора 10. Выход шестого сумматора 10 соединен с информационньим входом второго коммутатора 16, выход которого соединен с вторым информационном входом второго сумматора 13. Выход третьего сдвигателя 6 соединен с вторым информационным входом четвертого сумматора 9, управляющий вход которого соединен с управляющим входом третьего сумматора 8 и с выходом сумматора 17 по модулю два. Второй вход последнего соединен с управляющими входами пятого 11 и шестого 10 сумматоров и управляют входом седьмого сумматора 14, выход которого соединен с третьим выходом 27 устройства и с вторым информационным входом третьего регистра 3. Выход этого регистра 3 соединен с первым информационным входом седьмого сумматора 14, второй информационный вход которого соединен с выходом первого блока 18 памяти, а выход второго сдвигателя 5,соединен с первым информационным входом щестого сумматора 10. Второй информационный вход этого сумматора 10 соединен с вторым информационным входом третьего сумматора 8 и выходом четвертого сдвигателя 7. Выход 28 блока 29 анализа сходимости соединен с третьим входом 30 блока 19 управления и со стробирующим входом 31 второго блока 32 памяти. Первый выход этого блока 32 памяти соединен с четвертым входом 33 блока 19 управления, первый выход 22 которого соединен с первым адресным входом третьего блока 34 памяти, с первым входом 35 блока анализа сходимости и адресным входом второго блока 32 памяти, второй выход которого соединен с информационным входом дешифратора 36. Выход дешифратора 36 через набор триггеров 37 соединен с вторым адресньм входом третьего блока 34 памяти, выход которого соединен с управляющими входами первого 15 и второго 16 коммутаторов. Управляющая шина 38 устройства соединена с первым входом 39 блока 40 анализа состояния, первый выход которого соединен с вторым входом блока 29 анализа сходимости. Третий

вход последнего соединен с запускающим входом 20 устройства, первый 25, второй 26 и третий 27 выходы которого соединены с вторым входом 41 блока 40 анализа состояния. Третий вход 42 этого блока соединен с входной информапионной шиной 24 устройства. Ут равляю п й вход седьмого сумматора 14 соединен с вторым выходом 43 блока 40 анализа состояНИН, четвертый вход которого соединен с управляющими входамипервого 1 второго 2 и третьего 3 регистров и с третьим выходом 44 блока 19 управления. Четвертый 45 и пятый 46 выходы блока 19 управления соединены соответственно с четвертым входом блока 29 анализа сходимости и стробирующим входом дешифратора 36, а второй выход 23 блока 19 управ ления соединен с пятым входом . блока 40 анализа состояния и пятым входом 47 блока 29 анализа сходимости.

Блок управления (фиг.2) содержит генератор 48 тактовых импульсов, счетчик 49 тактовых импульсов, три триггера 50 - 52, элементы И 53 - 57 элемент НЕ 58 и формирователь 59 импульсов. Вход формирователя 59 соединен с синхронизирующим входом первого триггера 50 и первым входом блока, выход формирователя 59 импульсов соединен с первым входом перво1-о элемента И 53. Выход этого элемента И 53 соединен с обнуляющим входом первого триггера 50, обнуляющим входом второго триггера 51, обнуляющим входом счетчика 49 тактовых импульсов и первым входом второго элемента И 54. Второй вход и выход последнего соединены соотвчзтственно с третьим . входом блока и обнуляющим входом третьего триггера 52. Прямой выход 60 триггера 52 соединен с первым управляющим входом этого же триггера и с первым входом третьего элемента И 55, а инверсный выход 61 - с первым входом четвертого элемента И 56. Выход четвертого элемента И 56 соединен с счетным входом счетчика 49 тактовых импульсов, информационные выходы которого соединены с первым выходом 32 блока управления, а выход переполнения счетчика 49 тактовых импульсов соединен с вторым входом первого элемента И 53.

Вход элемента НЕ 58 соединен с вторым входом блока, а выход - с: первым входом пятого элемента И 57. Выход элемента И 57 соединен с вторым входом четвертого элемента И 56 второй вход элемента И 57 соединен с инверсньм выходом второго триггера 5 1 . Прямой выход и синхронизирующий вход триггера 51 соответственно соединены с третьим выходом 44 блока и с первым тактовым выходом 62 генератора 48 тактовых импульсов вход которого соединен с прямым выходом первого триггера 50. Второй выход генератора 48 тактовых импульсов соединен с четвертым выходом 45 блока, третий выход генератора 48 соединен с вторым выходом 23 блока, третьим входом четвертого элемента И 56, вторым входом третьеГР элемента И 55 и синхронизирующим входом третьего триггера 52. . Второй управляющий вход триггера 52 соединен с четвертым входом 33 блока.Пятый выход 46 блока соединен с выходом третьего элемента И 55.

Блок анализа состояния (фиг.З) содержит два мультиплексора 63 и 64 четвертый блок 6: памяти, триггер 66 знака регистр 67, ц -1 элементов 68 сложения по модулю два, узел 69 приоритета и шифратор 70. Выход и входы шифратора 70 соответственно соединены с первым выходом 71 блока и с выходами узла 69 приоритета, входы которого соединены с выходами Ц-1 элементов 68 сложения по модулю два. Первые входы этих элементов 68 соединены с разрядными выходами регистра 67, а вторые между собой и со знаковым разрядом регистра 67.

Управляющий вход регистра 67 соединен с пятым входом блока и с синхронизирующим входом триггера 66 знака, а информационные входы регистра 67 - с выходами первого мультиплесора 63.

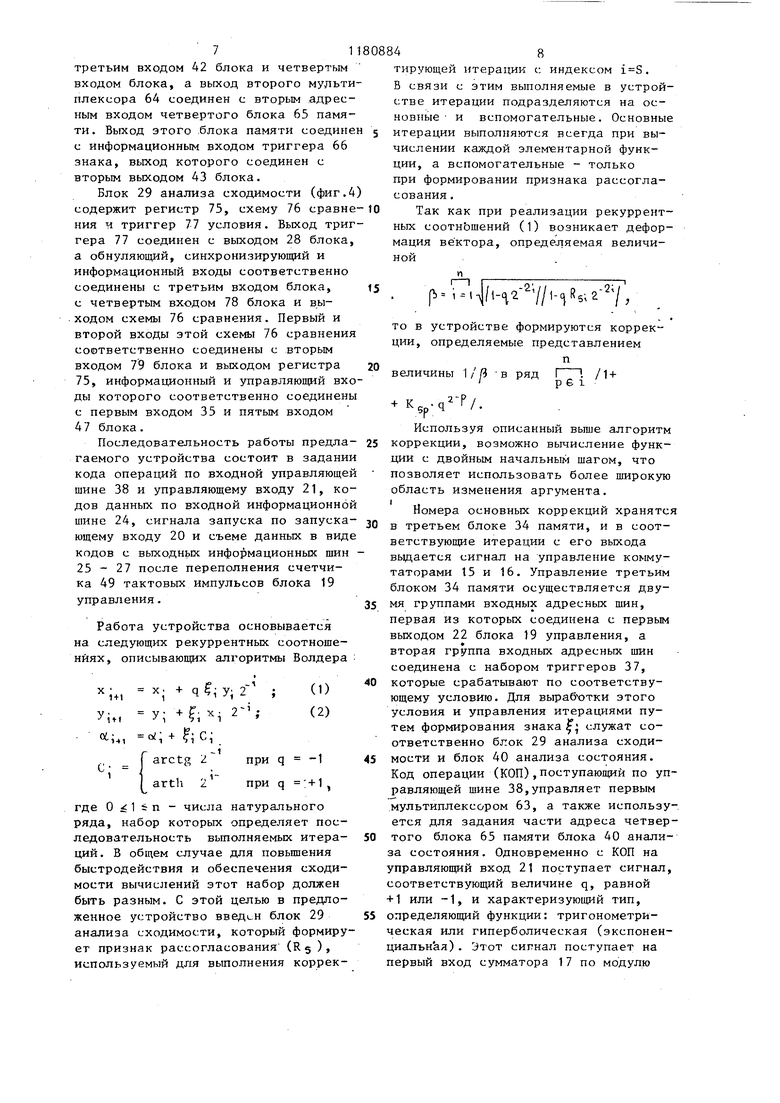

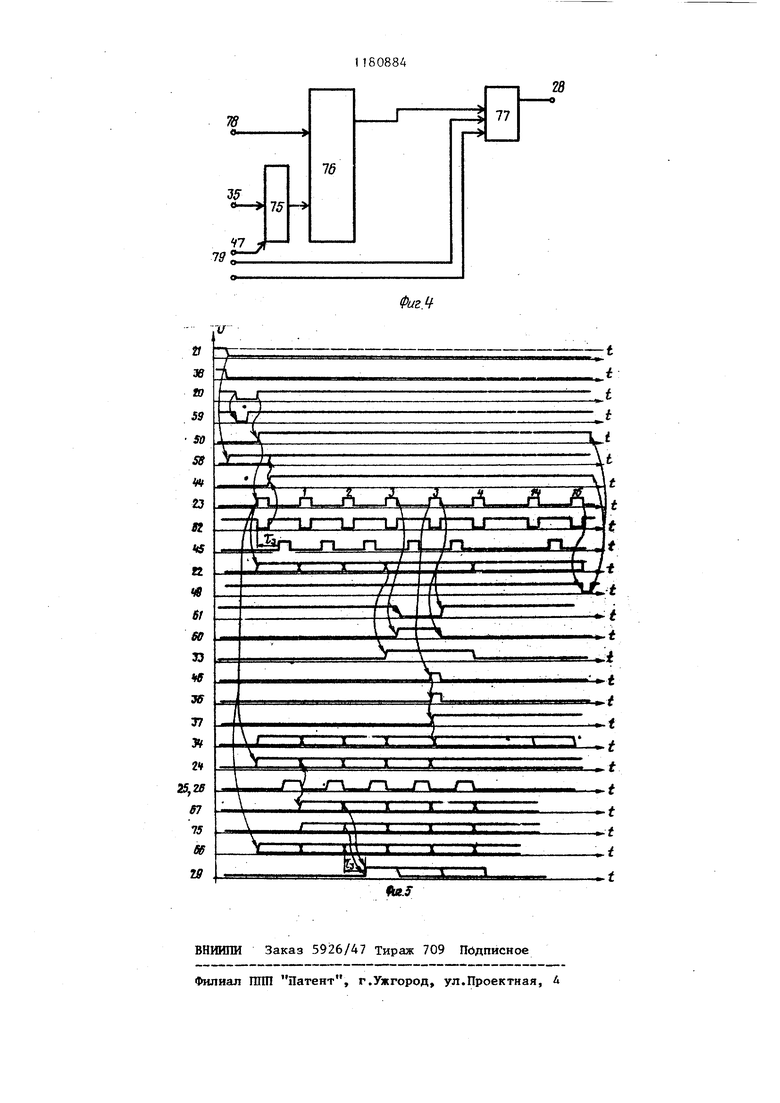

Управляющий вход этого мультиплексора 63 соединен с первым входом 39 блока и с первым адресным входом четвертого блока 65 памяти, а первый второй и третий информационные входы мультиплексора 63 соединены с вторым входом 41 блока и с первым входом 72 второго мультиплексора 64. Второй вход ,73 и управляющий вход 74 последнего соответственно соединены с третьим входом 42 блока и четвертым входом блока, а выход второго мульти плексора 64 соединен с вторым адресным входом четвертого блока 65 памяти. Выход этого блока памяти соедине с информационным входом триггера 66 знака, выход которого соединен с вторым выходом 43 блока. Блок 29 анализа сходимости (фиг.4 содержит регистр 75, схему 76 сравне НИН ч триггер 77 условия. Выход триг гера 77 соединен с выходом 28 блока а обнуляющий, синхронизирующий и информационный входы соответственно соединены с третьим входом блока, с четвертым входом 78 блока и выходом схемы 76 сравнения. Первый и второй входы этой схемы 76 сравнения соответственно соединены с вторым входом 79 блока и выходом регистра 75, информационный и управляющий вхо ды которого соответственно соединены с первым входом 35 и пятым входом 47 блока. Последовательность работы предла гаемого устройства состоит в задании кода операций по входной управляющей шине 38 и управляющему входу 21, ко дов данных по входной информационной шине 24, сигнала запуска по запускающему входу 20 и съеме данных в вид кодов с выходнь1х информационных шин 25-27 после переполнения счетчика 49 тактовых импульсов блока 19 управления. Работа устройства основывается на следующих рекуррентных соотношениях, описывающих алгоритмы Волдера , ,2 у; .,Х. 2 о;;+ с arctg 2 artli где О : 1 S- п - числа натурального ряда, набор которых определяет последовательность вьтолняемых итераций. В общем случае для повьппения быстродействия и обеспечения сходимости вычислений этот набор должен быть разным. С этой целью в предложенное устройство введин блок 29 анализа сходимости, который формирует признак рассогласования (Rg ), используемый для выполнения корректирующей итерации с индексом . В связи с этим выполняемые в устройстве итерации подразделяются на основные и вспомогательные. Основные итерации выполняются всегда при вычислении каждой элем ентарной функции, а вспомогательные - только при формировании признака рассогласования . Так как при реализации рекуррентных соотнЬшений (1) возникает деформация вектора, определяемая величиной . . то в устройстве формируются коррекции, определяемые представлением 1 / / - в ряд (771 /1+ величины Используя описанный выше алгоритм коррекции, возможно вычисление функции с двойным начальным шагом, что позволяет использовать более щирокую область изменения аргумента. Номера основных коррекций хранятся в третьем блоке 34 памяти, и в соответствуюш;ие итерации с его выхода выдается сигнал на управление коммутаторами 15 и 16. Управление третьим блоком 34 памяти осуществляется двумя группами входных адресных шин, первая из которых соединена с первым выходом 22 блока 19 управления, а вторая группа входных адресных шин соединена с набором триггеров 37, которые срабатывают по соответствующему условию. Для выраб отки этого условия и управления итерациями путем формирования знака служат соответственно блок 29 анализа сходимости и блок 40 анализа состояния. Код операции (КОП),поступающий по управляющей шине 38,управляет первым мультиплексором 63, а также используется для задания части адреса четвертого блока 65 памяти блока 40 аналиа состояния. Одновременно с КОП на правляюш;ий вход 21 поступает сигнал, оответствующий величине q, равной 1 или -1, и характеризующий тип, пределяющий функции: тригонометриеская или гиперболическая (экспонениальная) . Этот сигнал поступает на ервый вход сумматора 17 по модулю два и науправляющие входы сумматоров 12 и13, а также служит старшим разрядомадреса первого блока 18 памяти. КОП, поступая на мультиплексор 63 управляет выбором выходов с сумматора первого 12, второго 13 или седьмого 14 с целью анализа их выход ных кодов. КОП, поступая также на че вертый блок 65 памяти, совместно со знаками операндов, поступающих по третьему входу 42 блока и по второму входу 41 через мультиплексор 64, фор мирует стратегию выбора знака ; для заданной функции, т.е.. обеспечивает сходимость процессов вычислений во всех квадрантах пространства допусти мой области определения функций. Все отношения для выбора знаков во всех квадрантах для каждой функции записываются заранее в четвертом блоке 65 памяти. Сформированное значение знака итерации з аписывается с триггера 66 знака. С прямого плеча последнего значения поступает на второй вход сумматора 17 по модулю два, где совместно с управляющим сигналом (величиной q ) формирует соответству ющее значение сигнала для управления работой третьего 8 и четвертого 9 сумматоров. Сформированное значение 9i управляет также выбором операций пятого 11, шестого 10 и седьмого 11 сумматоров. Поступившее значение кода операнд на второй вход 41 блока 29 анализа сходимости через мультиплексор 63 записывается в регистр 67. Формирова ние порядка числа, записанного в регистре 67, осуществляется с помощью п - 1 элементов 68 сложения по моду лю два, узла 69 приоритета и шифрато ра 70. С последнего через первый выход 71 блока сформированное значение порядка числа поступает на схему 76 сравнения блока 29 анализа сходимости, где сравнивается с текущим значением номера итерации. Если текущий номер итерации меньше порядка числа, то вьфабатывается признак рассогласования, т.е. условия необхо димости повторения итерации. Сигнал признака рассогласования снимается с триггера 77 и подается через выход 28 блока на третий вход 30 блока 19 управления и на стробирующий вход 31 второго блока 32 памяти. Последовательность работы блока 19 управления заключается в следующем (фиг.5). На подготовительном этапе по управляющей шине 38 и управляющему входу 21 задается КОП и величина q, равная +1 или -1, что соответствует 1 или 0 в зависимости от вида вычисляемой функции, з. затем по запускающему входу 20-импульс, по которому происходит обнуление триггеров 50 и 51 и счетчика 49 тактовьк импульсов, и установка триггера 50 в состояние 1. Последний разрешает генератору 48 тактовых импульсов формирование серии импульсов прямых, инверсных и задержанных на некоторое оз относительно прямых, обусловливая функционирование устройства. По переднему фронту первого импульса (23) происходит запись в регистры 1-3 исходной информации о данных 2 1, Z 2,Т, поступающих по входной информационной шине 24 устройства. По этому же импульсу происходит запись в триггер 66 знака величины f, (66), считанной с четвертого блока 65 памяти. Формирование разрешения на прохождение тактирующим импульсов (23) на счетчик 49 тактовьк импульсов обуславливается наличием на втором входе четвертого элемента И 56 логической 1, снимаемой с пятого элемента И.57. Если величина q +1 (гиперболическая функция), т.е. соответствующий ей сигнал 1 поступает на управляющий вход 21, то на выходе элемента И 57 будет логическая 1, что дает разрешение на запись в счетчик 49 тактовых импульсов тактовых импульсов (23), а по переднему фронту первого инверсного импульса (62) формируется строб (44) на начало процесса вычисления, что характеризует второй этап работы блока управления. Если q -1, т.е. ей соответствует сигнал О, то вычисления в устройстве начинают также.как и при с . той разницей, что в;счетчик 49 тактовых импульсов первый импульс записан не будет (22), и произведенная итерация соответствует нулевому шагу. ,. В случае появления признака рассогласования (29) и наличия сигнала (33) с второго блока 32 памяти триггер. 52 устанавливается в 1 и сигналом О со своего инверсного плеча запрещает прохождение тактового импульса на счетчик импульсов, При этом формируется стробирующий сигнал (46), который поступает на дешифратор 36. В зависимости от того, при каком номере итерации произошло рассогласование и появление сигнала (33), на выходе дешифратора формируется соответствующий сигнал (36), который обуславливает срабатывание соответствующего триггера (37) из набора триггеров 37. При этом изменяется адресация третьего блока 34 памяти и, соответственно, последyюlЦIie номера корректирующих итераций. Опи ;анным выше методом харак088412

теризуется третий этап работы блока управления - этап дополнительных итераций. Возврат к второму этапу работы блока управления происходит при исчезновении либо сигнала признака рассогласования (29), либо исчезновении сигнала (33), снимаемого со второго блока памяти 32, в котором хранятся номера дополнительных итераций.

При появлении сигнала переполнения (49), снимаемого с счетчика 49 импульсов, вычислительный процесс заканчивается и элементы блока

15 управления устнавливаются в исходное начальное положение. 45 23Ц1

Д

1Г

1 180884

22

Й:

43

50

46

&

-е

52

61

Л

га

57

«Ил

чг

7J

72

57

Л5

- -

- -- -

Л

30

V3

-в

66

55

н

7/

7(

| Устройство для вычисления координат вектора на плоскости | 1975 |

|

SU693378A1 |

| G 0.6 F 15/20, 1979 | |||

| Устройство для вычисления тригонометрических функций | 1980 |

|

SU928348A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-23—Публикация

1984-04-24—Подача