Изобретение относится к вычисли тельной технике. Известно устройство для проверки логических субблоков, содержащее счетчик, выходной регистр, блок анализа и индикации, узел контроля, узел управления и коммутатора fl.. Недостатком известного устройства являются ограниченные функциональ ные В9зможности. Наиболее близким к предлагаемс 1у по технической сущности является уст ройство для контроля цифровых узлов содержащее- блок ввоДа, блок пгшяти, коммутатор, блок сравнения, блох индикацип, блок управления и регистр настройки, при этом первый выход бло ка ввода соединен с входом блока памяти, выход которого подключен к первому входу коммутатора, выходами соединенного с внешними контактгми контролируемого узла, второй выход блока ввода соединен с входом блока управления,- выход которого подключен соответственно к управляющим вхо дам блока ввода, блока памяти и блока индикации, вход регистра настройки соединен с блоком сравнения 21. Недостатком известного устройства является недостаточная точность и диапазон контроля. Цель изобретения - повышение точности контроля. . Для достижения поставленной цели в устройство для контроля цифровых блоков, содержащее коммутатор, блок индикации и накопитель, причем первый выход коммутатора подключен к первому входу блока индикации, второй и третий выходы коммутатора подключены соответственно к первому и второму входам накопителя введены адаптер, блок переключения, дополнительный коммутатор, блок питания, блок фиксации тестового слова, при этом вход-выход адаптера подключен к контролируемому объекту, первый вход адаптера соединен с выходом блока переключения, первый вход которого -подключен к четвёртому выходу коммутатора, пятый выход которого соединен со вторым входом адаптера, выход которого соединен с первым входом ксииму атора, второй вход которого соединен с первым выходом дополиительного коммутатора, второй выход которого подключен к первому входу блока фиксации тестового елова, выход которого соединен с третьи входом коммутатора, четвертый вход которого является тестовым входом устройства, второй вход блока переключения соединен с выходом блока питания, вход которого подключен к третьему выходу дополнительного коммтатора, четвертый выход которого соединен с третьим входом блока переключения, первый вход дополнительного коммутатора является информационным входом устройства, объединен со вторым входом блока фиксации тестового слова и поключен к третьему выходу коммутатора, второй вход дополнительного коммутатора является управляющим входом устройства, пятый выход дополнительного коммутатора соедин.ен с третьим входом накопителя, шестой выход дополнителного коммутатора подключен ко второму входу блока индикации.

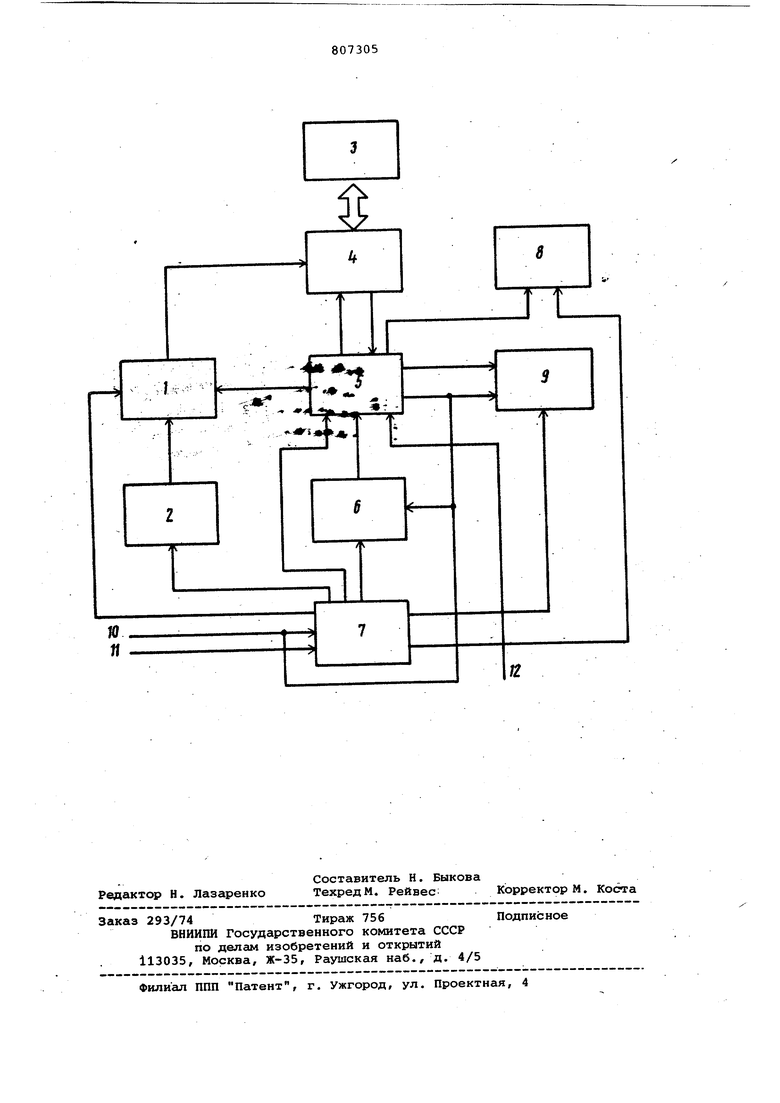

На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит блок 1 переключения, блок 2 питания, контролируемый объект 3, ад-аптер 4, коммутатор 5, блок 6 фиксации тестового слова, коммутатор 7, блок 8 индикации, накопитель 9, информационный вход 10, управлягадий вход 11 и тактовьт вход 12.

Первый вход блока 1 переключения предназначен для подачи и отключения от адаптера 4, питающего контролируемый объект 3, напряжения. Блок 2 питания служит для подачи питающего напряжения на контролируемый объект 3, причем уровень питающего напряжения может изменяться в требуемом для контроля диапазоне. Адаптер 4 предназначен для сопряжения устройства с контролируемым объектом, а для подачи на объект тестового слова и тактовых импульсов служит коммутатор 5. Блок б фиксации тестового слова предназначен для формирования тестового слова по накопленным изменениям. Ксммутатор 7 служит для распределения и обработки данных, поступаиицих с информационного входа 10 и управляющего входа 11, и для формирования управляющих воздействий на перечисленные блоки в устройстве.

Накопитель 9 предназначен для импульсов на контролируемом выходе с входа 12 контролируемого объекта 3. Блок 8 индикации предназ1Я указания координат неиспpaBHOCT iianpHMep обрыв, короткое эа1Факание JI..H хода контроля контролируемого о&&«цста 3.

Информационный вхо -адпрвдназначен для подачи на устройство-лунных о состоянии очередной операции KI . роля и съема информации о состоянии блоков устройства, управлякиций вход

11 которого служит для подачи на него сигналов управления и взаимодействия, например от ЭВМ. По тактовому входу 12 устройства производится подключение к устройству генератора тактовых импульсов.

Устройство работает следукяцим образом.

Все операции выполняются при подаче на управляющий вход 11 команд действие или контроль. На первоМ такте обеих команд со стороны внешнего управляющего устройства на информационный вход 10 выставляется информация о выборе данного устройства для контроля и вид операции которую устройство должно выполнить Затем на управляющий вход 11 подается 1-я часть команды,, коммутатор 7 подготавливает данные для управлени блоками устройства.

На втором такте команды действи внешнее управлякнцее Устройство сменяет инфо амацию на информационном входе 10 и подает на управляющий вход 11 2-ю часть команды. При этом коммутатор 7 подает подготовленные данные на входы блоков устройства, и операции выполняются.

На втором такте команды контроль внешнее управляющее устройство снимает с информационного входа 10 информацию и подает на управляющий вход 11 2-ю часть команды. При этом KONDnytaTop 7 подает подготовленные данные на входы блоков устройства. Выполнение операции заключается в подаче на информационный вход 10 информации о состоянии блоков устройства в сторону внешнего управляющего устройства.

Проверка контролируемого блока выполняется в 2 этапа. 1-й этап начальный контроль, 2-й этап - рабочая проверка.

На первом этапе коммутатор 7 подает на блок 1 переключения сигнал о подключении к адаптеру 4 выходов ксхлмутатора 5, соответствующих входам подачи питания на проверяемый цифровой блок 3. Блок 6 фиксации тестового слова заполняется значениями пассивных сигналов для контролируемого объекта 3, коммутатор 5 полностью подключается к блоку б фиксации тестового слова., после чего к входу 12 подключается конролируемый объект 3. Таким образом, на всех входах контролируемого объекта 3 установлены пассивные сигналы, и с него снято питающее напряжение. Затем происходит последовательный прогон активного сигнала, начиная от первого контакта контролируемого объекта 3 до последнего, причем после подачи активного сигнала на каждый контакт происходит нтроль состояния остальных контакTo& C L целью выяснения коротких замыканий на контролируемом объекте 3 контактами. В конце 1-го этапа блок 6 фиксации тестового слова устанавливается в пассивное состояние, коммутатор 7 подает на блок 1 переключения сигнал о подключении к адаптеру 4 номинального напряжения для работы проверяемого цифрового блока.

2-й этап состоит из трех циклов, отличающихся лишь значениями питающего контролируемый объект 3 напряжения, номинальное, минимально допустимое и максимально допустимое. Установку значений питающего напряжения на блоке 2 питания производит коммутатор 7. Выполнение цикла состоит в выполнении необходимого количества микротестов, заключающихся в формировании блоком б тестового слова путем накопления изменений и в проведении контроля состояния, всех контактов контролируемого объекта 3,

Во время проверки на блоке 8 индикации высвечивается состояние всех контактов контролируемого объекта 3 и координаты проверки, т.е. номер микротеста, номер контакта, на котором сформировался ошибочный сигнал. Состояние контактов индицируется непосредственно с коммутатора 5, а координаты проверки индицируются посредством подачи их с коммутатора 7 по окончании ангшиза ситуации внешним управляющим устройством.

Для проверки схем .типа счетчики, регистры коммутатор 5 переключает в сторону контактируемого объекта 3 при подаче соответствукядего управляющего воздействия от коммутатора 7 тактовый вход 12 на указанные в микротесте контакты.

Для проверки схем типа генератор, формирователь коммутатор 5 переключает в сторону накопителя . 9 при подаче соответствующего управляющего воздействия от .коммутатора 7 указанные в микротесте контакты, после чего на динамический накопитель 9 подается управляющее воздействие от коммутатбра 7 и накопитель 9 передает на двухнаправленный информационный вход 10 в сторону внешнего управляющего устройства накопленную информацию.

Изобретение обеспечивает повышег ние точности контроля за счет контроля цифровых блоков на всем допустимом диапазоне питающего напряжения после введения в устройство управляемого блока питания. Кроме того обеспечивается автоматический предварительный контроль замыкания между контактами проверяемого цифрово-го блока за счет введения в устройство блока переключения.

Формула изобретения

Устройство для контроля цифровых блоков, содержащее коммутатор, блок индикации и накопитель, причем первый, выход коммутатора подключен к

0 первому входу блока индикации, второй и третий выходы коммутатора подключены соответственно к первому и второму входам накопителя, отличающееся тем, что, с целью повышения точности контроля, устрой5ство содержит также адаптер, блок переключения, дополнительный коммутатор, блок питания, блок фиксации тестового слова, при этом вход-выход адаптера подключен к контролируемо0му объекту, первый вход адаптера соединен с выходом блока переключения, первый вход которого подключен к четвертому выходу коммутатора, пятый выход которого соединен со вто5рым входом адаптера/ выход которого соединен с первым входом комму татора, второй вход которого соединен с первьм выходом дополнительного коммутатора, второй выход которого

D подключен к первому входу блока фиксации тестового слова, выход которого соединен с третьим входом коммутатора, четвертый вход которого является тестовым входом устройства,

5 второй вход блока переключения сое- динен с выходом блока питания, вход которого подключен к третьему выходу дополнительного коммутатора, четвертый выход которого соединен с

0 третьим входом блока переключения, первый вход дополнительного коммутатора является информационным входом устройства, объединен со вторым входом блока фиксации тестового слова и подключен к третьему выходу комму5т атора, второй вход дополнительного коммутатора является управляющим BXQ устройства, пятый выход дополнительного коммутатора соединен с третьим входом накопителя, шестой

0 выход дополнительного ком татора подключен ко второму входу блока индикации .

Источники информации,

5 Принятые во внимание при экспертизе

1.Авторское свидетельство СССР 477412, кл. 6 Об Е 11/00, 1976.

2.Авторское свидетельство СССР 198619, кл. G Об F 11/00, 1974 (прототип).

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики дискретных объектов | 1983 |

|

SU1109756A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| Многоканальное устройство для контроля систем управления | 1985 |

|

SU1345200A1 |

| КОМАНДНО-СТРЕЛЬБОВАЯ ИНФОРМАЦИОННО-УПРАВЛЯЮЩАЯ СИСТЕМА БЕРЕГОВОГО БАЗИРОВАНИЯ | 2000 |

|

RU2176818C1 |

| Устройство для проверки функционирования логических схем | 1980 |

|

SU955072A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Устройство для контроля логических блоков | 1983 |

|

SU1262506A1 |

| Устройство для диагностирования группы логических узлов | 1987 |

|

SU1520520A1 |

| Многоканальное устройство тестового контроля логических узлов | 1985 |

|

SU1265778A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ДЛЯ ОПРЕДЕЛЕНИЯ ИНФОРМАЦИОННЫХ СВОЙСТВ ТЕСТА | 1991 |

|

RU2068580C1 |

Авторы

Даты

1981-02-23—Публикация

1979-01-08—Подача