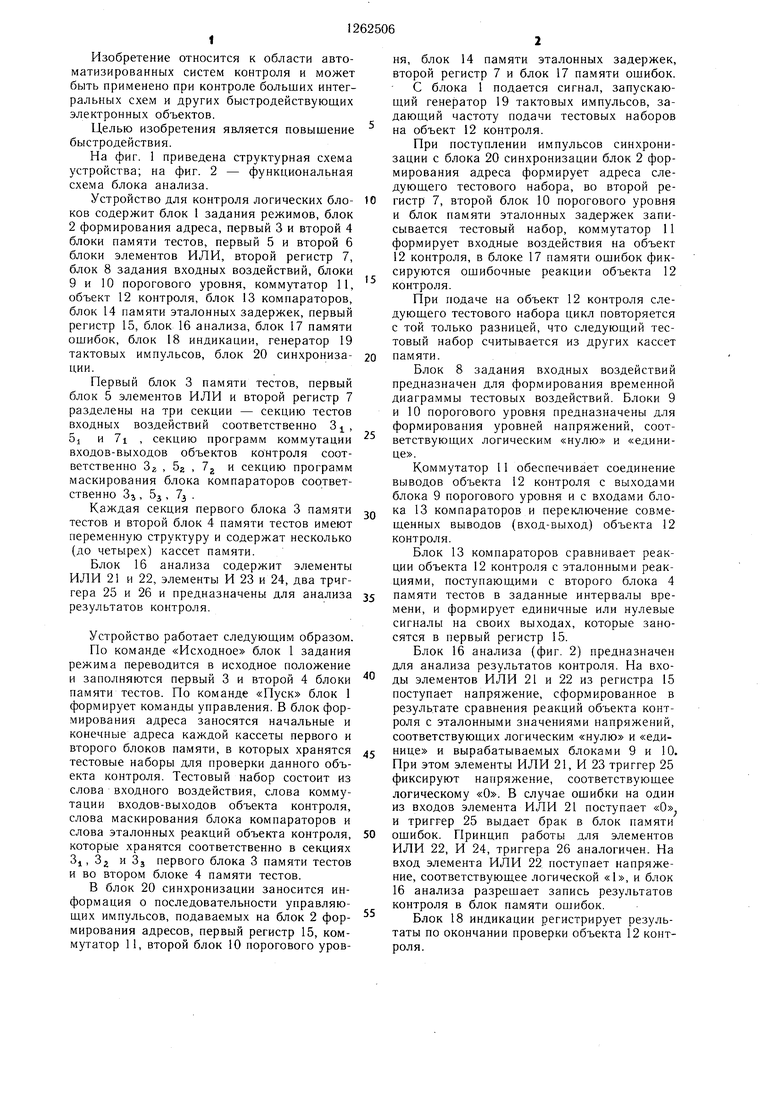

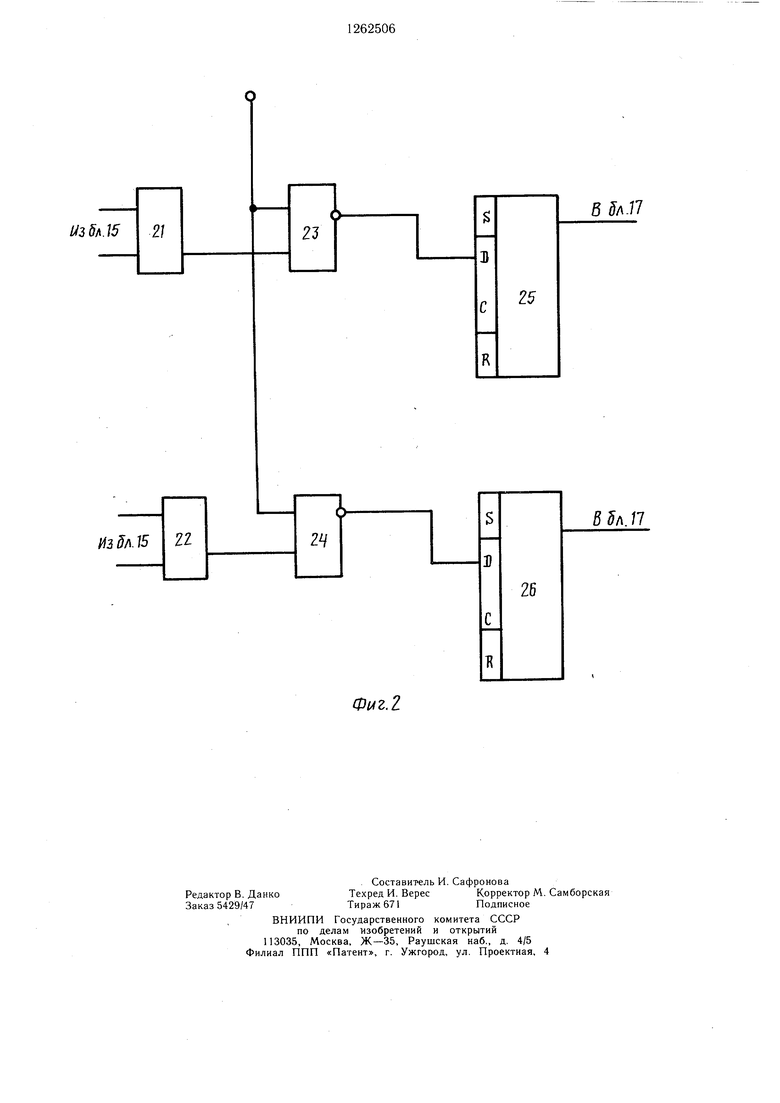

Изобретение относится к области автоматизированных систем контроля и может быть применено при контроле больших интегральных схем и других быстродействующих электронных объектов. Целью изобретения является повышение быстродействия. На фиг. 1 приведена структурная схема устройства; на фиг. 2 - функциональная схема блока анализа. Устройство для контроля логических блоков содержит блок I задания режимов, блок 2 формирования адреса, первый 3 и второй 4 блоки памяти тестов, первый 5 и второй 6 блоки элементов ИЛИ, второй регистр 7, блок 8 задания входных воздействий, блоки 9 и 10 порогового уровня, коммутатор 11, объект 12 контроля, блок 13 компараторов, блок 14 памяти эталонных задержек, первый регистр 15, блок 16 анализа, блок 17 памяти ошибок, блок 18 индикации, генератор 19 тактовых импульсов, блок 20 синхронизации. Первый блок 3 памяти тестов, первый блок 5 элементов ИЛИ и второй регистр 7 разделены на три секции - секцию тестов входных воздействий соответственно 3, 5i и 7i , секцию программ коммутации входов-выходов объектов контроля соответственно Зг , 5г , 7 и секцию программ маскирования блока компараторов соответственно 3j , 5з , 7з . Каждая секция первого блока 3 памяти тестов и второй блок 4 памяти тестов имеют переменную структуру и содержат несколько (до четырех) кассет памяти. Блок 16 анализа содержит элементы ИЛИ 21 и 22, элементы И 23 и 24, два триггера 25 и 26 и предназначены для анализа результатов контроля. Устройство работает следуюш,им образом. По команде «Исходное блок 1 задания режима переводится в исходное положение и заполняются первый 3 и второй 4 блоки памяти тестов. По команде «Пуск блок 1 формирует команды управления. В блок формирования адреса заносятся начальные и конечные адреса каждой кассеты первого и второго блоков памяти, в которых хранятся тестовые наборы для проверки данного объекта контроля. Тестовый набор состоит из слова входного воздействия, слова коммутации входов-выходов объекта контроля, слова маскирования блока компараторов и слова эталонных реакций объекта контроля, которые хранятся соответственно в секциях 3i, 32 и Зз первого блока 3 памяти тестов и во втором блоке 4 памяти тестов. В блок 20 синхронизации заносится информация о последовательности управляющих импульсов, подаваемых на блок 2 формирования адресов, первый регистр 15, коммутатор 11, второй блок 10 порогового уровня, блок 14 памяти эталонных задержек, второй регистр 7 и блок 17 памяти ошибок. С блока 1 подается сигнал, запускающий генератор 19 тактовых импульсов, задающий частоту подачи тестовых наборов на объект 12 контроля. При поступлении импульсов синхронизации с блока 20 синхронизации блок 2 формирования адреса формирует адреса следующего тестового набора, во второй регистр 7, второй блок 10 порогового уровня и блок памяти эталонных задержек записывается тестовый набор, коммутатор 11 формирует входные воздействия на объект 12 контроля, в блоке 17 памяти ощибок фиксируются ощибочные реакции объекта 12 контроля. При нодаче на объект 12 контроля следующего тестового набора цикл повторяется с той только разницей, что следующий тестовый набор считывается из других кассет памяти. Блок 8 задания входных воздействий предназначен для формирования временной диаграммы тестовых воздействий. Блоки 9 и 10 порогового уровня предназначены для формирования уровней напряжений, соответствующих логическим «нулю и «единице. Коммутатор 11 обеспечивает соединение выводов объекта 12 контроля с выходами блока 9 порогового уровня и с входами блока 13 компараторов и переключение совмещенных выводов (вход-выход) объекта 12 контроля. Блок 13 компараторов сравнивает реакции объекта 12 контроля с эталонными реакциями, поступающими с второго блока 4 памяти тестов в заданные интервалы времени, и формирует единичные или нулевые сигналы на своих выходах, которые заносятся в первый регистр 15. Блок 16 анализа (фиг. 2) предназначен для анализа результатов контроля. На входы элементов ИЛИ 21 и 22 из регистра 15 поступает напряжение, сформированное в результате сравнения реакций объекта контроля с эталонными значениями напряжений, соответствующих логическим «нулю и «единице и вырабатываемых блоками 9 и 10. При этом элементы ИЛИ 21, И 23 триггер 25 фиксируют напряжение, соответствующее логическому «О. В случае ощибки на один из входов элемента ИЛИ 21 поступает «0 и триггер 25 выдает брак в блок памяти ощибок. Принцип работы для элементов ИЛИ 22, И 24, триггера 26 аналогичен. На вход элемента ИЛИ 22 поступает напряжение, соответствующее логической «1, и блок 16 анализа разрешает запись результатов контроля в блок памяти ошибок. Блок 18 индикации регистрирует результаты по окончании проверки объекта 12 контроля. Формула изобретения Устройство для контроля логических блоков, содержащее два регистра, два блока памяти тестов, блок памяти эталонных задержек, блок анализа, блок индикации, блок компараторов, коммутатор, блок формирования адреса, блок задания режимов, причем адресные входы блоков памяти тестов подкл-ючены к первому выходу блока формирования адреса, второй выход которого соединен с первым входом блока индикации, входы первого и второго блоков памяти тестов являются входами задания тестовых воздействий устройства, первый выход блока задания режима подключен к входу задания начального и конечного адресов блока формирования адреса, отличающееся тем, что, с целью повышения быстродействия, в него введены два блока порогового уровня, два блока элементов ИЛИ, блок задания входных воздействий, блок синхронизации, генератор тактовых импульсов и блок памяти ошибок, причем вход задания частоты импульсов блока синхронизации и вход запуска генератора тактовых импульсов подключены соответственно к второму и третьему выходам блока задания режима, входы которого являются входами начальной установки, «Пуск и «Стоп устройства, входы синхронизации первого блока порогового уровня, блока памяти эталонных задержек, блока памяти ошибок, блока формирования адреса, второго регистра, коммутатора объединены и подключены к выходу блока синхронизации, тактовый вход которого соединен с выходом генератора тактовых импульсов, выходы первого блока памяти тестоб соединены с соответствуюшими входами первого блока элементов ИЛИ, выходы которого соединены с соответствуюшими разрядными входами второго регистра, разрядные выходы которого соединены соответственно с входом блока задания входных воздействий, первым информационным входом коммутатора и входом максирования блока компараторов, выход блока задания входных воздействий подключен к входу первого блока порогового уровня, выход которого соединен с управляюшим входом коммутатора, второй 1нформационный вход которого соединен с выходом контролируемого логического блока, выход коммутатора подключен к первому информационному входу блока компараторов, второй информационный вход которого подключен к выходу второго блока пороговогоуровня, управляющий вход блока компараторов соединен с выходом блока памяти эталонных задержек, выход блока компараторов подключен к входу первого регистра, выход которого соединен с первым информационным входом блока памяти ошибок и с входом блока анализа, выход которого соединен с вторым информационным входом блока памяти ошибок, выход блока памяти ошибок соединен с вторым входом блока индикации, выходы второго блока памяти тестов подключены к соответствующим входам второго блока элементов ИЛИ, выход которого соединен с информационными входами второго блока порогового уровня и блока памяти эталонных задержек, блок анализа содержит два триггера, два элемента И и два элемента ИЛИ, причем выходы первого и второго элементов ИЛИ соединены с первыми входами соответственно первого и второго элементов И, инверсные выходы которых подключены к D-входам первого и второго триггеров соответственно, входы перрого и второго элементов ИЛИ и вторые входы элементов И являются информационными входами блока анализа, а выходы триггеров являются выходами блока анализа.

Из5А.15

2.

2

В 5лЛ7

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля объектов | 1985 |

|

SU1363141A1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Устройство для контроля логических схем | 1985 |

|

SU1252786A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО КОНТРОЛЯ | 1991 |

|

RU2015523C1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Устройство для контроля и диагностики дискретных объектов | 1983 |

|

SU1109756A1 |

| Устройство для контроля и диагностики гибридных блоков | 1981 |

|

SU957212A1 |

| Устройство для формирования тестовых воздействий | 1985 |

|

SU1334139A1 |

Изобретение относится к автоматизированным системам контроля и может быть применено при контроле больших интегральных схем и других быстродействующих электронных объектов. Цель изобретения - повышение быстродействия. Цель достигается за счет введения в устройство двух блоков 9 и 10 порогового уровня, двух блоков 5 и 6 элементов ИЛИ, блока 8 задания входных воздействий, блока 20 синхронизации, генератора 19 тактовых импульсов, блока 17 памяти ошибок. 2 ил. (Л to О5 IN:) сд о О5

.г

| ОПИСАНИЕ ИЗОБРЕТЕНИЯ | 0 |

|

SU377738A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| УСТРОЙСТВО для КОНТРОЛЯ ИНТЕГРАЛЬНЫХ СХЕМ | 1971 |

|

SU419852A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-10-07—Публикация

1983-09-27—Подача