(54) УСТРОЙСТВО ДЛЯ ПРОВЕРКИ ФУНКЦИОНИРОВАНИЯ ЛОГИЧЕСКИХ СХЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических схем | 1986 |

|

SU1381517A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1278855A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для обнаружения и локализации неисправностей цифровых блоков | 1982 |

|

SU1067507A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1317440A1 |

| Устройство для контроля параллельных микропроцессорных интерфейсов | 1982 |

|

SU1040489A1 |

| Устройство для тестового контроля цифровых блоков | 1983 |

|

SU1136169A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1141414A1 |

| Устройство для контроля цифровых блоков | 1981 |

|

SU1037259A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

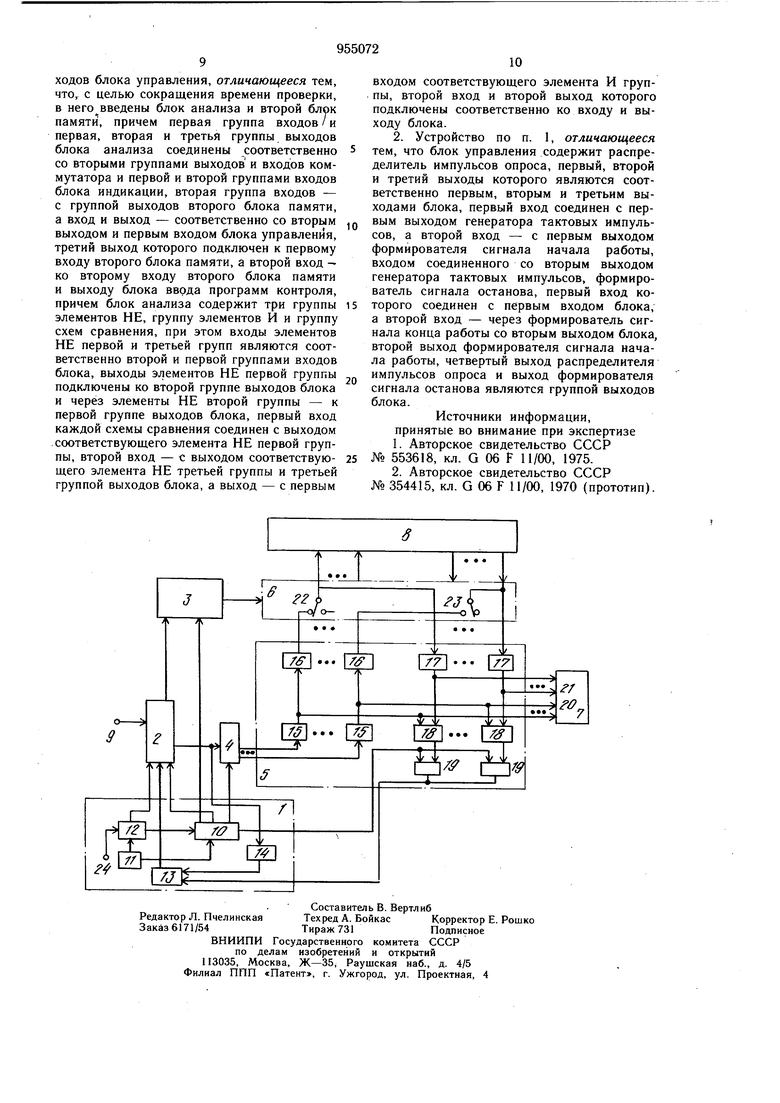

Изобретение относится к вычислительной технике и может быть использовано при тестовой диагностике неисправностей и контроле логических схем: типовых элементов замены, схем цифровых приборов, больших интегральных схем. Известны устройства для контроля схем, которые обеспечивают поочередную проверку каждой схемы, входящей в состав объекта контроля, путем сравнения ее входных сигналов с выходными сигналами однотипной эталонной схемы, на входе которой прикладываются сигналы, снимаемые со входов контролируемой схемы объекта 1. Недостаток данных устройств - ограниченные функциональные возможности, так как они позволяют зафиксировать неисправность при условии использования однотипной эталонной схемы. Наиболее близким к предлагаемому по технической сущности является устройство для проверки функционирования логических схем, обеспечивающее тестовую проверку функционирования логических схем с помощью поочередного сравнения сигналов контролируемых выходов проверяемого устройства с эталонными выходными сигналами в блок;е сравнения на максимальной рабочей частоте и содержащее блок ввода данных, выходом соединенный с первым входом блока входных и эталонных выходных сигналов, выход которого подключен через коммутатор к контролируемой схеме и через блок сравнения к блоку индикации, блок управления, подключенный своими выходами ко входам блока ввода данных, блока входных и эталонных выходных сигналов, коммутатору и блоку индикации, блок контролируемых выходов, выход которого подключен ко второму входу схемы сравнения, один вход - к выходу блока ввода, другой - к выходу блока управления, блоки регистров, причем вход одного блока регистров подключен к выходу блока входных и эталонных выходных сигналов, а вход другого блока регистров - к выходу блока контролируемых выходов, одни выходы блоков контрольных регистров подключены к соответствующим входам блока индикации, другие выходы - ко входам блока управления, управляющие входы - к выходам блока управления, а выходы сравнения - к соответствующим выходам блока ввода 2. Недостаток известного устройства состоит в больших временных затратах на проверку, что обусловлено необходимостью поочередного сравнения сигналов контролируемых выходов проверяемого устройства с эталонными выходными сигналами на каждом такте работы устройства. Кроме того, работа устройства не может быть прекращена при обнаружении устойчивого отказа типа замыкания входов на землю, что вызывает потери времени на тестирование заведомо неисправной схемы. Цель изобретения - сокращение времени проверки. Поставленная цель достигается тем, что в устройство, содержащее блок индикации и коммутатор, первые группы входов и выходов которого соответственно являются группами входов и выходов устройства, а вход соединен с выходом первого блока памяти, первым входом соединенного с первым выходом блока управления, а вторым - с первым выходом блока ввода и хранения программ контроля, вход которого является входом устройства, а группа входов подключена к группе выходов блока управления, введены блок анализа и второй блок памяти, причем первая группа входов и первая, вторая и третья группы выходов блока ана-лиза соединены соответственно со вторыми группами выходов и входов коммутатора и первой и второй группами входов блока индикации, вторая группа входов - с группой выходов второго блока памяти, а вход и выход - соответственно со вторым выходом и первым входом блока управления, третий выход которого подключен к первому входу второго блока памяти, а второй вход -ко второму входу второго блока памяти и выходу блока ввода и хранения программ контроля, причем блок анализа содержит три группы элементов НЕ, группу элементов И и группу схем сравнения, при этом входы элементов НЕ первой и третьей групп являются соответственно второй и первой группами входов блока, выходы элементов НЕ первой группы подключены ко второй группе выходов блока и через элементы НЕ второй группы к первой группе выходов блока, первый вход каждой схемы сравнения группы соединен с выходом соответствующего элемента НЕ первой группы, второй вход - с выходом соответствующего элемента НЕ третьей группы и третьей группой выходов блока, а выход - с первым входом соответствующего элемента И группы, второй вход и выход которого подключены соответственно ко входу и выходу блока. Блок управления содержит распределитель импульсов опроса, первый, второй и третий выходы которого являются соответственно первым, вторым и третьим выходами блока, первый вход соединен с первым выходом генератора тактовых импульсов, а второй вход - с первым выходом формирователя сигнала начала работы, входом соединенного со вторым выходом генератора тактовых импульсов, формирователь сигнала останова, первый вход которого соединен с первым входом блока, а второй вход - через формирователь сигнала конца работы со вторым выходом блока, второй выход формирователя сигнала начала работы, четвертый выход распределителя импульсов опроса и выход формирователя сигнала останова являются группой выходов блока. На чертеже представлена блок-схема устройства. Предлагаемое устройство содержит блок 1 управления, блок 2 ввода программ контроля, блоки 3 и 4 памяти, блок 5 анализа, коммутатор 6, блок 7 индикации, проверяемую логическую схему 8 и вход 9 устройства. Блок I управления содержит распределитель 10 импульсов опроса, генер атор 11 тактовых импульсов, формирователь 12 сигнала начала работы, формирователь 13 сигнала останова и формирователь 14 сигнала конца работы. Блок 5 анализа содержит элементы НЕ 15 16 и 17 первой, второй и третьей групп, схемы 18 сравнения группы и элементы И 19 группы. На чертеже обозначены также входы 20 и 21 первой и второй групп блока индикации, контакты 22 и 23 коммутатора 6 и вход 24 пуска формирователя 12 сигнала начала работы. Устройство позоляет проводить контроль работоспособности логической схемы при проверке элементов схемы на переключение из состояния «1 в состояние «О и наоборот. Тест для неисправности рассматривают, во-первых, как последовательность тестовых служебных и информационных наборов, при подаче которых переключение сигналов в блоке 5 анализа, по крайней мере, с одного контролируемого входа исправной схемы отличается от переключения сигналов в блоке 5 контролируемого входа схемы с неисправностью, причем неисправность заключается в замыкании контролируемого входа схемы на землю. Во-вторых, при подаче наборов происходит переключение сигналов, по крайней мере, одного контролируемого выхода исправной схемы в отличие от переключения сигналов в блоке 5 контролируемого выхода схемы с неисправностью. Блок 1 управления реализует задание на выборку определенной программы контроля для проверяемого устройства из блока 2 в блоки 3 и 4, формирует импульсы опроса для блоков 3, 4 и 5, производит останов тест-программы в такте, в котором возникли условия останова, и осуществляет .запуск тест-программы. Блок 2 ввода программ контроля обеспечивает ввод и хранение программ контроля. выдает тестовые последовательности информационных входных и эталонных выходных сигналов в блок 4, а служебных установочных сигналов в блок 3. Первый блок 3 памяти реализует установку и хранение одной из последовательностей служебных сигналов и обеспечивает ее параллельный ввод в коммутатор 6. Второй блок 4 памяти осуществляет хранение одной последовательности информационных входных и последовательности эталонных выходных сигналов, реализует параллельный ввод информационных входных сигналов через блок 5 по каналам коммутатора 6 на определенные входные контакты контролируемой схемы 8, обеспечивает параллельный ввод эталонных выходных сигналов в блок 5, который предназначен для обнаружения состояния, при котором требуется произвести останов тест-программы, а также при неисправности контролируемой логической схемы реализует выдачу сигналов о неисправности в блок 7 индикации и в блок управления для останова тестпрограммы контроля. Коммутатор 6 обеспечивает подключение к определенным каналам коммутатора входных и выходных контактов проверяемой логической схемы, а также соответствующих входов и выходов блока 5. Блок 7 индикации неисправности проверяемого устройства фиксирует неисправность с точностью до номера контакта входного или выходного проверяемой логической схемы. Проверяемая логическая схема должна иметь не более М внещних логических полюсов (где М - число разрядов выходных регистров блока 4). Устройство работает следующим образом. Перед началом работы устройства на вход 9 блока 2 поступает тест-программа контроля одной из логических схем в двоичном коде. После того, как в блок 2 поступит сигнал с блока 1, разрешающий начало считывания тестовых наборов программы контроля, последовательность служебных установочных сигналов поступает в блок 3 памяти, а последовательность информационных входных и последовательность эталонных выходных сигналов занесется в соответствующие регистры блока 4 памяти. Затем с блока 1 подается импульс опроса в блок 3, с приходом которого происходит параллельный ввод последовательности установочных служебных сигналов в коммутатор б, при этом под воздействием этих сигналов в коммутаторе происходят соответствующие переключения контактов, обеспечивающих подключение к олределенным каналам коммутатора входных и выходных контактов проверяемой логической схемы 8, а также групп входов и выходов блока 5. В следующем временном такте с блока 1 подается импульс опроса в блок 4, разрешающий параллельный ввод информационных входных сигналов через блок 5 в блок 7 и по каналам коммутатора 6 на входные контактные проверяемой логической схемы 8. Блок 5 определяет реакцию контролируемых входов и в случае, если хотя бы один из входов проверяемой логической схемы замкнут на землю, формирует сигнал неисправности данного входа, поступающий в блок 7 для фиксации номера неисправного входа, и сигнал в блок 1 для останова тест-программы. Одновременно с информационными сигналами в блок 5 по другим входам вводятся параллельно из блока 4 эталонные выходные сигналы, которые сравниваются с сигналами выходов проверяемой логической схемы 8. В случае несравнения сигналов хотя бы на одном контролируемом выходе результаты несравнения передаются на блок 7 для фиксации номера неисправного выхода. Блок I на каждом временном такте работы устройства формирует импульс опроса результатов сравнения выходных сигналов с контактов проверяемой схемы с входными эталонными сигналами программы контроля и в случае несравнения в блок 1 поступает сигнал на останов тест-программы контрол я. После проверки логической схемы 8 на одном тесте подается следующий тест, и процесс повторяется до тех пор, пока логическая схема 8 не будет проверена на всех тестах, после чего на блок 2 поступает сигнал останова по входу 9. Сигналы, действующие на выходах блока 3 памяти, поступая в коммутатор 6, переключают контакты коммутатора, соединяя выходы заданных элементов НЕ 16 со входами логической схемы 8. Информационные сигналы, поступая из блока 4 памяти на элемент НЕ 15, изменяют на выходе элемента НЕ 15 уровень потенциалов сигналов с «1 на «О или наоборот. Сигналы с выхода элемента НЕ 15 поступают на вход 20 блока 7 и одновременно эти сигналы поступают на первый вход схемы 18 сравнения и на вход элемента НЕ 16. На выходе элемента НЕ 16 сигналы изменяют уровень потенциала с «О на «1 или наоборот и через контакт, например контакт 22 коммутатора 6, поступают на соответствующий вход проверяемой логической схемы 8 и вход элемента НЕ 17. Если проверяемый вход логической схемы 8 замкнут на землю, то на вход элемента НЕ 17 поступает уровень потенциала сигнала, равный нулю, а с выхода элемента НЕ 17 сигнал поступает на вход 21 блока 7 индикации. В блоке 7 будет зафиксирован номер неисправного входного контакта из-за несравнения логических значений потенциалов сигналов, поступающих по входам 21 и 20. Сигналы с выхода элемента НЕ 17 поступают и на второй вход схемы 18 сравнения, где происходит сравнение сигналов, поступивших с выхода элемента НЕ 15 и с выхода элемента НЕ 17 на совпадение уровней областей потенциалов «1 или «О. Результат сравнения поступает на первый вход соответствующего элемента И 19, на второй вход которого поступает импульс опроса с выхода блока I в каждом такте теста. При обнаружении несовпадения в схеме 18 сравнения с выхода элемента И 19 на вход блока 1 поступает сигнал для останова тест-программы. Таким образом, обнаруживаются все входы логической схемы 8, замкнутые на землю. Для проверки реакций логической схемы 8 на эталонные сигналы соответствующие контакты коммутатора 6 размыкаются (например, как контакт 23), и эталонные выходные сигналы поступают с выходов блока 4 памяти на вход элемента НЕ 15, вызывая переключение уровней потенциалов сигналов с «1 на «О и наоборот на выходе элемента НЕ 15. Затем сигналы с выхода элемента НЕ 15 поступают на вход 20 в блок индикации, где происходит фиксация этих сигналов. Одновременно сигналы с выхода элемента НЕ 15 поступают на первый вход схемы 18 сравнения и вход элемента НЕ 16, выход которого отключен от соответствующего входа проверяемой логической схемы 8 контактом 23 коммутатора 6. Выходные сигналы логической схемы 8 поступают на вход элемента НЕ 17. Сигналы с выхода элемента НЕ 17 поступают по входу 21 в блок 7 индикации, где происходит сравнение и фиксация логических значений сигналов, поступающих по входам 21 и 20. В случае несравнения логических значений выходных и эталонных сигналов в блоке 7 фиксируется номер выходного контакта с неисправностью проверяемой схемы. Сигналы с выхода элемента НЕ 17 поступают и на второй вход схемы 18 сравнения, где происходит сравнение на совпадение этих сигналов с эталонными сигналами, поступающими с выхода элемента НЕ 15. При обнаружении несравнения сигиал с выхода элемента 4 по импульсу опроса из блока 1 поступает для останова тест-программы в формирователь 14. Блок 1 управления работает следующим образом. При подаче питания происходит запуск генератора 11, причем первые тактовые импульсы поступают на вход распределителя 10 и формирователя 12 и запускают их. При подаче сигнала на вход 24 формирователь 12 формирует сигиал «Начало работы, поступающий в блок 2, который разрешает считывать тестовые наборы программы контроля. При этом последовательность служебных установочных сигналов поступает в блок 3 памяти, а последовательность информационных входных и последовательность эталонных выходных сигналов заносятся в соответствующие регистры блока 4 памяти. С поступлением второго тактового импульса с генератора 11 формирователь 12 снимает блокировку распределителя 10 и импульс опроса поступает в блок 3. С приходом этого импульса происходит параллельный ввод последовательности установочных служебных сигналов в коммутатор 6. С приходом третьего тактового импульса на формирователь 12 снимается блокировка другого выхода распределителя 10 и импульс опроса поступает в блок 4, где разрешает параллельный ввод информационных входных сигналов на входы проверяемой логической схемы 8, и в блок 7 индикации, а эталонных выходных сигналов - в блок 5. С поступлением следующего тактового импульса импульсы опроса на каждом из последующих временных тактов работы поступают в блок 5 для опроса результатов сравнения. В случае несравнения на формирователь 13 поступает сигнал, по которому формируется импульс для блока 2 на прерывание тест-программы. Для продолжения проверки логической схемы 8 нужно повторно подать сигнал на вход 24. После проверки схемы на всех тестах программы контроля сигнал «Конец программы контроля выдается с выхода блока 2 на вход блока 4 для обнуления регистров памяти блока 4 и на вход формирователя 14, который формирует и выдает сигнал «Конец работы на вход узла 13. Последний вырабатывает импульс останова тест-программы и приводит в исходное состояние блок 2. Таким образом, предлагаемое устройство обеспечивает сокращение времени проверки логических схем за счет прекращения проверки при обиаружеиии замкнутых на землю входов. Кроме того, устройство имеет меньший съем оборудования и обеспечивает контроль своих собственных блоков. Формула изобретения 1. Устройство для проверки функционирования логических схем, содержащее блок индикации и коммутатор, первые группы входов и выходов которого соответственно являются группами входов и выходов устройства, а вход соединен с выходом первого блока памяти, управляющим входом соединенного с первым выходом блока управления а информационным входом - с первым выходом блока ввода программ контроля, вход которого является входом устройства, а группа входов подключена к группе вы

Авторы

Даты

1982-08-30—Публикация

1980-04-08—Подача