Изобретение относится ,к аналоговой вычисли1 ельной технике.

Известен обобщенный интегратор, содержащий последовательно включенные блок перемножения и интегратор. На входил блока перемножения поданы переменная-и производная.по времени от зависимой машинной переменной ij

Недоста;тками его являются большая погрешность, обусловленная применением блока перемножения и интегрирование по времени. i

Наиболее близким по технической сущности к предлагаемому является интегратор, содержащий интегрирующий усилитель и блок перемножения 2j .

Недостаток данного интегратора заключается в большой погрешности интегрирования, обусловленной погрешностью блока перемножения и в сложности наличия блока перемножения.

Цель изобретения - упрощение интегратора и повышение точности интегрирования.

Это достигается тем, что в интегратор,, содержащий интегрирующий усилитель, выход которого является выходом интегратора, и переключатели

введены дополнительный интегрирующий усилитель, блок сравнения, вход которого подключены соответственно к выходу дополнительного интегриру.ющего усилителя и входу независимог аргумента, а выходы соединены соответственно с входом управления режимом работы основного интегрирующего усилителя и управляющими входами переключателей, переключающие контакты которых подключены соответственно к входам интегрирующих усилителей, а переключаемые контакты переключателей соединены с разнополярными шинами соответственно зависимой переме1й10й и постоянного напряжения.

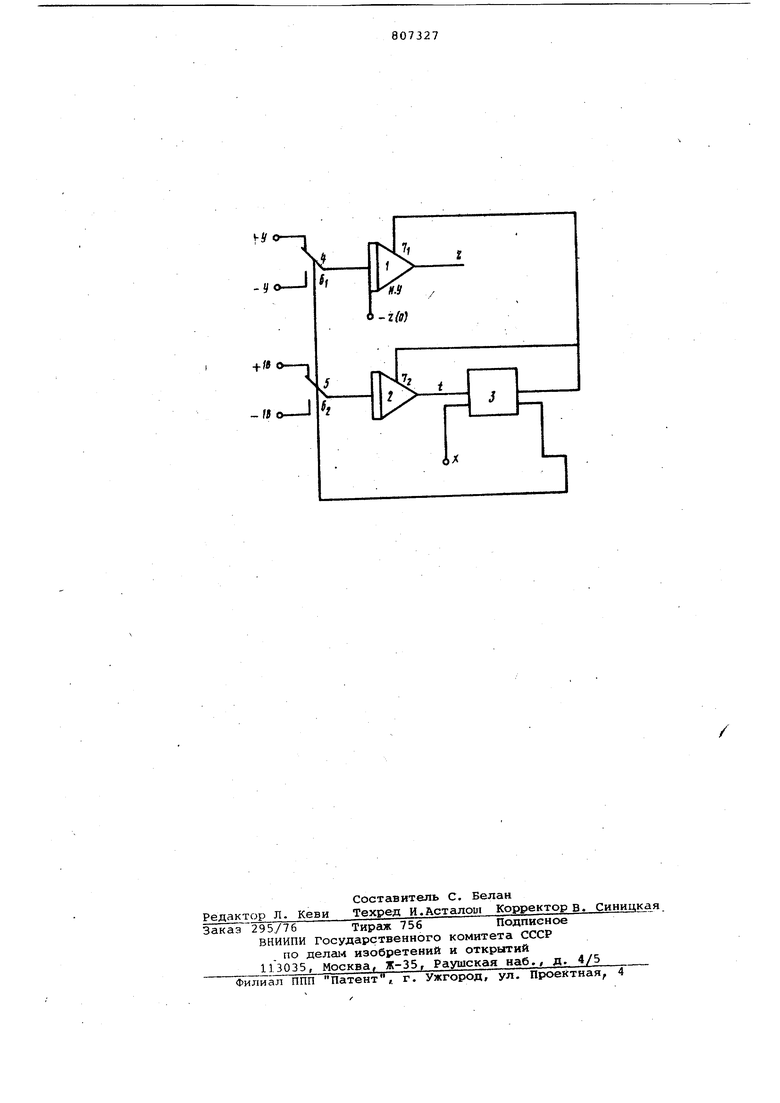

На чертеже приведена блок-схема

интегратора.

. Интегратор содержит интегрирующие усилители 1 и 2, блок 3 сравнения, переключатели 4 и 5, управляющие входы 6 переключателей, входы 7 управления режимом работы интеграторов.

При подаче на вход интегрируквдего усилителя 2 опорного напряжения на его выходе имеет место напряжение. пропорциональное функции t, где t - время в секундах. Если обеспечить равенство значений напряжения на вьпсоде интегрирующего усилителя 2 Напряжению незави симой переменной X, то режим работы этого интегрирующего усилителя буде эквивалентен интегрировани1р по неза висимому аргументу х. Если режим интегрирования первого интегрирующе го усилителя 1 установить таким же как режим второго интегрирующего ус лителя, то режим работы первого интегрирующего усилителя .также будет эквивалентен интегрированию по независимому аргументу х. Для этого применен блок управлен интегратором, который состоит из ин тегрирующего усилителя 2, на вход которого подается постоянное (опорное) напряжение +1 в через переключатель 5 и блок 3 сравнения/ на пер вом выходе которого формируется сиг нал управления переключателями 4 и 5 и подается на управляющие входы 6 переключателей, а на втором выходе формируется сигнал, управляющий режимом работы интеграторов 1 и 2. При положительном знаке разности входного напряжения х и напряжения на выходе интегрирующего усилителя 2 на входы интегрирующих усилителей подаются положительные значения зависимой переменной и опорного напря жения, а при отрицательном знаке указанной выше разности происходит переключение переключателей Л и 5 и на вход интегрирующих усилителей подаются соответственно отрицательные значения зависимой переменной и опорного напряжения, таким образо интегрирование происходит по независимой переменной X. Если разность входного напряжения X и напражения на в :Есоде интегрирующего усилителя 2 не равна нулю, то на втором выходе блока 3 сра нения формируется сигнал пуск инт грирукяцих усилителей 1 и 2, В случае равенства нулю этой.разности на втором выходе блока 3 сравнения формируется сигнал останов интегрирующих усилителей 1 и 2, Таким образом, интегрирующий уси литель 2 работает в режиме слежения за независимой переменной х, а на выходе интегрирующего усилителя 1 получаем значение интеграла зависимой переменной у по независимой переменной х и при задании начальных условий напряжение на выходе интегрирующего усилителя имеет величину Z ydx + Zo Параллельно с интегрирующим усилителем 1 можно включить Б режим интегрирования по независимой переменной п других интегрирующих усилителей. Таким образом, возможно моделирование дифференциального уравнения п-го порядка по независимому аргументу. В отличие от известного предлагаемый обобщенный интегратор позволяет интегрировать по произвольной независимой переменной. Формула изобретения Интегратор, содержащий интегрирующий усилитель, выход которого.является выходом-интегратора и переключатели, отлич ающийся тем, что, с целью упрощения интегратора и повышения точности интегрирования по независимому аргументу, в него введены дополнительный интегрирующий усилитель, блок сравнения, входы которого подключены соответственно к выходу дополнительного интегрирующего усилителя и входу независимого аргумента, а выходы соединены соответственно с входом управления режимом работы основного интегрирующего усилителя и управляющими входами переключателей, переключающие контакты .которых подключены соответственно к входам интегрирующих усилителей, переключаемые контакты переключателей соединены с разнополярными шинами соответственно зависимой переменной и постоянного напряжения. Источники информации, принятые во внимание при экспертизе 1.Коган Б.Я. Электронные моделирующие устройства. М., Госиздатфизматлит, 1959. 2.Керн Г. и Керн Т. Электронные аналоговые и аналого-цифровые вычислительные машины. М., Мир, 1967, т. If с. 73 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1979 |

|

SU801004A1 |

| Устройство для интегрирования | 1983 |

|

SU1108470A1 |

| ЭЛЕКТРОННЫЙ ИЗМЕРИТЕЛЬ ЭЛЕКТРОЭНЕРГИИ | 1995 |

|

RU2097773C1 |

| Аналоговый интегратор | 1983 |

|

SU1239730A1 |

| Генератор функций | 1982 |

|

SU1057966A1 |

| Аналого-цифровой интегратор | 1978 |

|

SU805345A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| Измеритель отношения двух напряжений | 1979 |

|

SU813277A1 |

| Интегрирующее устройство | 1979 |

|

SU813454A1 |

| Интегрирующее устройство | 1985 |

|

SU1251125A1 |

Авторы

Даты

1981-02-23—Публикация

1979-03-19—Подача