(54) УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный десятичный счетчик | 1979 |

|

SU824443A1 |

| Интегро-дифференциальный вычис-лиТЕль | 1979 |

|

SU798902A1 |

| Устройство для сравнения двоичныхчиСЕл | 1979 |

|

SU822178A1 |

| Устройство для обслуживания групповых заявок | 1986 |

|

SU1381507A1 |

| Генератор циклов | 1977 |

|

SU693359A1 |

| Десятичный вычитающий счетчик | 1979 |

|

SU809584A1 |

| Цифровой измеритель длительности одиночных импульсов | 1986 |

|

SU1318986A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ СРЕДНЕЙ НАРАБОТКИ НА ПОЛНЫЙ ОТКАЗ СТРУКТУРНО-СЛОЖНОЙ СИСТЕМЫ | 1992 |

|

RU2041493C1 |

| Устройство для последовательного выделения единиц из двоичного кода | 1990 |

|

SU1795458A1 |

| Устройство для сравнения чисел | 1979 |

|

SU809168A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в различных областях техники и про1ЛЛ11ленности для раздельной регистрации входных воздействий любой физической природы, поступающих одновременно по нес кольким параллельным каналам, например для раздельной регистрации количества производимой продукции различных типов и т.п. Известен счетчик импульсов, содержащий N+1 параллельных регистров и коммутатор каналов, где N - количество входных каналов 1. Недостаток этого многоканального счетчика импульсов заключается в росте аппаратурных затрат пропорционально произведению количества вхо ных каналов на количество разрядов регистров, что привалит к существен ным аппаратурным затратам. Наиболее близким к предлагаемому является устройство для счета импульсов, содержащее регистр, блок синхронизации, триггер, элементы задержки, логические элементы И, ИЛ НЕ, причем входные шины каждого канала подключены к первым входам соответственно группы элементов выходы которых подключены к первым входам группы элементов ИЛИ соответственно, блок синхронизации подключен первым каходом к первому входу первого элемента И и вторым выходом - ко вторым входам группы элементов И, триггер подключен нулевым выходом к первому входу второго элемента И и единичным входом - к выходу первого элемента И, второй вход которюго соединен с выходом первого элемента группы элементов ИЛИ 12 , Недостаток известного устройства - относительная сложность его реализации. Цель изобретения - упрощение устройства. Поставленная цель достигается тем, что в устройство для счета импульсов, содержащее регистр, блок синхронизации, выходы которого подключены к первому входу первого элемента И и к первым входам группы элементов И, вторые входы которой являются входами устройства, выходы первой группы элементов И соединены с соответствующим входом группы элементов ИЛИ, выход первого элемента ИЛИ группы элементов

или подключен ко второму входу первого элемента И,, выход которого соединен с единичным входом тригге™ ра, нулевой выход которого подключен к первому входу второго элемента И и элементы ИЛИ, НЕ и задеркки, введена группа элементов задержки, выходы регистра подключены соответственно к первому входу элемента ИЛИ и к нулевому входу триггера, единичный выход которого через первый элемент задержки соединен со вторым входог. элемента ИЛИ; выкод которого подключен ко второму входу второго элемента И, выход которого соединен со входом регистра, выходы всех последующих элементов ИЛИ группы элементов ИЛИ, кроме первого, через соответствующий элемент задержки подключен ко второзд- входу предыдущего элемента ИЛИ группы элементов ИЛИ, выход первого элемента ИЛИ группы элементов ИЛИ соединен с первым входом третьего элемента И, второй вход которого подключен к выходу элемента НЕ, вход которого соединен с выходом синхронизатора, выход третьего элеме5-1Тс1 И подключен ко второму входу последнего элемента ИЛИ гр у п гы э л емен тон ИЛИ

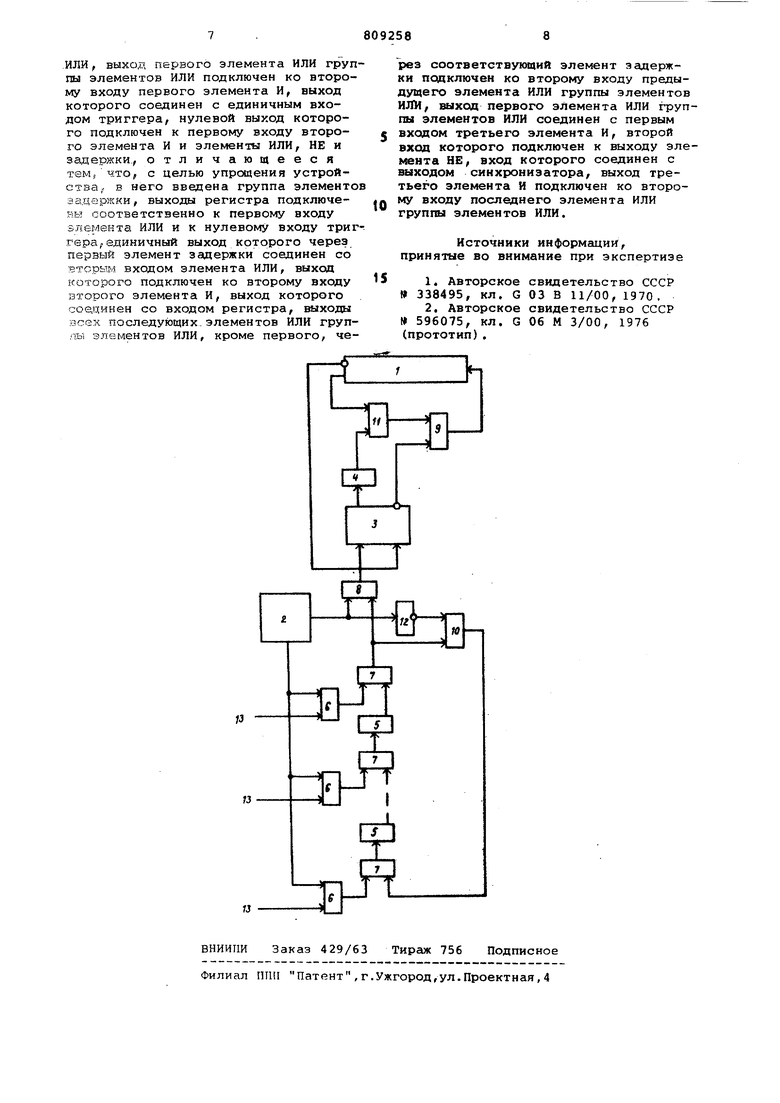

На чертенке приведена структурная схема устройства для счета импульсов ,

Устройство содержит рехистр 1, блок 2 синхронизал:;ии (, триггер 3, элемент 4 за,держки,- группу элементов 5 задержки, группу- элементов И б, группу элементов ИЛИ 7, элементы И 8-10, элемент ИЛИ 11, элемент НЕ 12 и входньзе шнны 13,

Регистр 1 подключен инверсным выходом к нулевом у входу триггера 3, единичный выход которого подключен к входу элемента 4 задержки. Блок 2 синхронизации подключен первым выходом к первому входу первого элемента И 8 , второй вход которого соединен с выходом первого элемента групп элементов ИЛИ 7 и первым входом третьего элемента И 10. Триггер 3 подключен единичным входом первого элемента И 8 и нулевым выходом к первому входу второго элемента И 9,. выход которого соединен с входом регистра 1 . Прямой выход регистра подключен к первому входу элемента ИЛИ 11, выход которого соединен со вторым входом второго элемента И 9, Выход элемента 4 задержки подключен ко второ ду входу элемента ИЛИ 11, Выход соответствующего элемента группы элементов И 6 подключен к первому входу соответствующего элемента группы элементов ИЛИ 7. Выход соответствующего элег тента группы элементов ИЛИ 7 канала соединен через элемент 5 задержки со вторым входом элемента группы ИЛИ 7 .последующего канала. Третий элемент

и 10 подключен ко второму входу последнего элемента группы элементов ИЛИ 7 и вторым входом - к выходу элемента НЕ 12, выход которого соединен с первым выходом блока 2 синхронизации. Выходные шины 13 каждого канала подключены к первым входам группы элементов И б соответственно, вторые входы которых соединены со вторым выходом блока 2 синхронизации

Устройство работает следующим о5 разом,

I В исходном состоянии регистр 1 очищен, а триггер 3 находится в нулевом, состоянии, в которое его устанавливает единичный сигнал инверсного выхода регистра 1.

Блок 2 синхронизации вырабатывает по первому выходу синхронизации импульсы с частотой

.(1)

где f - частота тактовых сигналов,

К - определяется ма симальным числом 2 регистрируемых импульсов по одному каналу, а по второму выходу - импульсы опроса с частотой

F,f

;2)

2К

где К - количество входных каналов.

Регистр 1 выполняет функцию задержки импульсных сигналов на время

- Е-К- f

ц- F fЧ

и имеет возможность хранить динамическим способом К двоичных кодов по п разрядов в каждом.

В исходном состоянии второй элемент И 9 открыт по первому входу единичным сигналом нулевого выхода триггера 3, а на втором входе элемента ИЛИ 11 через элемент 4 задержки действует нулевой сигнал единичного выхода триггера 3. Таким образом, цепь циркуляции последовательных двоичных кодов с прямого выхода регистра 1 на его.-,вход замкнута. Исходное состояние устройства сохраняется до поступления по входным шинам 13 последовательностей импульсов

Предположим, что в момент действия импульса опроса, поступаклцего со второго выхода блока 2 синхронизации на вторые входы всех элементов И 6, на все входные шины 13 поступают счетные импульсы. В этом случае срабатывают все элементы И б, с выхода KOTOptJx импульсные сигналы поступают на первые входы элементов ИЛИ.7. Счетный импульс первого канала с выхода первого элемента ИЛИ 7 поступает на второй вход первого элемента И 8 и первый вход третьего элемента И 10. В это время на первом выходе блока 2 синхронизации действует синхронизирующий импульс, который поступает на первый вход первого элемента И 8, открывая его, и через элемент НЕ 12 закрывает по второму входу третий элемент И 10. Таким образом, счетный импульс первого канала проходит на выход первого элемента И 8, устанавливая триггер 3 в единичное состояние, а на выход третьего элемента И 10 не поступает. Установка триггера 3 в единичное состояние приводит к запиранию второго элемента И 9 по первому входу и к действию единичного сигнала единичного выхода три гера 3 на втором входе элемента ИЛИ 11, спустя время задержки элементом 4, которое равно длительности импульса. Триггер 3 возвращает в нулевое состояние единичный сигнал инверсного выхода регистра 1 в момент считывания нулевого кода младшего разряда двоичного кода первого кана ла. Возврат триггера 3 в единичное состояние приводит к формированию на выходе второго элемента И 9 импу сного сигнала, так как по первому входу он открывается единичным сигналом нулевого выхода триггера 3, а на втором входе второго элемента 9 на время длительности импульса эл ментом задержки 4 через элемент ИЛИ 11 поддерживается единичный сигнал предыдущего единичного состояния тр гера. Импульсный сигнал с выхода второго элемента И 9 записывается в регистр 1 по месту первого разряда двоичного кода первого канала, остальные (нулевые) разряды которого переписываются без изменения с прямого выхода регистра 1 на его вход через элементы ИЛИ 11 и И 9. В это время счетные импульсы вто рого и всех последующих каналов цир кулируют в регистре, образованном последовательным соединением элемен тов задержки 5 на один период такто вой частоты и элементов ИЛИ 7; Цепь циркуляции этого регистра закыкается через третий элемент И 10, который открыт по второму входу элемент НЕ,. 12 ввиду отсутствия синхронизиру щих импульсов на первом выходе блока 2 синхронизации. Параметры многоканального счетчи ка импульсов выбираются такими,чтобы выполнялось соотношение ,(4) где п - количество разрядов двоично го кода одного канала, К - количество входных каналов. Соотношение (4) обеспечивает задержку импульсного сигнала в цепи циркуляции регистра, образованного последовательным соединением элемен тов задержки 5, элементов ИЛИ 7 и третьего элемента И 10, на время Та -9Соотношение (5) обеспечивает сов,падение на входах первого элемента И 8 счетного импульса второго канала с синхрониэирукадим импульсом, действующим на первом выходе блока 2 синхронизации с частотой f/n,K моменту считывания с выхода регистра 1 младшего разряда п-разрядного двоичного кода второго канала. Таким образом, триггер 3 установится в единичное состояние счетным сигналом второго канала к моменту считывания с выхода регистра 1 младшего разряда двоичного кода второго канала. Счетный сигнал второго канала стирается. В результате запирания третьего элемента И 10 по второму входу синхронизирующим сигналом первого выхода блока 2 синхронизации, действующим через элемент НЕ 12. Суммирование счетного импульса второго канала с двоичным кодом второго канала регистра 1 выполняется таким же образом, как суммирование счетного импульса первого канала, благодаря формированию на выходе второго элемента И 9 импульсного сигнала по месту первого, начиная с младшего разряда, нулевого кода,который в виде импульсного сигнала на инверсном выходе регистра 1 возвращает триггер 3 в нулевое состояние. Причем, при единичном состоянии триггера второй элемент И 9 закрыт, что обеспечивает стирание всех единиц до первого нулевого кода. CyNiMHpOBaHHe счетных импульсов остальных каналов с соответствующиьш двоичными кодами регистра 1 выполняется аналогичным образом. К моменту времени действия следующего импульса опроса на втором выходе блока 2 синхронизации все К двоичных кодов в регистре 1 увеличивается на единицу, а регистр, образованный последовательным соединением элементов 5 задержки, элементов ИЛИ 7 и третьего элемента И 10, бует очищен от счетных импульсов пре-. дъадущего опроса входных шин 13. В дальнейшем устройство работает аналогичным образом. Технико-экономические преимущества предлагаемого многоканального счетчика импульсов заключается з простоте реализации. Формула изобретения Устройство для счета импульсов, одержащее регистр, блок синхрониации, выходы которого подключены первому входу первого элемента И к первым входам группы элементов , вторые входы которой- являются ходами устройства, выходы первой руппы элементов И соединены с соотетствующим входом группы элементов

Авторы

Даты

1981-02-28—Публикация

1979-05-14—Подача