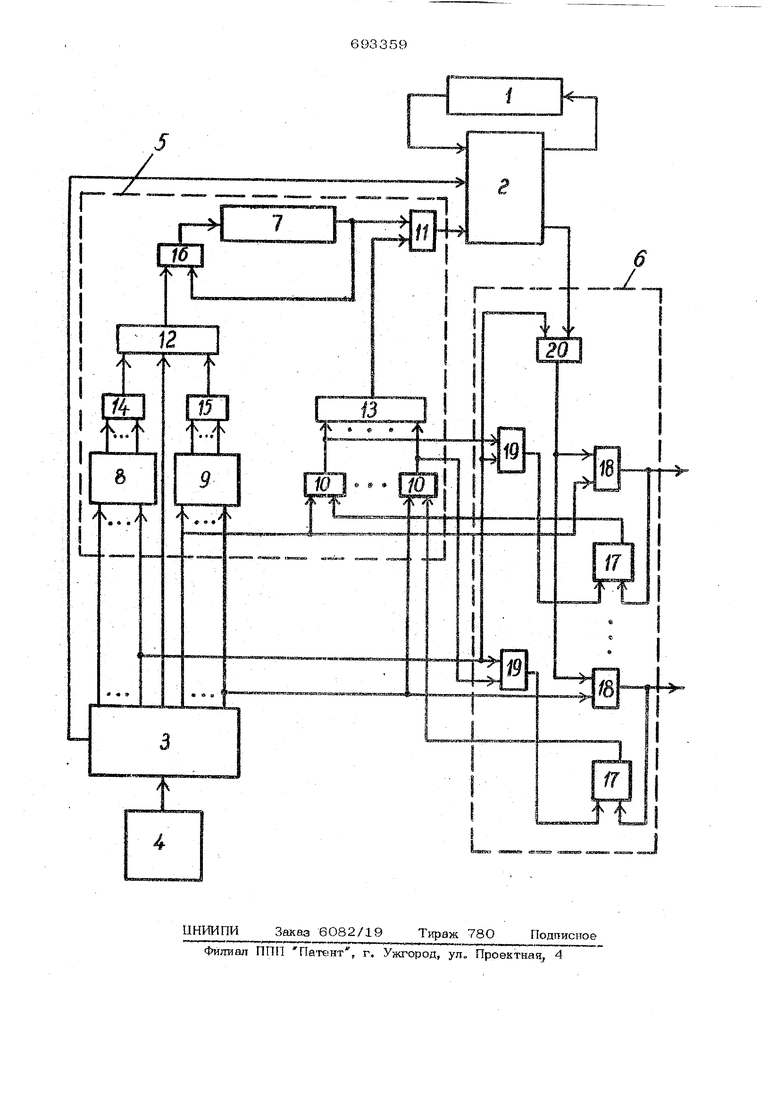

Изобретение относится к области автоматики и вычислительной техники и предназна енр для генерирования импульсных сигналов с заданным периодом следования. Известен генератор циклов, содержащий динамический регистр на магнитострикщюнной линии задержки, соединенный с сумматором последовательного дейс-пвия, кварцевый генератор, соединенный с блоком синхронизации, блок ввода начальных условий и триггер, подключенные чэ« рез схему И и сумматор к динамическому регистру . Недостатком этого генератора циклов является ограниченность функциональных возможностей, которая заражается в 1;-ене рировании выходных сигналов с различной 1астотой следования только по одному каналу. Наиболее близким техническим решением к данному предложению является генератор циклов, содержащий кольцевой регистр сдвига, сумматор, блок синхронизации, генератор эталонной частоты, первый И второй коммутаторы, первый элемент И, первую и вторую группы элементов И по Ш элементов в каждой группе (fn-число выходов генератора циклов), первый, второй и третий элементы ИЛИ, w триггеров, причем выход кольцевого регистра сдвига подклк)чен к первому входу сумматора, а вход - к выходу суммы суммй1о ра, йлход переноса которохч подключен к первому входу злемевта И, первый выход; блока свпхронизацни подклю- чен к скнхрониэирукя му входу суммато. ра, первая группа оыходов блока синхронизации через первый коммутатор подклкнчена Ко входам второго элемента ИЛИ, а вторая группа выходов блока синхронизации через второй коммутатор - ко входам третьего элемента ИЛИ, первые входы элементов И первой группы подключены к выходам соответствующих триггеров, а вторые входа - к соответствующим выходам второй Л руппы блока синхронвза- цви в первым входем соответствуюпшх элементов И второй группы, выходы але- и первой группы подключены ко входам первого элемента ИЛИ, выходы nepaotX) элемента И подключены ко вто |рым входам эпемевтрв И второй rpymuJ, выхо; кргорых, являюпщеся выходами reHepaTopia аЕкло1з, пойшочевы к эданичвым входам соответствующих триггеров, выход генератора эталонной частоты подключен ко входу блока синхронизации 2. Недостатком его является сложность Цель изобретения - упрощение устройстеа. Цель дос-зпагаетса тем, что генератор сзрдержит дополнительный кольцевой регистр сдвига, второй и треЧий элементы И, третью группу из in элементов РГ и четвертый элемент ИЛИ, причем выход до яюлнитёльного колыцевого регистра сдвига подключен к першам входам второго элемента И и четвертого элемента ИЛИ, а вход - к выходу четвертого элемента ИЛИ выход первого элемента ИЛИ подключен ко второму входу второго элемента И, выход которого подключен ко второму входу сумматора, первый, выторой к третий вхо fSfj третьего элемента И подключены COOT ветствёнНо к выходу второго и третьезго элементов ИЛИ и второму выходу блока синхронизации, а выход третьего элемента И - ко второму входу четвертого элемента ИЛИ, первые входы элементов И третьей группы подключены к выходам со ответствующих элементов И первой группы, выходы - к нулевым -входим соответ ствующих триггеров, а вторые входм, также второй вход первого элементй И к одному из шлходов перврй группы блока синхронизации На чертеже изображена структурная схйла генератора циклов. Генератор ииклов содержит кольцевой регистр сдвига 1, сумматор 2, блок синхрониздции 3, генератор эТалонной частоты 4, блок ввода начальных условий 5 и многоканвльк го вывода 6. Блок ввода начальных условий 5 состоит ив яйпблнитёп1Ж гб колыхевбго регистра сдвига 7, двух коммутаторов В и 9, двухююдовых элементов И 10 первой группы, элементов И 11 и 12, элементов ИЛИ 13, 14, 15 и 16. Влок многоканального вывода 6 состоит из Ли триггеров 17, m двухвходовых эвемевтов И 18 второй группы, hi двухвхояЬшх элементов И 19 третьей группы fWieMc Ta И 20. FisHepatop циклов работает следующим . Гвнератор эталонной частоты 4 вырабатзывает импульсные сигналы с частотой , которые поступают в блок синхронизаии 3. Блок синхронизации 3 с помощью елителя частоты вырабатывает по первоу выходу счетные импульсы с частотой -J.: где И - количество разрядов в одном слове динамического регистра 1, необходимое для генерирования сигналов по одному выходу. Максимальная частота импульсных сиг- налов на каждом из Hi выходов генератора циклов определяется временем задержки Г ямпульсного сигнала в динамическом регистре I ., 2 1ПпТ . где уп- количество слов регистра, равное количеству выходов генератора цик- . лов. Время задержки импульсного сигнала в регистре 7 также равно Т .Величина И-Ж равна полному количеству двоичных разрядов регистров 1 и 7, каждый из которых хранит rVVi двоичных кодов (слов) по п разрядов. Соединение регистра 1 с суммато юм 2 образует счетчик импульсов, поступающих с частотой f с первого выхода блока синхронизации 3 на один из входов сумматора 2. Сумматор 2 выполняет за один , цикл -Г суммирование одного импульса с первого Ейыхода блока синхронизации 3 последовательно с первым (младшим) разрядом во всех ГУ словах динамического регистра 1. Сигналы на обходах генератора циклов появляются в момент появления импульса переноса на втором выходе сумматора 2. в каждом h-OM разряде кажiJtOiro слова динамического регистра 1. В случае нулевых начальных условий. вырабатываемых блоком 5, выходной сигнал на каждом из Yn выходов генератора циклов поя1вляется с частотой Дискретность заполнения каждого Мго разряда динамического регистра 1 ооставл«(ет 2, где N - номер разряда в одном слове регистра 1. Такая дискрет ность при больших периодах следования выходных сигналов генератора циклов не всегда соответг.-туе т требуемому периоду. С .целью точной отработки заданного периода следования в регистр 1 во все Ж слова вводятся начальные условия с помо- шью блока 5. jQвoичpыe Kojflj «ачеа ъвык условий формируются блоком 5 из импульсных сигналов, вырабатываемых блоком синхронизации 3 по и выходам первой группы в Щ ш.1Ходам второй группы, По п выходам первой группы блок син хронизации 3 вырабатывает из импульсов генератора эталонной часто.ты 4 И времен- ныхпЬспедовательностейимпульсов {разр Я- дов), сдвинутых друг относителыю друга на один период эталонной частоты и следуюших с частотой f. По И выходам второй группы блок син .хронизапии 3 вырабатывает из импульсов частоты f-i п временных последовательноотей импульсов (слов), сдвинутых друг OTW носительнр друга на один период часто-сл f и следующих с частотой f. Длитель ность этих импульсов равна первюду часТОТЫ f 2-По второму выходу блок СКВхронизадии 3 вырабатывает сигнал Запись длительностью На первом коммутаторе 8 выставляете ся и -разрядный двоичный код начальных условий, который с помощью ц .ходового элемента ИЛИ 14 преобразуется из параллельного кода в последовательный По втором коммутаторе 9 задается порядковый номер слова от 1 до vn - Замыкание контактной группы коммутатора 9 обеспечивает подключение сорч втству- ющето выхода второй группь ылходов блока синхронизации 3 через элемент ИЛИ 15 ко входу элемента И 1.2. По сигналу Запись, вырабатываемому на втором выходе блока сввхроввзацин 3, срабатывает элемент И 12, череа который во время действия синхроназируюшего сигнала на соответствующем выходе второй группы блока 3 пройдет последовательно, начиная с первого (младшего) разряда, двоичный код начальных условий, заданный на коммутаторе 8. Этот двоичный код с выхода элемента И 12 че рез элемент ИЛИ 16 запишется в регистр 7 по месту, выбранному номером слова на коммутаторе 9. В дальнейшем двоич ный код начальных условий хранится в регистре 7, циркулируя с выхода его на вход через элемент И/1И 16. Аналогичным образом записываются в регистр 7 все т слов начальных условий в вИдё h -разрядных двоичных кодов. 693 96 В режиме запвси вачальвых условий в регистр 7 все триггеры 17 блока 6 на Х0ДЯТСЯ в нулевом состояний, в результате чего все элемеачы И 1О закрыты снгналом с единичных выходов триггеров 17, в элемент ИЛИ 13 вырабатывает нулевой сигнал, закрывающий элемент И 11. Блок сиюсронизадЕИ 3 в этом режиме счетные импульсы по первому выходу не вырабатывает. Динамическвй регистр 1 очишен и не меняет своего содержимого, так как на входа сумматора 2, сигналы не посту- пают. Запуск генератора циклов осушествляется установкой всех триггеров 17 блока 6 в единичное состояние. ЕдиничнЕаге выхода триггеров 17 открывают все элементы И Ю блока 5, в результате чего втоpgg группа выходов блока синхронизации з подключается Е о входам элемента ИЛИ з. Одновременно с запуском генератора циклов блок синхронизации 3 начинает вырабагывать по первому выхбду счетные тлпулызл с частотой Совпадающие с - f . моментом считывания с выходов динамических, регистров 1 и 7 младших разрядов слов. Синхронизирующий сигнал- слова с первого выхода второй группы выходов блока 3 гу1нтельйостью h /f через элемент И 1О, открытый единичным выходом триггера 17, поступает на вход элемента ИЛИ 13. С далхода элемента ИЛИ 13 синхронизирующий сигнал первого слова поступйют на второй вход элемента И 11, обес11вч|шая прохождение последовательного даювчного кода начальных условий первого слова на вход сумматора 2. Сумматор 2 суммирует код начальных условий первого слова со счетным сигна- лом, поступающим с первого выхода блокв синхрон8эа 1ии 3, и результат записы- вается с первотго выхода сумматора 2 в дивамвческкй регистр 1. Посла окончания передачи последнего разряда первого слова из регистра Д сумматора 2 на последнем выходе первой группы выходов блока синхронизадив 3 вырабатывается синхронизирующий сигнал и НТО разряда, который по ступает на второй вход элемента И 19 перового канала. На первом входе элемента И 19 первого канала в это время действует синхроввзируЮ11Шй сигнал первого слова с ш гхода первого элемента И 1О. Элемент И 19 первого канала срабаты69вает и пропускает синхронизирующий вмпульс разряда на вход установки / в нулевое состояние триггера 17 первого канала. В это время элемент И 20 закрыт по первому входу ВВИДУ о-гсутстаия переноса в разряд на втором вы ходе сумматора 2, Трип-ер 17 первого канала сбрасывв ется в вуяевое состояние, закрывая единичным выходом первый элемент И 10 блока 5, .. Аналот ичным образом происходит перезапись начальных условий остальных слов из регистра 7 через элемент И 11, сумматор 2 в регистр 1. После каждой перезаписв 1-го слова сраёатЬтвает элемент И 19 канала блока 6, в результате чего сбрасывается чрйггер 17 этого канала и закрывается i-Фгй элемент И 10 в блоке. 5.. После перезаписи всех начеяьных условий Из динамического регистра 7 в динамический регистр 1 все триггеры 17 блока в перейдут в нулевое состояние. В резулътате все элементы И 10 блока 5 закроютсй едййичнймн выходами тригге-; ров 17 блока 6. На выходе элемента И лИ 13 сформируется нулевой сигнал, который закроет элемент И 11, запрещающий дальнейшее поступление кодов начальвьгх уелоВИЙ с выхода регистра 7 на вход cjnwMaтора 2.: В дальнейшем двйиздвлй счетчик, образованный соединением, сумматора с регйст ром 1, выполняет счёт ампульсов первого выхода блока Синхронизации 3 с начальных условий в каждом слове, которые были задана двоичными кодами динамического регистра 7. Так будет продолжаться до тех пор, по ка не появится перенос в Vl-ом разряде в любом слове. Допустим перенос в Ь-ом разряде произойдёт в первом слове регист ра 1, В этом случае на втором выходе сумматора 2 во время действия синхрони- a ipyKjiEiero сигнала И-го разряда на Последнем выходе первой группы блока 3 вгоявится сигнал переноса, который откро ет элемент И 20 и поступит на nepBbie входы всех элементов И 18, Однако еработает только элемейт И 18 первого канала, так как на второй вход iaro поступит сигнал с первого выхода второй группы выходов блока синхронизаини 3, совпадающий с периодом обработки первого слова в сумматоре 2. Импупьстшгй сигнал с выхода элемента И 18 первого канала пройдет на пёр9вый выход блока 6 и установит в единичное состояние триггер 17, который откроет первый элемент И 10 блока 5. Остальные элементы И 10 Останутся закрытыми единичными выходами триггеров 17 остальных каналов соответственно. Синхронизирующий сигнал первого слова с первого №1хода второй группы выходов блока 3 прьйдет через первый элемент И 10, элемент ИЛИ 13 на второй вход элемента И 11, кото{ый откроется и пропустит начальные условия первого слбва с выхода динамического регистра 7на вход сумматора 2. Таким образом восстанавливаются начальные условия в пёрВок слове Динамического регистра 1 после генерации блоком 6 выходного импульса по первому каналу. После переписи двоичного кода начальнь1х условий первого слова из динамического регистра 7 8динамически регистр 1 цикл генерации вьгходного импудьса по первому каналу повторится. Аналогичным образом генерирутются выходные импульсы генератора циклов в других каналах при переполнении в И-ый разряд соответствующего слова динамического регистра 1. Аналогично процессу восстановления начальных условий в первом слове динамического регистра 1 осуществляется восстановление начальных условий в других словах динамического регистра 1 при генераций выходного импульса в соответст вующем канале блока 6. : Реализация генераторов циклов с параlA TpaMH Hi 10 по предлагаемой схеме энйчйт«льно проще. Введение в генератор йиклов Второго динамического регистра, одаого элемента И на двia входа, одного элемента И на три входа, одного элемента ИЛИ на два входа и двухвходовых элементов И позволило исключить из схемы устройства hi - 2 коммутаторов, т- 2 элементов ИЛИ на п входов и вместо tti элементов И аи три входа использовать столько же даухвходовых элементов И. Формула в а о б р е т е н и я Генератор циклов, содержащий кольцевой регистр сдвига, сумматор, блок синхронизации, генератор эталонной частоты, первый и второй коммутаторы, первый элемент И, первую н вторую группы элементов в каждой группе (Hi-число выходов генератора циклов), первый, второй и третей элементъ ИЛИ, ги триггеров, причем выход колы1евого регистра сдвига подключен к первому входу сумматора, а вход - к выходу суммы сумматора, выход переноса которого подключен к первому входу первого элемента И, перш1й выход блока синхронизации подключен к синхрониэируюшему входу сумматора, первая группа выходов блока синхронизации через первый коммутатор подключена ко входам второго элемента ИЛИ, а вторая группа выходов блока синхронизации через второй коммутатор - ко входам третьего эле мента ИЛИ, первьте входы элементов И первой группы подключены к выходам COOT- ; ветствуюишх триггеров, а вторые входы к соответствующим выходим второй группы блока синхронизации и перизтм входам соответствующих элементов И второй груплы, выходы элементов И первой группы подключены ко входам первого элемента ИЛИ, выход первого элемента И подключен ко вторым входам элементов И второй группы, выходы которыХ)являющиеся выходами генератора циклов, подключены к единичным входам соответству- юптих триггеров, выход генератора эталонной частоты подключен ко входу блока синхронизации, о т л и ч а ю щ и и с я тем, что, с целью упрощения генератора циклов, он содержит дополнительный кольцевой регистр сдвига, второй и третий алементы И, третью группу из hi злементов И и четвертый элемент ИЛИ, причем выход дополнительного кольцевого регистра сдвига подключен к первым входам второго элемента Ив четвертого элемента ИЛИ, а вход - к выходу четвертого элемента ИЛИ, выход первого элемента ИЛИ подключен ко второму входу второхч) элемента И, выход которого подалючен кй второму входу сумматора, первый, второй и третий входы третьего элемента И подключены соответственно к выходу второго и третьего элемейтов ИЛИ и второму выходу блока синхронизации, а выход третьего элемента И - ко второму входу четвертого элемента ИЛИ, первые входы элементов И третьей группы подключены к выходам соответствующих элементов И первой группы, выхода - к йулевым входам соответствующих триггеров, а вторые входьт, а также второй вход первого элемента И - к одному из йыходов первой группы блока сйнхрониэатн.

Источники янформацйв, 11рвня1ые во внимание при экспертизе

1.Авторское свидетельство СССР Ns 291198, кл. G 06 F 7/ОО, 1969.

2.Авторское свидетельство СССР

№ 485437, кл. Q Об F 1/02,23.04.73 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор циклов | 1981 |

|

SU964616A1 |

| Цифровой регулятор | 1982 |

|

SU1056130A2 |

| Интегро-дифференциальный вычис-лиТЕль | 1979 |

|

SU798902A1 |

| Устройство для контроля экспоненциальных процессов | 1987 |

|

SU1500997A1 |

| Интегро-дифференциальный вычислитель | 1983 |

|

SU1108445A2 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Генератор сигналов сложной формы | 1985 |

|

SU1280597A1 |

| Цифровая электронная вычислительная машина последовательного действия | 1975 |

|

SU532295A1 |

| Цифровой регулятор | 1980 |

|

SU938255A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО КОНТРОЛЯ | 1991 |

|

RU2015523C1 |

Авторы

Даты

1979-10-25—Публикация

1977-07-05—Подача