1

Изобретение относится к автоматике и вычислительной технике и может быть использовано для моделирования и управления динамическими объектами в различных отраслях промышленности

Известны аналоговые интегро-дйфференциальные устройства, содержащие аналоговые интеграторы,. сумматоры и масштабные блоки для задания коэффициентов передачи fljНедостатком аналоговых интегродифференциальных устройств является низкая точность вычисления выходных сигналов в случае достаточно больших значений постоянных времени, характерных для многих технологических процессов, -ц

Наиболее бл изким техническим решением к предлагаемому является интегро-дифференциальный вычислитель , содержащий.четыре регистра, сумматор, два блока дополнительного кода, блок синхронизации. Три триггера, элементы И, ИЛИ и элемент- задержки, причем вход первого регистра подключен к выходу сумматора и первому входу блока знака, второй вход которого подключен к первой входной шине, первый вход сумматора под: ключен к выходу первого блока дополнительного кода, второй вход сумматора подключен .к вьоходу первого элемента ИЛИ, входы которого подключены к выходам первого и второго элементов И, подключенных первыми входами.соответственно к прямому и инверсному выходам первого триггера, выход первого регистра подключен ко второму входу первого эле0мента И, блок синхронизации подключен первым выходом к инверсным входам первого, второго и третьего триггеров , вторым выходом - к третьему входу блока знака и третьей груп5пой выходов - к четвертой группе входов 2.

Недостатками известного устройства является относительно высокие аппаратурные затраты и низкое быс0 тродействие;

Относительно высокие аппаратурные затраты на реализацию интегродифференциального вычислителя с помощью цифровых интеграторов выз5ваны ростом количества цифровых интеграторов в зависимости от сложности интегро-дифференциального преобразования.

Низкое быстродействие цифровых

0 дифференцильных анализаторов связано с вычислениями одноразрядных прИ ращений на одном шаге/ что требует значительного количества шагов на интервале интегрирования.

Цель изобретения - упрощение вычислителя и повышения его быстродействия. .

Поставленная цель достигает зя j:em что в интегро-дифференциальном вычйр лителе, содержащем блок синхронизации, регистры/ сумматор, .блоки формирования дополнительного кода, блок хранения знака, триггеры, элементы И ИЛИ, и элемент задержки, причем вход первого регистра подключен к выходу сумматора и первому входу блока хранения знака,- второй вход которого подключен к первому входувьтаислителя, первый вход сумматора соедийен с выходом первого блока формирования дополнительного кода, второй вход сумматора подключен к выходу :, первого элемента ИЛИ, входы которого подключены соответственно к выходам первого и второго элементов И, первые входы которых подключены соответственно к прямому и инверс-. ному выходам первого триггера, выход первого регистра подключен ко второму входу первого элемента.И, первый выход блока синхронизации подключен к инверсным входам первого, второго и третьего триггеров, второй выход - к-третьему входу блока хранения знака, группа выходов к группе входов блока храйения знака, второй вход второго элемент и подключен к первому входу второго блока формирования дополнительного кода непосредственно и через элемент задержки - к выходу первого регистра, первый вход первого блока формирования дополнительного кода подключен к выходу третьего элемента И, первый вход которого подключен к выходу второго регистра, второй вход - к прямому выходу второго триггера, вторые входы первого и.второго блоков формирования дополнительного кода подключены к выходу блока хранения знака и к первому выходу вычислителя, выхода второго блока формирования дополнительного кода подключен к первому входу четвертого элемента И, выход третьего регистра подключен к первому входу пятого, элемента И, входы второго элемента ИЛИ подключены соответственно к выходам четвертого и пятого элементов И, вход Ч;етвертого регистра подключен к выходу второго элемента ИЛИ и к первому входу шестого элемента И, второй вход которого подключен к третьему выходу блока синхронизации, а выход - к прямому входу второго триггера, входы третьего элемента ИЛИ подключены соответственно к выходам седьмого и восьмого элементов и, выход третьего элемента

ИЛИ соединен с.входом третьего регистра, первый вход седьмогЬ элемента И подключен ко второму входу вычислителя, второй вход - к прямому выходу третьего триггера, инверсный выход которого соединен с третьим входом второго элемента И, вторым входом пятого элемента И и первьйми входами восьмого и девятого элементов И элемента и подключен к выходу четвертого регистра,, прямой вход третьего триггера соединен с вторым выходом блока, синхронизации, четвертый выход которого подключен ко второму входу. девятого элемента И, выход которого с.оединен с прямым входом первого триггера, второй выход вычислителя соединен с выходом четвертого элемента И ..

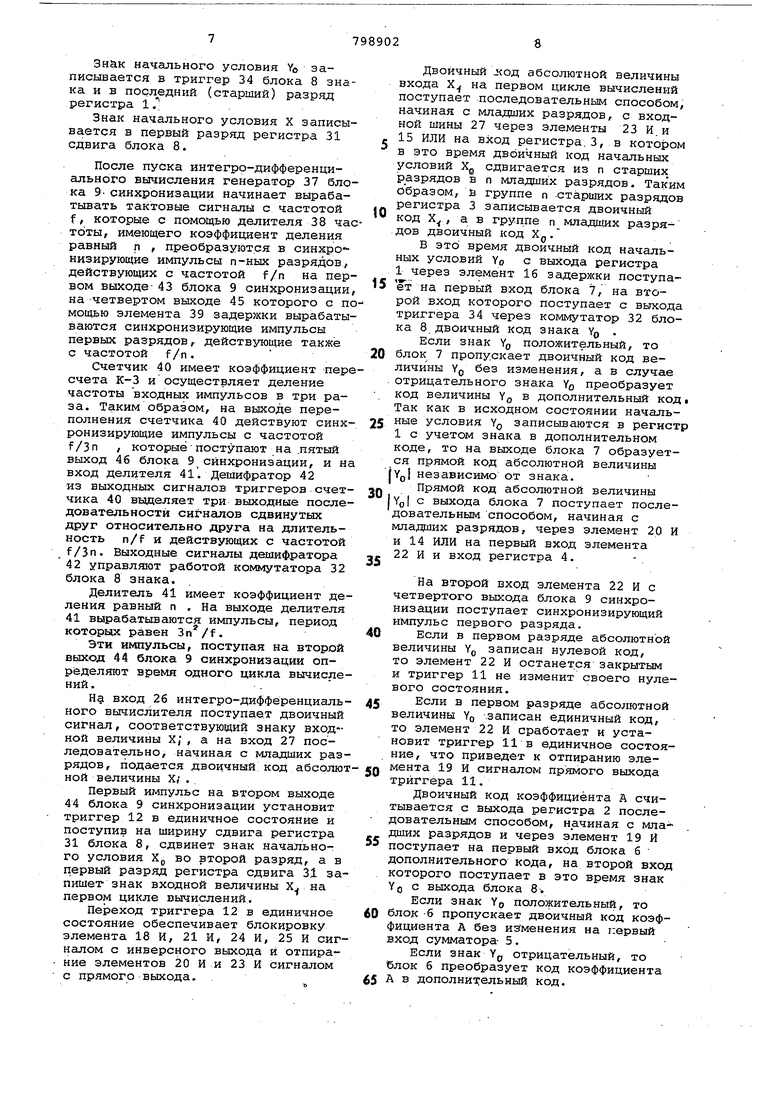

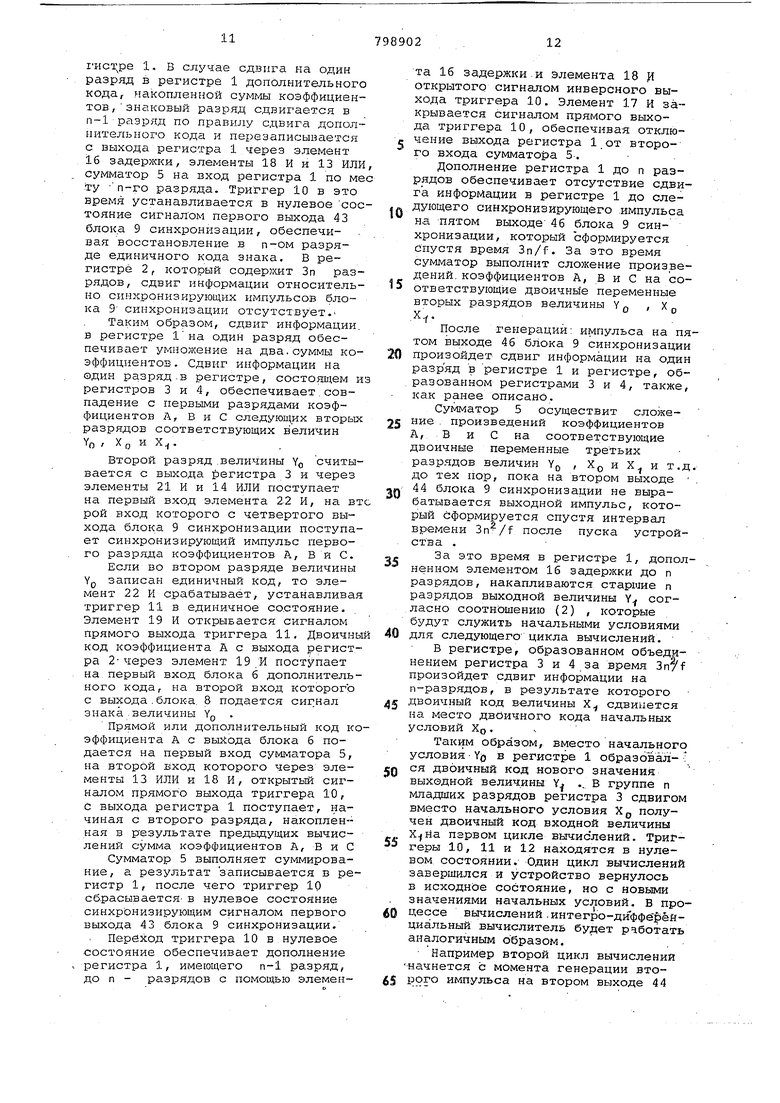

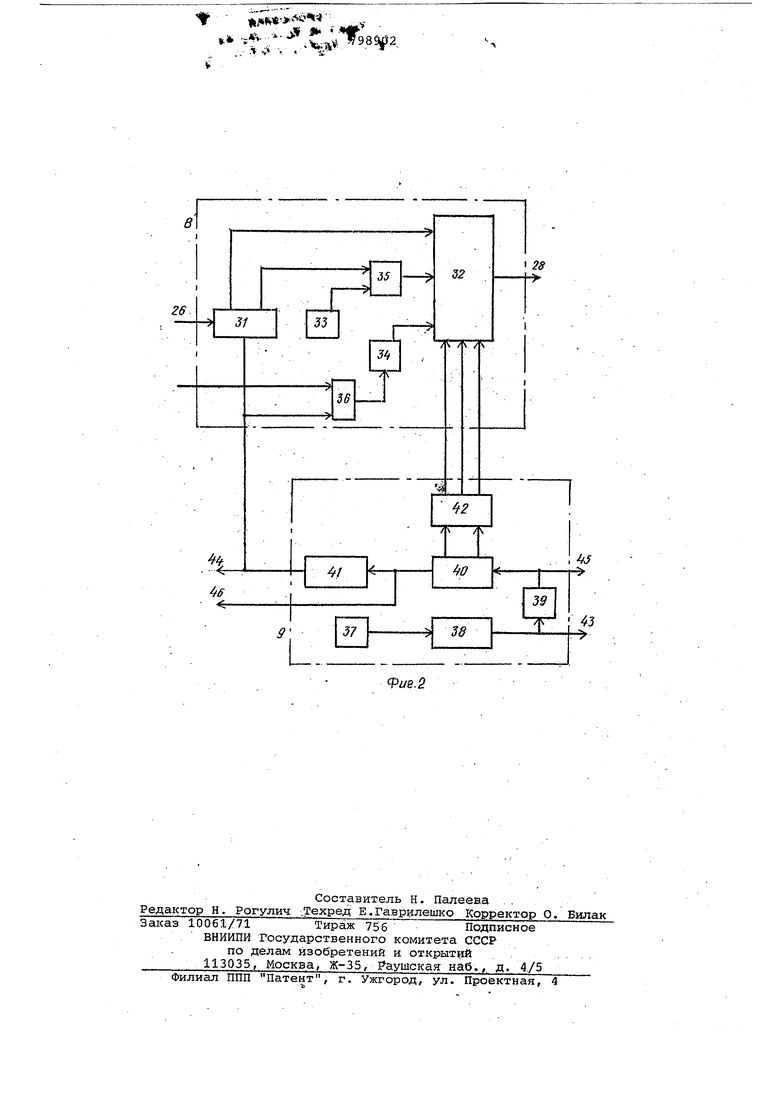

Ца фиг. 1 изображена структурная схема интегро-дифференциального вычислителя ; на фиг. 2 - структурная схема-блока знака и блока синхронизации, .

Интёгро-дифференциалъный вычислитель / фиг. 1) содержит четыре регистра 1-4, сумматор 5, два блока б и 7 формирования дополнительного кода , блок 8 хранения знака, блок 9 синхронизации, три триггера 10-12, три элемента 13-15 ИЛИ, элемент 16 задержки, девять элементов И, два входа 26-27 и два выхода 28-29. .

Интегро-диффёренцильный выч.ислитель для каждог.о цикла отрабатывает рекуррентное соотношение

Yi AYi-i+-BX -i+ CXi,, (1) где Yj, и Y.. - значения выходной

величины соответственно на it-м и (i-l . . . цикле, вычислений

А, В, С - постоянные коэффици.. - енты, значения которых зависят от шага по независимой переменной, согласно которому осуществляется переход от (i-l)-ro к i-му и П следующим циклам вычислений , а так же от вида реализуемог интегрр-дифференци:ального преобразования;

X;; и Xi..j - значения входной ве-. личины соответственно- на i-м и(i-1)-м цикле вычислений.

Для настройки вычислителя осуществляется ввод постоянных коэффици ентов А,.В и С и начальных условий Yii и Xt-d . Далее с постоянным шагом h согласно (1) осуществляется

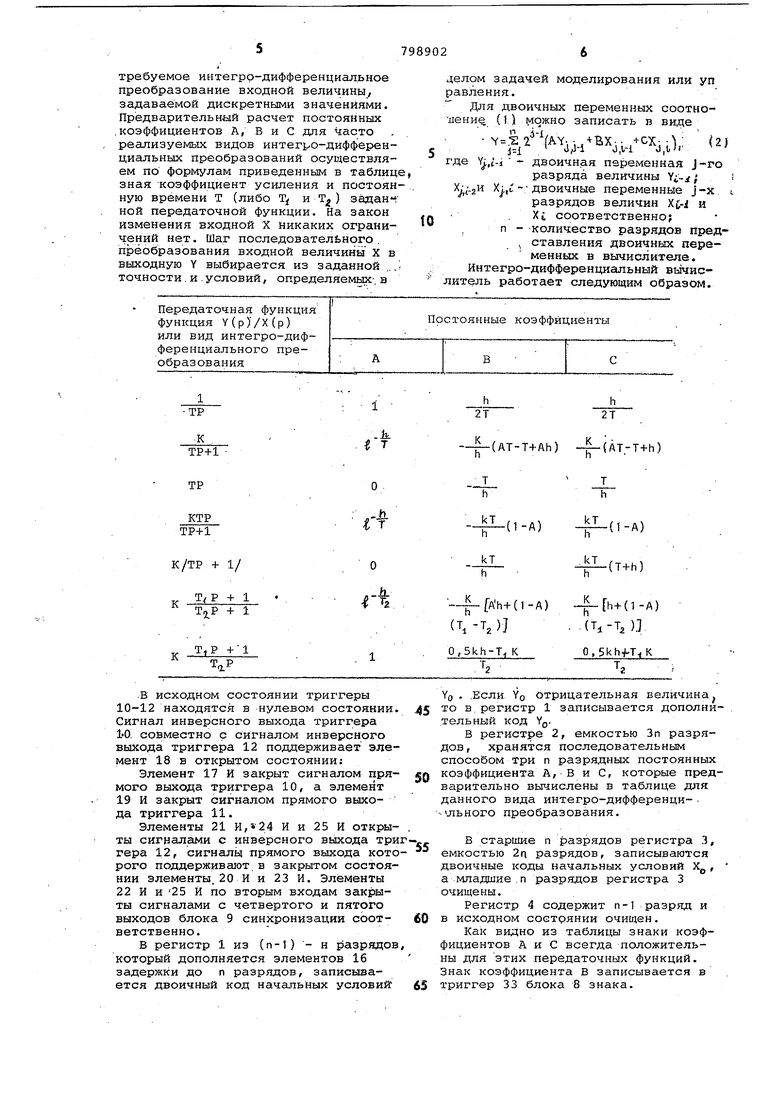

требуемое интегрр-дифференциальное преобразование входной величины, задаваемой дискретными значениями. Предварительный расчет постоянных .коэффициентов А, В и С для часто реализуемых видов интегро-дифференциальных преобразований осуществляем по формулам приведенным в таблице зная коэффициент усиления и постоянную времени Т (либо Т и T,j ) задананой передаточной функции. На закон изменения входной X никаких ограничений нет. Шаг последовательного, преобразования входной величины X в выходную Y выбирается из заданной ,.,, точности. и . условий, определяемых-, в

делом задачей моделирования или уп равления.

Для двоичных переменных соотно.LieHH (I.) можно записать в виде

4 . .. . ВХ- - .-ЮХ- Л : {2)

j-:i J 1 0, sl|ii

где Yj,, - двоичная переменная J-ro

разряда величины i { i X.gii Xj,,t- двоичные переменные j-x

разрядов величин и . Xi соответственно; , п - -количество разрядов пред, ставления двоичных переменных в вычислителе. Интегро-дифференциальный вычислитель работает следующим образом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегродифференциальный вычислитель | 1981 |

|

SU1007105A1 |

| Интегро-дифференциальный вычислитель | 1981 |

|

SU1020823A1 |

| Интегро-дифференциальный вычислитель | 1980 |

|

SU960813A1 |

| Интегро-дифференциальный вычислитель | 1983 |

|

SU1108445A2 |

| Интегро-дифференциальный вычислитель | 1980 |

|

SU955051A1 |

| Цифровой регулятор | 1980 |

|

SU938255A1 |

| Цифровой регулятор | 1979 |

|

SU938253A1 |

| Цифровой регулятор | 1981 |

|

SU974336A1 |

| Цифровой регулятор | 1982 |

|

SU1056130A2 |

| Устройство для вычисления квадратногоКОРНя | 1979 |

|

SU809172A1 |

.В исходном состоянии триггеры 10-12 находятся в нулевом состоянии. Сигнал инверсного выхода триггера 1-0. совместно с сигналом инверсного выхода триггера 12 поддерживает элемент 18 в открытом состоянии:

Элемент 17 И закрыт сигналом прямого выхода триггера 10, а элемент 19 И закрыт сигиалом прямого выхода триггера 11.

Элементы 21 И,24 И и 25 И открыты сигналами с инверсного выхода три гера 12, сигналы прямого выхода которого поддерживают в закрытом состоянии элементы.20 И и 23 И. Элементы 22 VL и 25 И по вторым входам закрыты сигналами с четвертого и пятого выходов блока 9 синхронизации соответственно.

В регистр 1 из (п-1) - н разрядов который дополняется элементов 16 задержки до п разрядов, записывается двоичный код начальных условий

YO . .Если, YO отрицательная величина то в. регистр 1 записывается дополни.тельинй код YQ.

В регистре 2, емкостью Зп разрядов, хранятся последовательным способом три п разрядных постоянных коэффициента А, В и С, которые предварительно вычислены в таблице для данного вида интегро-дифференци-. -шьного преобразования.

в старшие п разрядов регистра 3, емкостью 2п разрядов, записываются двоичные коды начальных условий Х, а младшие.п разрядов регистра 3 очищены.

Регистр 4 содержит п-1 разряд и в исходном состоянии очищен.

Как видно из таблицы знаки коэффициентов А и С всегда положительны для этих передаточных функций, знак коэффициента в записывается в триггер 33 блока 8 знака.

Знак начального условия YO записывается в триггер 34 блока 8 знака и в последний (старший) разряд .регистра 1 .

Знак начального условия X записывается в первый разряд регистра 31 сдвига блока 8.

После пуска интегрр-дифференциального вычисления генератор 37 блока 9-синхронизации Начинает вырабатывать тактовые сигналы с частотой f, которые с помощью делителя 38 частоты, имеющего коэффициент деления равный л , преобразуются в сннхро- низирующие импульсы п-ных разрядов, действующих с частотой f/n на первом выходе- 43 блока 9 синхронизации, на четвертом выходе 45 которого с помощью элемента 39 задержки вырабатываются синхронизирующие импульсы первых разрядов, действующие также с частотой f/п.

Счетчик 40 имеет коэффициент пересчета К-3 и осуществляет деление частоты входных импульсов в три раза. Таким образом, на выходе переполнения счетчика 40 действуют синхронизирующие импульсы с частотой f/3n , которые поступают на .пятый выход 46 блока 9 синхронизации, и на вход делителя 41. Дешифратор 4 2 из выходных сигналов триггеров счетчика 40 выделяет три выходные последовательности сигналов сдвинутых друг относительно друга на длительность n/f и действующих с частотой f/3n. Выходные сигналы дешифратора 42 управляют работой коммутатора 32 блока 8 знака.

Делитель 41 имеет коэффициент деления равный п , На выходе делителя 41 вырабатываются импульсы, период которых равен .

Эти импульсы, поступая на второй выход 44 блока 9 синхронизации определяют время одного цикла вычислений.

На вход 26 иНтегро-дифференциального вычислителя поступает двоичный сигнал, соответствующий знаку входной величины Х;, а на вход 27 последовательно, начиная с младших разрядов, подается двоичный код абсолютной величины Xj ..

Первый импульс на втором выходе 44 блока 9 синхронизации установит триггер 12 в единичное состояние и поступив на ширину сдвига регистра 31 блока 8, сдвинет знак начального условия Хр во второй разряд, а в первый разряд регистра сдвига 31 запишет знак входной величины Х на первом цикле вычислений.

Переход триггера 12 в единичное состояние обеспечивает блокировку элемента 18 И, 21 И, 24 И, 25 И сигналом с инверсного вЕлхода и отпирание элементов 20 И и 23 И сигналом

с прямого выхода.

Двоичный абсолютной величины входа Х. на первом цикле вычислений поступает последовательным способом, начиная с младших разрядов, с входной шины 27 через элементы 23 И. и , 15 ИЛИ на вход регистра.3, в котором в это время двоичный код начальных условий Хд сдвигается из п старших р азрядов в п младших разрядов. Таким образом, и группе п -старших разрядов регистра 3 записывается двоичный

код Х, а в группе п младших разрядов двоичный код Хр.

В это время двоичный код начальных условий YO с выхода регистра 1 через элемент 16 задержки поступа5 ет на первый вход блока 7, на второй вход которого поступает с выхода триггера 34 через коммутатор 32 блока 8 двоичный код знака YQ .

Если знак VQ положительный, то

0 блок 7 пропускает двоичный код величины YQ без изменения, а в случае . отрицательного знака YQ преобразует код величины У в дополнительный код. Так как в исходном состоянии начальные условия YQ записываются в регистр 1 с учетом знака в дополнительном коде, то На выходе блока 7 образуется прямой код абсолютной величины lYpi независимо от знака.

.. Прямой код абсолютной величины 1Уд| с выхода блока 7 поступает последовательным способом, начиная с младших разрядов, через элемент 20 И и 14 ИЛИ на первый вход элемента

. 22 И и вход регистра 4.

На второй вход элемента 22 И с четвертого блока 9 синхронизации поступает синхронизирующий импульс первого разряда,

0 ЕСЛИ в первом разряде абсолютной величины YP записан нулевой код, то элемент 22 И останет.ся закрытым и триггер 11 не изменит своего нулевого состояния.

ij Если в первом разряде абсолютной величины YO записан единичный код, то элемент 22 И сработает и установит триггер 11 в единичное состояние, что приведет к отпиранию элеQ мента 19 И сигналом прямого выхода триггера 11.

Двоичный код коэффициента А считывается с выхода регистра 2 последовательным способом, начиная с мла дших разрядов и через элемент 19 И

5 поступает на первый вход блока б дополнительного кода, на второй вход которого поступает в это время знак YO с выхода блока 8-.

Если знак YO положительный, то

0 блок -б пропускает двоичный код коэффициента А без изменения на первый вход сумматора- 5.

Если знак YP отрицательный, то блок б преобразует код коэффициента

5 А в дополнительный код.

Поскольку в это время триггер 10 находится в нулевом состоянии, а триггер 12 - в единичном, то элементы 17 И и 18 И закрыты сигналом прямого выхода триггера 10 и сигна-лом инверсного выхода триггера 12 соответственно. В результате на втором входе сумматора 5 действует нулвой код с выхода элемента 13 ИЛИ.

Прямой или дополнительный код коэффициента А с выхода блока 6 записывается через сумматор 5 в. регистр 1, после чего синхронизирующий сигнал п-го разряда с первого выхода блока 9 синхронизации сбросит триггеры 11 и 12 в нулевое состояние.

Переход триггера 12 в нулевое состояние обеспечивает с помощью элемента 20- И отключение выхода блока 7 от входной цепи регистра 4 и отключение с помощью элемента 23И входной шины 27 от входной цепи регистра -3.

Отпирание элементов 21 И и 24 И сигналом инверсного выхода триггера 12 обеспечивает подключение выхода регистра 3 к входу регистра 4, выхо которого подключается к входу регистра 3.

В результате регистры 3 и 4 объединяются в один регистр общей емкостью в Зп - 1 двоичный разрядов. Причем, в момент объединения с выхода регистра 3 считывается первый разряд кода Хд , а с выхода регистра 4 - второй разряд кода YO .

Первый (младший) разряд кода Xg с выхода регистра 3 поступает через элементы 21 И и ,14 ИЛИ на первый вход элемента 22 И и на вход регистра 4.

Если в первом разряде величины Хр записан единичный код, то элемент 22 и срабатывает и установит триггер 11 в едииничное состояние, который сигналом прямого выхода открывает элемент 19 И.

В это время с выхода регистра 2 считывается последовательным способом, начиная с младших разрядов, двоичный код коэффициента в, который поступает через блок б впрямом или дополнительном коде в зависи7 мости от знака произведения в Хд на первый вход сумматора 5. Знак произведения в XQ формируется элементом несовпаден1йя 35 и через коммутатЬр 32- блока 8 подается на второй вход блока 6.

На первый вход сумматора 5 в это время поступает с выхода регистра 1 через элемент. 16 задержки, элемент 18 И и элемент 13 ИЛИ коэффициент А, ранее записанный в регистр 1. Элемент 18 И открыт, так как триггеры 10 и 12 находятся в нулевом состоянии.

CyNMaTop 5 произведет суммирование коэффициентов А и В последовательным способом. Безультат суммирования с выхода сумматора 5 записывается в регистр 1.

После сложения коэффициентов А и В g выхода регистра 2 считывается 2 коэффициент С, в это времяс выхода регистра 3 поступает двоичный код величины Х, начиная с младшего разряда. Первый разряд кода выхода регистра 3 через элементы 21 И и 14

ИЛИ поступает на первый вход элемен0

та. 22 И и вход регистра 4.

Если в первом.разряде величины Хзаписан единичный код, то элемент 22 Д срабатывает и установит триггер 11 в единичное состояние.

5 Коэффициент С с выхода регистра 2 через элемент 19 И, открытый прямым выходом триггера 11, и блок б поступает в прямом или дополнительном коде в зависимости от знака

0 величины X, на первый вход сум-. матора 5. Код знака величины Х . считывается с первого разряда регистра 31 и с помощью коммутатора 32 блока 8 знака подключается к второ5 входу блока б.

Таким образом, на первый вход сумматора 5 поступает или дополнительный код коэффициента С, а на его второй вход считывается с

„ выхода регистра 1 через элемент 16

задержки, элемент 18 И и элемент 13 ИЛИ двоичный код предыдущей суммы коэффициентов А и В.

Сумматор 5 выполняет сложение двоичных кодов коэффициентов С, А+В

5 и результат сложения записывается в регистр 1.

После этого.на пятом выходе 46 блока 9 синхронизации вырабатывается импульс, который пройдет через

0 элемент 25 И, открытый сигналом инверсного выхода Триггера 12, на прямой вход триггера 10 и установит его в единичное состояние.

Переход триггера 10 в единичное

5 состояние приводит к подключению выхода регистра 1 с помощью элемента 17 И, открытого сигналом прямого выхода триггера 10, и элемента 13 ИЛИ, к второму входу сумматора 5. При

0 этом, элемент 18 И закрыт сигналом инверсного выхода триггера 10, обеспечивая стираниес младшего, разряда суммы коэффициентов.

Подключение выхода регистра 1 к второму входу сумматора приводит к

5 сдвигу информации в регистре 1 на один разряд в сторону младших разрядов по отношению к синхронизирующим импульсам четвертого выхода 45 блока 9 синхронизации. В результате

0 сдвига информация fi регистре 1, который содержит п - 1 разряд, с синхронизирующим импульсом первого разряда на четвертом выходе 45 блока 9 синхронизации совпадает второй разряд

5 суммы коэффициентов, записанной в регистре 1. В случае сдвига на один разряд в регистре 1 дополнительного кода, накопленной суммы коэффициентов, знаковый разряд сдвигается в разряд по правилу сдвига дополпительного кода и перезаписывается с выхода регистра 1 через элемент 16 задержки, элементы 18 И и 13 ИЛИ сумматор 5 на вход регистра 1 по ме ту -п-го разряда. Триггер 10 в это время устанавливается в нулевое состояние сигналом первого выхода 43 блока 9 синхронизации, обеспечивая восстановление в п-ом разряде единичного кода знака. В регистре 2, который содер) Зп разрядов, сдвиг информации относительно синхронизирующих импульсов блока 9 синхронизации отсутствует.

Таким образом, сдвиг информации, в регистре 1на один разряд обеспечивает умножение на два.суммы коэффициентов. Сдвиг информации на один разряд.в регистре, состоящем и регистров 3 и 4, обеспечивает.совпадение с первыми разрядами коэффициентов А, в и С следующих вторых разрядов соответствующих величин YO / X Q и X .J.

Второй разряд .величины Y считывается с выхода )егистра 3 и через элементы 21 И и 14 ИЛИ поступает на первый вход элемента 22 И, на вт рой вход которого с четвертого выхода блока 9 синхронизации поступает синхронизирующий импульс первого разряда коэффициентов А, В и С.

Если во втором разряде величины YP записан единичный код, то элемент 22 И срабатывает, устанавливая триггер 11 в единичное со.стояние. . Элемент 19 И открывается сигналом прямого выхода триггера 11, Двоичны код коэффициента А с выхода регистра 2-через элемент 19.И поступает на первый вход блока б дополнительного кода, на второй вход которого с выхода.блока. 8 подается сигнал знака величины YQ

Прямой или дополнительный код коэффициента А с выхода блока б подается на первый вход сумматора 5, на второй вход которого через элементы 13 ИЛИ и 18 И, открытый сигналом прямого выхода триггера 10, с выхода регистра 1 поступает, начиная с второго разряда, накопленная в результате предьщущих вычислений сумма коэффициентов А, В и С

Сумматор 5 выполняет суммирование , а результат записывается в регистр 1, после чего триггер 10 сб.расываетсЯ в нулевое состояние синхрЬнизирующим сигналом первого выхода 43 блока 9 синхронизации. Переход триггера 10 в нулевое состояние обеспечивает дополнение , регистра 1, имеющего п-1 разряд, до п - разрядов с помощью элемента 16 задержки-И .элемента 18 JI открытого сигналом инверсного выхода триггера 10. Элемент 17 И закрывается сигналом прямого выхода триггера 10, обеспечивая отклюс чение выхода регистра 1 от второго входа сумматора 5-.

Дополнение регистра 1 до п разр ядов обеспечивает отсутствие сдвига информации в регистре 1 до следующего синхронизирующего .импульса на пятом выходе46 блока 9 синхронизации, который сформируется Спустя время 3n/f. За это время сумматор выполнит сложение произведений, коэффициентов А, В и С на соответствующие двоичные переменные вторых разрядов величины Y Q / X р Х.

После генерации: импульса на пятом выходе 46 блока 9 синхронизации произойдет сдвиг информации на один разряд в регистре 1 и регистре, образованном регистрами 3 и 4, также, как ранее описано.

Сумматор 5 осуществит сложение . произведений коэффициентов А, В и С на соответствующие двоичные переменные третьих разр.чдов величин Y , .д, до тех пор, пока на втором выходе 44 блока 9 синхронизации не вырабатывается выходной импульс, который сформируется спустя интервал времени после пуска устройства .

За это время в регистре 1, дополненном элементом 16 задержки до п разрядов, накапливаются старшие п разрядов выходной величины Y согласно соотношению (2) , которые будут служить начальными условиями

0 для следующего цикла вычислений.

В регистре, образованном объединением регистра 3 и 4 за время 3n5f произойдет сдвиг информации на п-разрядов, в результате которого

к двоичный код в-еличины Х сдвинется на место двоичного кода начальных условий XQ.

Таким образом, вместо начального условия-Yg в регистре 1 образовал-ся двоичный код .нового значения

выходной величины V ... В группе п младшик разрядов регистра 3 сдвигом вместо начального условия XQ получен двоичный код входной величины первом цикле вычислений. ТриГ-геры 10, 11 и 12 находятся в нулевом состоянии. Один цикл вычислений завершился и устройство вернулось в исходное состояние, но с новыми значениями начальных условий, в процессе вычислений .интегро-диффе ёнциальный вычислитель 6yjieT работать аналогичным образом.

Например второй цикл вычислении начнется с момента генерации второго импульса на втором выходе 44 блока 9 синхронизации, который установит триггер 12 в единичное состояние и, воздействуя на шину сдвига регистра 31, сдвинет знак входной величины,Х во второй разряд регистра 31, а в его первый разряд запишет знак входной величины Х. Кроме этого,, импульс синхронизации со второго выхода 43 блока 9 си хронизации поступит на первый вход элемента 36 И блока 8.Если в резуль тате вычислений выходная величина Y изменит знак, то в регистре 1 образуется дополнительный код старших разрядов выходной величины и в п-ом знаковом разряде появится сигнал единичного кода, который с выхо .д сумматора 5 поступает на второй вход элемента 36 И блока знака. Сра батывание элемента 36 И приводит к переходу триггера 34,который при положительном знаке выходной величины находился в нулевом состоянии в единичное состояние, соответствую щее отрицательному знаку выходной величины. Триггер 12 в единичном состоянии осуществляет блокировку сдвига в регистре 1 следующим образом Сигнал с инверсного выхода триггера 12 закрывает элемент 25 И,, запрещая установку триггера 10 в единичное состояние. Поэтомуво время нахождения триггера 12 в единичном состоянии регистр 1 дополняется элементом 16 задержки до п-разрядов и старшие п разрядов вычисленной величины У с выхода элемента 16 задержки поступают через блок 7, элемент Г20, открытый сигналом прямоговыхода триггера 12, и элемент 14 ИЛИ в виде прямого кода абсолютной величины |Y.,| на вход регистра 4 и первый вход элемента 22 И. Двоичный код абсолютной величины входа jXgiHa втором цикле вычислений записывается последовательным способом с входной шины 27 в старшие п разрядов регистра 3, в котором в это.время двоичный код входа X:j на первом цикле вычислений сдвигается из п старших в п младшие раз ряды регистра 3.. Двоичный код начального условия входа Хд сдвигается из п-младших .разрядов регистра 3 на его выход и стирается, так как элемент 21 И закрыт сигналом инверсного выхода триггера 12, который блокирует также элемент 1$ И/ запрещая перезапись старших разрядов величины Y с выхода элемента 16 задержки через сумматор 5 на вход регистра 1, выпо няя этим очистку регистра.1. Таким образом, в интегро-диффере циальном вычислителе записывается новаяХ , / Уi- информация, исходная для следующего i-ro цикла вычислений, и стирается Х;., , Y,-a информация, использованная в предыдущем (i-l)-M цикле вычислениП. Реализация требуемого интегро-дифференциального преобразования в последующих i+1 циклах, выполняется также как и в описанном первом цикле при соответствующих начальных условиях. Следуем отметить, что интегродифференциальный вычислитель можно применять для линейных интегро- . дифференциальных преобразований любого порядка и по любой зависимой входной переменной X(t). Чтобы осуществить интегро-диффеч ренциальное преобразование высокого порядка нужно представить ее в виде произведения элементарных передаточных функций (таблица), .рассчитать их параметры, соединить последовательно ряд одинаковых интегродифференциальных вычислителей в общем случае с различными начальными условиями.и коэффициентами А, В и С« В этом случае выходные шины 28 и 29 каждого предыдущего интегро-дифференциального вычислители подключаются соответственно к входным шинам 26 и 27 последующего интегро-дифферендиального. вычислителя. Причемсинхронизация работы Bcei-O ряда из нескольких одинаковых интегро-дифференциальных вычислителей, реализующих каждый свою.специфическую передаточную функцию, осуществляется от одного и того же блока 9 синхронизации и следовательно в этом случае не требуется дополнительных затрат оборудования. На базе унифицированных интегродифференциальных - вычислителей можно реализовать любые другие сложные, последовательно-параллельиые схег-ал дискретного управления и комплексного моделирования динамических объектов. . Технико-экономические преимущества интегро-дифференциального вычислителя по сравнению с известным заключаются в простоте реализации И повышении быстродействия. Формула изобретения Интегро-дифференциальный вычислитель, содержащий блок синхронизации, регистры, сумматор, блоки формирования дополнительного кода, блок хранения знака, триггеры, элементы И, ИЛИ и элемент задержки, причем вход первого регистра подключен к выходу сумматора и -первому входу блока хранения знака, второй вход кото.рого подключен к первому входу вычислителя, первый вход сумматора соединен с выходом первого блока формирования дополнительного кода.

второй вход сугФдатора подключен к выходу первого элемента ИЛИ, входы которого подключены соответственно ;к выходам первого и второго элементов И, первые входы которых подключены соответственно к прямому и инверсному выходам первого триггера, выход первого регистра подключен- ко второму входу первого элемента И.первый выход блока синхронизации подключен к инверсным входам первого, второго и третьего триггеров , второй выход - к третьему входу блока хранения знака, группа выходов. - к группе входов блока хранения знака, о т л и ч аю щ и и с я тем, что, с целью упрощения вычислителя и повышения его быстродействий, второй вход второго элемента И подключен к первому входу второго блока формирования дополнительного кода непосредственно и через элемент задержки - к выходу первого регистра,первый вход первого блока формирования дополнительного кода подключен к выходу третьего элемента И, первый вход которого подключен к выходу второго регистра, второй вход - к прямому выходу второго триггера, вторые входы первого и второго блоков формирования дополнительного кода подключены к выходу блока хранения знака и к первому выходу вычислителя, выход второго блока формирования дополнительного кода подключен к первому входу четвертого элемента И, выход третьего регистра подключен к первому входу пятого элемента И, входы второго элемента ИЛИ подключены соответственно к

выходам четвертого и пятого элементов И, вход четвертого регистра подключен к выходу второго элемента ИЛИ и к первому входу шестого элемента И, второйвход которого подключен к третьему выходу блока сихронизации, а вькод - к прямому входу второго триггера, входы трет.ьего элемента ИЛИ подключены соответственно к выходам седьмого и восмого элементов И, выход третьего элемента ИЛИ соединен с входом третьего регистра, первый вход седьмого элемента И подключен ко второму входу вычислителя, второй вход к-прямому выходу третьего триггера инверсный выход которогосоединен с третьим входом второго элемента И, вторым входом пятого элемента И и первыми входами восьмого и девятого элементов И,- второй вход восьмого элемента И подключен к выходу четвертого ре1истра, прямой вход третьего триггера соединен с вторым выходом блока синхронизации, четвертый выход которого подключен ко второму входу девятого элемента И, выход которого соединен с Прямым входом первого триггера, второй выход вычислителя соединен с выходом четвертого элемента И.

Источники информации, принятые во внимание при экспертизе

Г.А. Корна, т. 1, М-Л,, Энергия, 1964, с. 63-71.

Дпрототип).

Фг/2./

, .

.

Авторы

Даты

1981-01-23—Публикация

1979-01-22—Подача