I

Изобретение относится к вычислительной- технике и может быть использовано в цифровых вычислительных машинах.

Известно запоминающее устройство (ЗУ) с электрической сменой информации и со сч;итыванием информации без ее разрушения на микробиаксах.

Такое устройство содержит накопитель, соединенный с формирователями и управляемыми дешифраторами, усилители считывания и синхронизирующее устройство 1 .

Запись информации в этом устройстве производится медленнее, чем в оперативных ЗУ, а считывание быстрее. Неисправности в цепях формирователей разрядных и линейных токов могут привести к искажению ранее записанной информации или к полной ее потере, что недопустимо в высоконадежных устройствах памяти. Ложный запуск формирователей разрядных токов приводит к появлению на выходных схемах ЗУ искаженных кодов чисел Отсутствие внутренйих схем защиты числового блока при записи и считывании является существенным недостатком всех известных ЗУ особенно

при наличии в устройствах памяти встроенных схем записи.

Наиболее близким по технической сущности к предлагаемому изобретению является устройство, содержащее блок управления, накопитель, соединенный ,с формирователями линейных токов и ключами, формирователи разрядных токов, подключенные к накопителю, а

0 также дешифраторы, усилители воспроизведения, связанные с накопителем, регистр, входные и выходные инверторы 21,

Наличие ложного сигнала или по5мехи в режиме считывания, а также неисправность схем питания формирователей разрядных токов и неисправность в самих схемах формирователей разрядных токов может привести к по0тере информации, ее искажению или записи излишней информации. В режиме записи отсутствие разрядных токов приводит к потере старой информации и незаписи новой. Отсутствие одного

5 из линейных токов приводит к искажению записываемой информации. Все это снижает надежность запоминающего устройства.

Цель изобретения - повышение наfдежности устройства.

Поставленная цель достигается тем, то в запоминающее устройство, содеращее блок управления, первый вход которого соединен с шиной запуска, второй вход с шиной считывания-записи, третий вход с шиной установки нуля, а четыре выхода с соответствуюими шинами управления, четыре ключа, ервые входы первых двух из которых соединены с первой шиной управления, а первые входы вторых двух с второй шиной управления, накопитель, входы которого соединены с выходами соответствующих ключей, формирователь разрядного тока, выход которого соединен с соответствующим входом накопителя, и два формирователя линейного тока, в него дополнительно введены три блока фиксации тока, три блока питания, три элемента ИЛИ, четыре элемента и и блок управления, причем вторые входы первых двух ключей подключены к первому выходу первого блока фиксации тока, вторые выходы вторых двух ключей к первому выходу второго блока фиксации тока, вход первого блока фиксации тока подключен к выходу первого формирователя линейного тока, вход которого подключен к выходу первого блока питания, вход которого подключен к первому входу второго элемента ИЛИ, вход второго блока фиксации тока подключен к выходу второго формирователя линейного тока, вход которого подключен к выходу второго блока питания, вход которого подключен к выходу второго элемента ИЛИ, первый вход которого подключен к выходу первого элемента И, второй вход к выходу второго элемента И, второй выход первого блока фиксации тока подключен к первому входу первого элемента ИЛИ, второй вход которого подключен к второму выходу второго блока фиксации тока, первый выход третьего блока фиксации тока подключен к входу формирователя разрядного тока, вход к выходу третьего блока питания, второй выход к перЕОму входу дополнительного блока управления, вход третьего блока питания подключен к выходу третьего элемента ИЛИ, первый вход которого подключен к выходу третьего элемента И, а второй к выходу четвертого элемента И, первые входы первого и третьего элементов И подключены к третьей шине упрайления, первые входы второго и четвертого элементой И подклк)чены к четвертой шине управления, а звторые входы элементов И к соответствующим выходам дополнительного блока управления, второй вход которого подключен к выходу первого элемента ИЛИ.

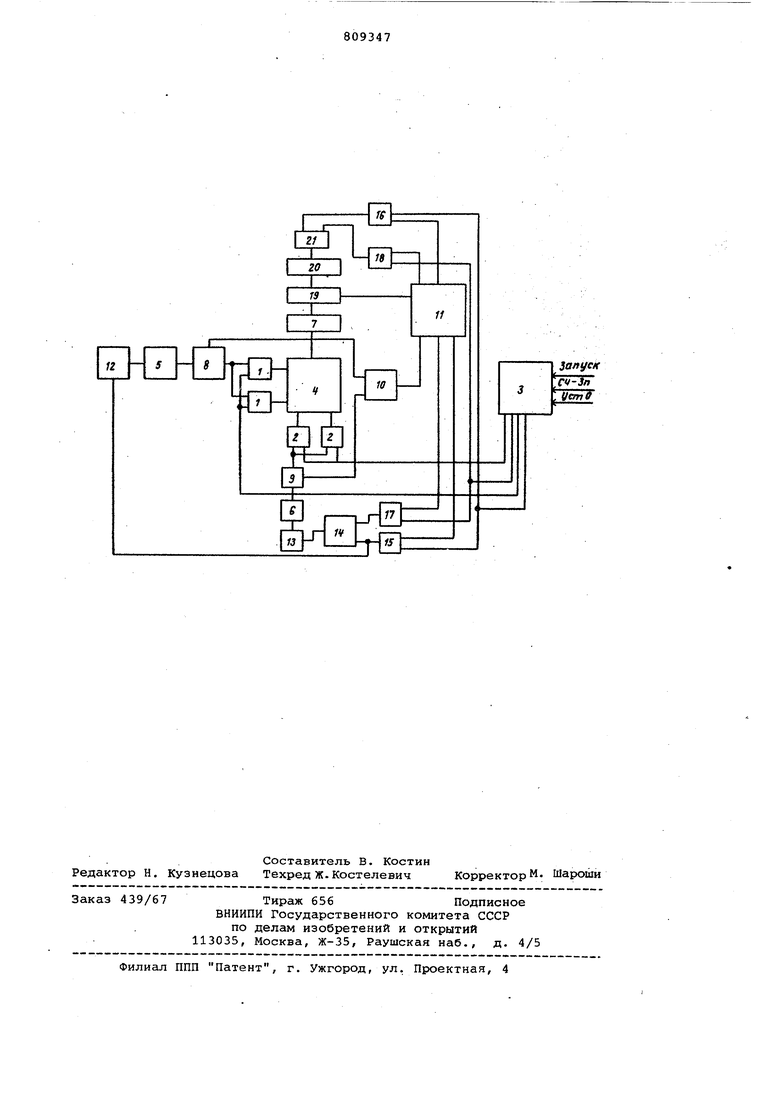

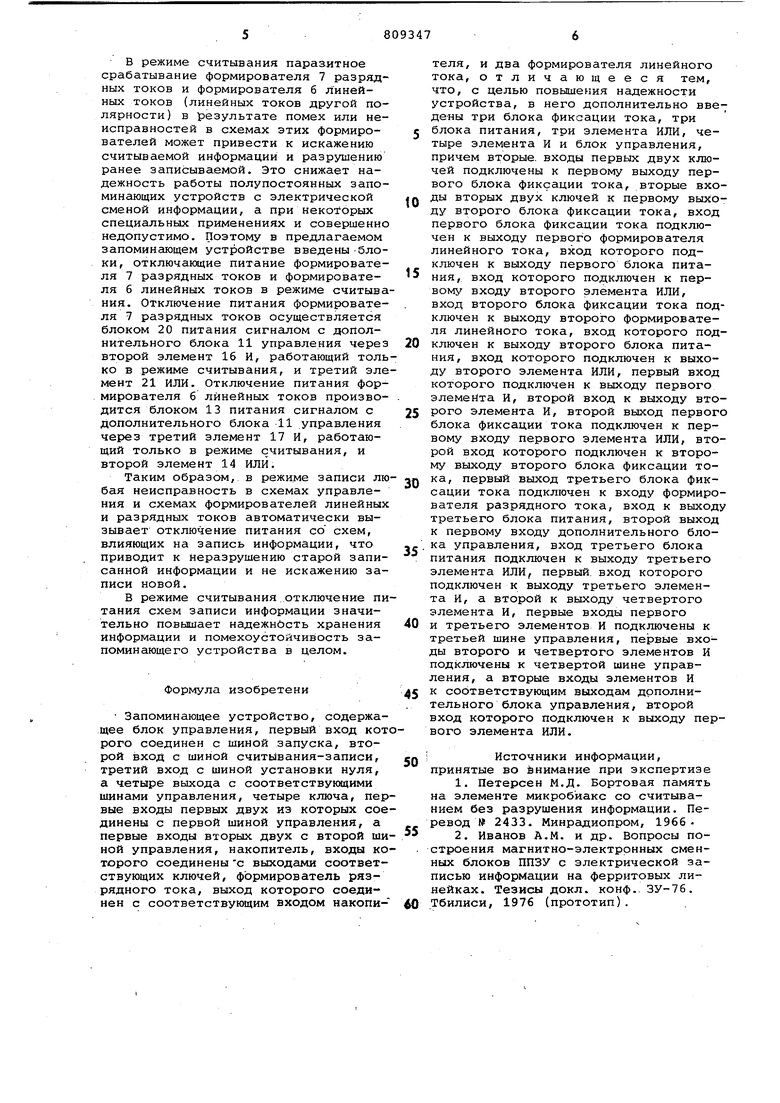

.На чертеже показана схема предлагаемого устройства.

Устройство содержит ключи 1 и 2, блок 3 управления, накопитель 4, формирователи линейных токов 5 и б, формирователь 7 разрядных токов, первый и второй блоки фиксации токов 8 и 9, первый элемент 10 ИЛИ, дополнительный блок 11 управления, первый и втоf рой блоки питания 12 и 13, второй элемент 14 ИЛИ, четыре элемента И 1518, третий блок 19 фиксации тока, третий блок 20 питания и третий элемент 21 ИЛИ.

Устройство работает следующим образом.

В режиме записи на блок 3 управления из внешних устройств поступают сигналы Установка О, Считывание запись и 3-апуск. Все схемы блока 3 управления подготавливаются к работе, и по сигналам с дешифратора, находящемся в блоке 3 управления, открываются выбранные ключи 1 и 2. От формирователя 5 линейных токов по

0 одной из линеек накопителя 4 протекает ток одной полярности, а от формироватеЛя б линейных токов по той же линейке - ток другой полярности. Формирователь 7 разрядных токов в

5 разрядных шинах записи-считывания накопителя .4 формируют токи записи 1 и О в соответствии с пришедший из внешних устройств кодом числа, который надо записать в выбранную

Q ячейку запоминакмдего устройства. Сигнал наличия линейного тока одной полярности регистрируется блоком 8 фиксации тока, а сигнал наличия линейного тока другой полярности регисте рируется блоком 9 фиксации тока и

через первый элемент 10 ИЛИ подаются в дополнительный блок 11 управления. Сигналы наличия разрядных токов регистрируются блоком 19 фиксации тока и также подаются на дополнительный

0 блок 11 управления. При отсутствии

сигналов .наличия разрядных токов, что ,приводит к разрушению старой информации и незаписи новой, дополнительный блок 11 управления формирует сигнал

5 оттключения напряжения питания, который через первый элемент 15 И, работающий только в режиме записи, и через второй элемент 14 ИЛИ с помощью блоков питания 12 и 13 отключает питание с формирователей линейных токов 5 и б. В этом случае, даже в случае отказа блоков управления и формирователей линейных токов 5 и б подача двуполярных токов в линейку наf копителя 4 прекращается. При отсутствии одного из линейных токов, что может привести к .искажению ранее записанной информации и незаписи новой, дополнительный блок 11 управления через четвертый элемент 18 И, также

0 работающий только в режиме записи, с помощью блока 20 питания отключает питание с формирователей 7 разрядных токов, исключая появление токов в разрядных шинах записи-Считывания

5 накопителя 4. В режиме считывания паразитное срабатывание формирователя 7 разрядных токов и формирователя б Линейных токов (линейных токов другой полярности) в результате помех или неисправностей в схемах этих формирователей может привести к искажению считываемой информации и разрушению ранее записываемой. Это снижает надежность работы полупостоянных запоминсшзщих устройств с электрической сменой информации, а при некоторых специальных применениях и совершенно недопустимо. Поэтому в предлагаемом запоминающем устройстве введеныблоки, отключающие питание формирователя 7 разрядных токов и формирователя б линейных токов в режиме считыва ния. Отключение питания формирователя 7 разрядных токов осуществляется блоком 20 питания сигналом с дополнительного блока 11 управления через второй элемент 16 И, работающий толь ко в режиме считывания, и третий эле мент 21 ИЛИ. Отключение питания формирователя б линейных токов производится блоком 13 питания сигналом с дополнительного блока 11 управления через третий элемент 17 И, работающий только в режиме считывания, и второй элемент 14 ИЛИ. Таким образом, в режиме записи лю бая неисправность в схемах управления и схемах формирователей линейных и разрядных токов автоматически вызывает отключение питания со схем, влияющих на запись информации, что приводит к неразрушению старой записанной информации и не искажению записи новой. В режиме считывания отключение пи тания схем записи информации значительно повышает надежность хранения информации и помехоустойчивость запоминающего устройства в целом. Формула изобретени Запоминающее устройство, содержащее блок управления, первый вход кот рого соединен с шиной запуска, второй вход с шиной считывания-записи, третий вход с шиной установки нуля, а четыре выхода с соответствующими шинами управления, четыре ключа, пер вые входы первых двух из которых сое динены с первой шиной управления, а первые входы вторых двух с второй ши ной управления, накопитель, входы ко торого соединены с выходами соответствующих ключей, формирователь рязрядного тока, выход которого соединен с соответствующим входом накопителя, и два формирователя линейного тока, отличающееся тем, что, с целью повышения надежности устройства, в него дополнительно введены три блока фиксации тока, три блока питания, три элемента ИЛИ, четыре элемента и и блок управления, причем вторые, входы первых двух ключей подключены к первому выходу первого блока фиксации тока, вторые входы вторых двух ключей к первому выходу второго блока фиксации тока, вход первого блока фиксации тока подключен к выходу первого формирователя линейного тока, вход которого подключен к выходу первого блока питания, вход которого подключен к первому входу второго элемента ИЛИ, вход второго блока фиксации тока подключен к выходу второго формирователя линейного тока, вход которого подключен к выходу второго блока питания, вход которого подключен к выходу второго элемента ИЛИ, первый вход которого подключен к выходу первого элемента И, второй вход к выходу второго элемента И, второй выход первого блока фиксации тока подключен к первому входу первого элемента ИЛИ, второй вход которого подключен к второму выходу второго блока фиксации тока, первый выход третьего блока фиксации тока подключен к входу формирователя разрядного тока, вход к выходу третьего блока питания, второй выход к первому входу дополнительного блока управления, вход третьего блока питания подключен к выходу третьего элемента ИЛИ, первый, вход которого подключен к выходу третьего элемента И, а второй к выходу четвертого элемента И, первые входы первого и третьего элементов И подключены к третьей шине управления, первые входы второго и четвертого элементов И подключены к четвертой шине управления, а вторые входы элементов И к соответствующим выходам дрполнительного блока управления, второй вход которого подключен к выходу первого элемента ИЛИ. Источники информации, принятые во внимание при экспертизе 1.Петерсен М.Д. Бортовая память на элементе микробиакс со считыванием без разрушения информации. Перевод 2433. Минрадиопром, 19662.Иванов A.M. и др. Вопросы построения магнитно-электронных сменных блоков ППЗУ с электрической записью информации на ферритовых линейках. Тезисы докл. конф.. ЗУ-76. Тбилиси, 1976 (прототип).

Запуск СЧ-Зп

| название | год | авторы | номер документа |

|---|---|---|---|

| Полупостоянное запоминающее устройство | 1980 |

|

SU900314A1 |

| Полупостоянное запоминающее устройство | 1978 |

|

SU746733A1 |

| Запоминающее устройство | 1980 |

|

SU873275A1 |

| Запоминающее устройство | 1979 |

|

SU809368A1 |

| Запоминающее устройство | 1979 |

|

SU858094A1 |

| Запоминающее устройство | 1980 |

|

SU911614A1 |

| Запоминающее устройство | 1978 |

|

SU765876A1 |

| Запоминающее устройство | 1977 |

|

SU621022A1 |

| Запоминающее устройство | 1979 |

|

SU826417A1 |

| Полупостоянное запоминающее устройство | 1978 |

|

SU765875A1 |

Авторы

Даты

1981-02-28—Публикация

1979-06-04—Подача