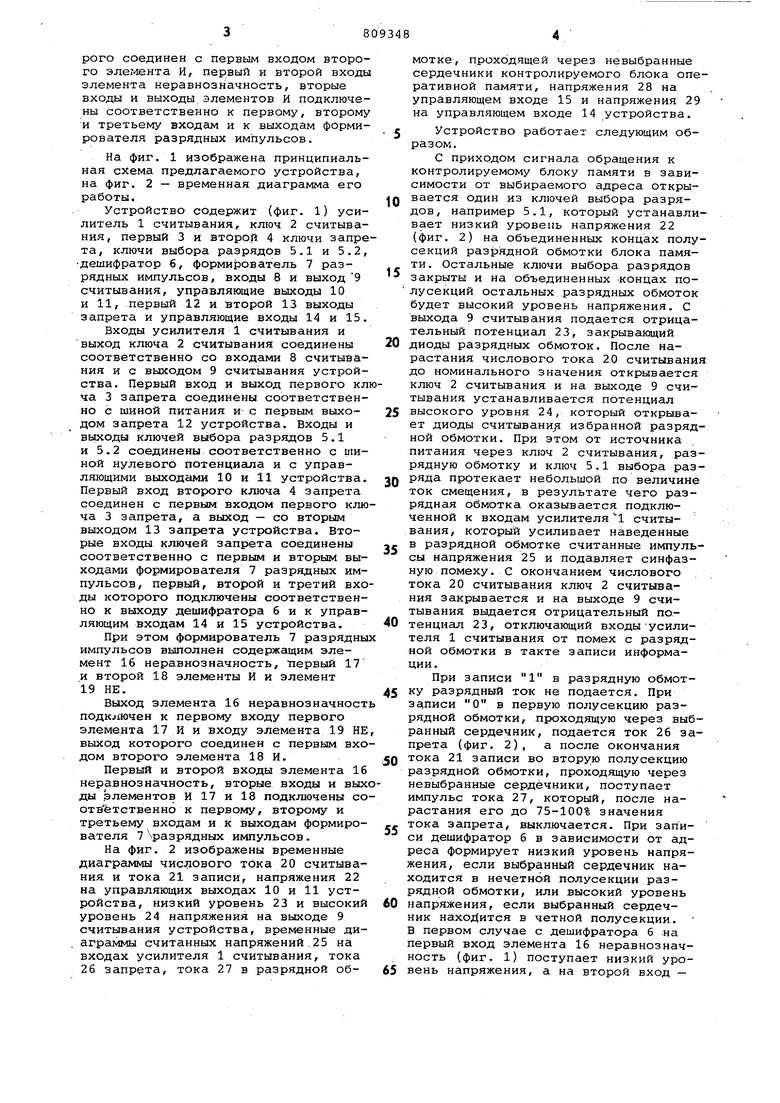

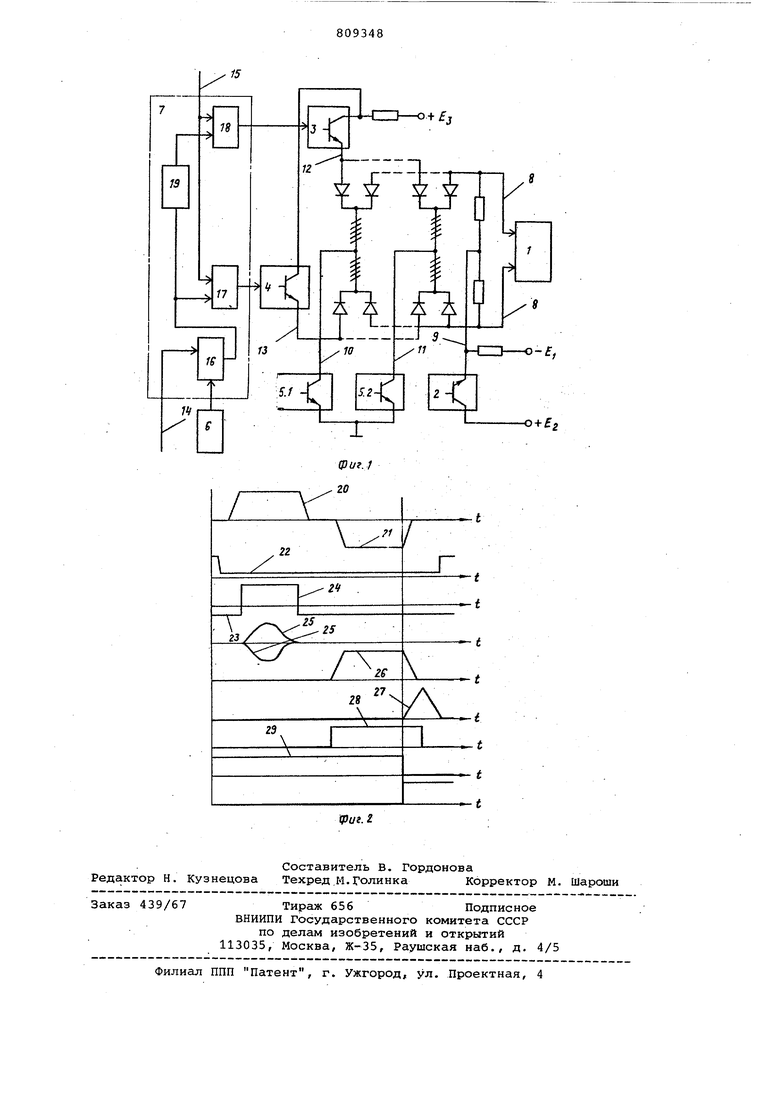

Изобретение относится к запоминающим устройствам. Известно устройство, в котором в разрядную обмотку считывания-запрета подается двойной ток запрета 1. Недостатком этого устройства является двойное потребление разрядного тока. Наиболее близким техническим решением к предлагаемому изобретению является устройство для записи и счи тывания информации из блоков памяти на магнитных сердечниках, содержащее ключ выбора секций разрядных обмоток ключи чтения и записи и дифференциальный усилитель считывания 23. Недостатком этого устройства является необходимость подавать удвоенное значение тока для записи инфор мации, что увеличивает потребляемую мощность. Цель изобретения - снижение потре ляемой устройством мощности. Поставленная цель достигается тем что в устройство для записи и считывания информации в блоке оперативной памяти, содержащееусилитель считывания, ключ считывания, первый ключ запрета и ключи выбора разрядов, при чем входы усилителя считывания и выход ключа считывания соединены соответственно с входами считывания и с выходом считывания устройства, первый вход и выход первого ключа запрета соединены соответственно с ши-, ной питания и с первым выходом запрета устройства, входы и выходы ключей выбора разрядов соединены соответственно ,с шиной нулевого потенциала и с управляющими выходами устройства, введеньа второй ключ запрета, дешифратор и формирователь разрядных импульсов, причем первый вход второго ключа запрета соединен е первым входом первого ключа запрета, а выход - с вторым выходом запрета устройства, вторые входы ключей запрета соединены соответственно с первым и вторым выходами формирователя разрядных импульсов, первый, второй и третий входы которого подключены соответственно к выходу дешифратора и к управляющим входам устройства. При этом формирователь разрядных импульсов целесообразно выполнить содержащим элемент неравнозначность, два элемента И и элемент НЕ, причем выход элемента неравнозначность подключен к первому входу первого элемента И и входу элемента НЕ, выход которого соединен с первым входом второго элемента И, первый и второй входы элемента неравнозначность, вторые входы и выходы элементов И подключены соответственно к первому, второму и третьему входам и к выходам формирователя разрядных импульсов. На фиг. 1 изображена принципиальная схема предлагаемого устройства, на фиг. 2 - временная диаграмма его работы. Устройство содержит (фиг. 1) усилитель 1 считывания, ключ 2 считывания, первый 3 и второй 4 ключи запре та, ключи выбора разрядов 5.1 и 5.2, -дешифратор 6, формирователь 7 разрядных импульсов, входы 8 и выход 9 считывания, управляющие выходы 10 и 11, первый 12 и второй 13 выходы запрета и управляющие входы 14 и 15. Входы усилителя 1 считывания и выход ключа 2 считывания соединены соответственно со входами 8 считывания и с выходом 9 считывания устройства. Первый вход и выход первого кл ча 3 запрета соединены соответственно с шиной питания и с первым выходом запрета 12 устройства. Входы и выходы ключей выбора разрядов 5.1 и 5,2 соединены соответственно с шиной нулевого потенциала и с управляющими выходгиди 10 и 11 устройства, Первый вход второго ключа 4 запрета соединен с первым входом первого клю ча 3 запрета, а выход - со вторым выходом 13 запрета устройства. Вторые входы ключей запрета соединены соответственно с первым и вторым выходами формирователя 7 разрядных импульсов, первый, второй и третий вхо ды которого подключены соответственно к выходу дешифратора б и к управляющим входам 14 и 15 устройства, При этом формирователь 7 разрядны импульсов выполнен содержащим элемент 16 неравнозначность, первый 17 и второй 18 элементы И и элемент 19 НЕ, Выход элемента 16 неравнозначност пoдкJiючeн к первому входу первого элемента 17 И и входу элемента 19 НЕ выход которого соединен с первым вхо дом второго элемента 18 И, Первый и второй входы элемента 16 неравнозначность, вторые входы и вых ды элементов И 17 и 18 подключены со OTBfeTCTBeHHO к первому, второму и третьему входам и к выходам формирователя 7 разрядных импульсов, На фиг, 2 изображены временные диаграммы числового тока 20 считывания и тока 21 записи, напряжения 22 на управляющих выходах 10 и 11 устройства, низкий уровень 23 и высокий уровень 24 напряжения на выходе 9 считывания устройства, временные диаграммы считанных напряжений.25 на входах усилителя 1 считывания, тока 26 запрета, тока 27 в разрядной обмотке, проходящей через невыбранные сердечники контролируемого блока оперативной памяти, напряжения 28 на управляющем входе 15 и напряжения 29 на управляющем входе 14 устройства. Устройство работает следующим образом. С приходом сигнала обращения к контролируемому блоку памяти в зависимости от выбираемого адреса открывается один из ключей выбора разрядов, например 5.1, который устанавливает низкий уровень напряжения 22 (фиг. 2) на объединенных концах полусекций разр;ядной обмотки блока памяти. Остальные ключи выбора разрядов закрыты и на объединенных -концах полусекций остальных разрядных обмоток будет высокий уровень напряжения, с выхода 9 считывания подается отрицательный потенциал 23, закрывающий диоды разрядных обмоток. После нарастания числового тока 20 считывания до номинального значения открывается ключ 2 считывания и на выходе 9 считывания устанавливается потенциал высокого уровня 24, который открывает диоды считываний избранной разрядной обмотки. При этом от источника питания через ключ 2 считывания, разрядную обмотку и ключ 5.1 выбора разряда протекает небольшой по величине ток смещения, в результате чего разрядная обмотка оказывается подключенной к входам усилителя Ч считывания, который усиливает наведенные в разрядной обмотке считанные импульсы напряжения 25 и подавляет синфазную помеху. С окончанием числового тока 20 считывания ключ 2 считывания закрывается и на выходе 9 считывания выдается отрицательный потенциал 23, отключающий входы-усилителя 1 считывания от помех с разрядной обмотки в такте записи информации. При записи 1 в разрядную обмотку разрядный ток не подается. При записи О в первую полусекцию разрядной обмотки, проходящую через выбранный сердечник, подается ток 26 запрета (фиг, 2), а после окончания тока 21 записи во вторую полусекцию разрядной обмотки, проходящую через невыбранные сердечники, поступает импульс тока 27, который, после нарастания его до 75 -100% значения тока запрета, выключается. При записи дешифратор 6 в зависимости от адреса формирует низкий уровень напряжения, если выбранный сердечник находится в нечетной полусекции разрядной обмотки, или высокий уровень напряжения, если выбранный сердечник находится в четной полусекции, В первом случае с дешифратора 6 на первый вход элемента 16 неравнозначность (фиг. 1) поступает низкий уровень напряжения, а на второй вход -

высокий уровень напряжения с управляющего входа 14.

На вторые входы элементов И 17 и 18 подается высокий уровень напряжения с управляющего входа 15, Элемент 18 И -формирует сигнал, открывающий первый ключ 3 запрета.

В момент выключения тока 21 записи (фиг. 2) на управляющий вход 14 поступает низкий уровень напряжения 29, в результате чего закрывается первый ключ 3 запрета (фиг. 1) и открывается второй ключ 4 запрета.

При этом в нечетной полусекции разрядной обмотки происходит сп тока 26 запрета (фиг. 2), а в четной полусекции - формирование импульса тока 27, после чего закрываются второй ключ 4 запрета и ключ выбора разряда 5.1.

Технико-экономическое преиг ущество предлагаемого устройства заключается в том, что при записи О ток зпрета подается только в одну полусекцию разрядной обмотки, а во вторую - короткий импульс тока, за счет чего на 40% снижается потребляемая мощность,

Формула изобретения

1. Устройство для записи и считыва ния информации в блоке оперативной памяти, содержащее усилитель считывания, ключ считывания, пермай ключ запрета и ключи выбора разрядов, при-чем входы усилителя считывания и выход ключа считывания соединены соответственно с входами считывания не выходом считывания устройства, первый вход и выход первого ключа запрета соединены соответственно с шиной

питания и с первым выходом запрета устройства, входы и выходы ключей выбора разрядов соединены соответственно с шиной нулевого потенциала и с управляющими выходами устройства, отличающееся тем, что, с целью снижения потребляемой мощности, устройство содержит второй ключ запрета, дешифратор и формирователь разрядных импульсов, причем первый вход второго ключа запрета соединен с первым вхрдом первого ключа запрета, а выход - с вторым выходом запрета устройства, вторые входы ключей запрета соединены-соответственно с первым и вторым выходами формирователя разрядных импульсов, первый, второй и третий входы которого подключены соответственно к выходу дешифратора и к управляющим входам устройства.

2. Устройство по п. 1, о т л и - . чающееся тем, что формирователь разрядных импульсов содержит элемент неравнозначность, два элемента И и элемент-НЕ, причем выход элемента неравнозначность подключен к первому входу первого элемента И и входу элемента НЕ, выход которого соединен с первым входом второго элемента И, первый и второй входы элемента неравнозначность, вторые входы и выходы элементов И подключены соответственно к первому, второму и третьему входам и к выходам формирователя разрядных импульсов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР 377874, кл. G 11 С 11/02, 1973.

2. Авторское свидетельство СССР № 523451, кл. G 11 С 7/00, 1976 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1974 |

|

SU487417A1 |

| Магнитное оперативное запоминающее устройство | 1981 |

|

SU980161A1 |

| Запоминающее устройство | 1978 |

|

SU799001A1 |

| Счетчик импульсов | 1983 |

|

SU1112576A1 |

| Запоминающее устройство | 1980 |

|

SU955196A1 |

| ЛОГИЧЕСКОЕ ПОЛНОТОЧНОВ ЗАПОМИНАЮЩЕЕ L'rifc :ИГ УСТРОЙСТВОI.™™———- | 1973 |

|

SU374658A1 |

| Устройство для сопряжения ЦВМ с магнитофоном | 1985 |

|

SU1317445A1 |

| Устройство для вычисления временных интервалов микропроцессорных систем | 1980 |

|

SU960781A1 |

| Запоминающее устройство типа 2,5 д | 1981 |

|

SU999105A1 |

| Устройство для контроля запоминающих матриц | 1979 |

|

SU875468A1 |

Авторы

Даты

1981-02-28—Публикация

1979-05-17—Подача