Изобретение относится к запоминатацим устройствам, Одно из известных устройств представляет многоканальное устройство памяти и регистрации с временным разделением каналов и содержит накопитель информации на сердечниках с прямоугольной петлей гистерезиса Д.

Недостатками этого устройства являются большие аппаратурные затраты.

Из известных устройств наиболее близким техническим решением к предлагаемому является запоминающее устройство, йодержащее накопитель, схему формирования разрядных сигналов, содержащую распределитель, вентили иформирователи записи и считывания п6 количеству разрядов, схему формирования адресЕШх сигналов, ключ пере- йоса и триггер управления, причем накопитель содержит две выходные шиг ны, а разрядные цепи его включены встречно, т.е, один и тот же адресный ток является для четных разрядов током считывания, а для нечетных записи 2 .

Применение двух выходных шин делает накопитель нестандартным и, следовательно, значительно усложняет устройство, что, в свою очередь, снижает- его надежность.

Цель изобретения - повышение надежности и упрощение устройства.

Поставленная цель достигается тем, что в запоминающее устройство, содержащее формирователи записи и считывания, накопитель, адресные входы которого подключены к адресному

10 блоку, а выход соединен с входом усилителя считывания, и распределитель импульсов, введены дешифратор, ключи и элементы задержки, причем входы распределителя импульсов под15ключены соответственно к выходам формирователя считывания и первого элемента задержки, а .выходы - к разрядным входам накопителя и информационным входам дешифратора, управ20лякнций вход которого соединен с выходом формирователя записи, вход которого подключен к выходу первого элемента задержки, входы первого ключа соединены с выходом усилителя считывания, а также с выходом второго элемента задержки и входом формирователя считывания, а выходы - с входсял первого элемента задержки и пер1выи входом второго ключа, второй вход которого подключен

к одному из выходов дешифратора, один из выходов - к входу второго элемента задержки,, другой выход второго ключа является выходом устройства, а выходы дешифратора под ключены к разрядным входам накопителя .

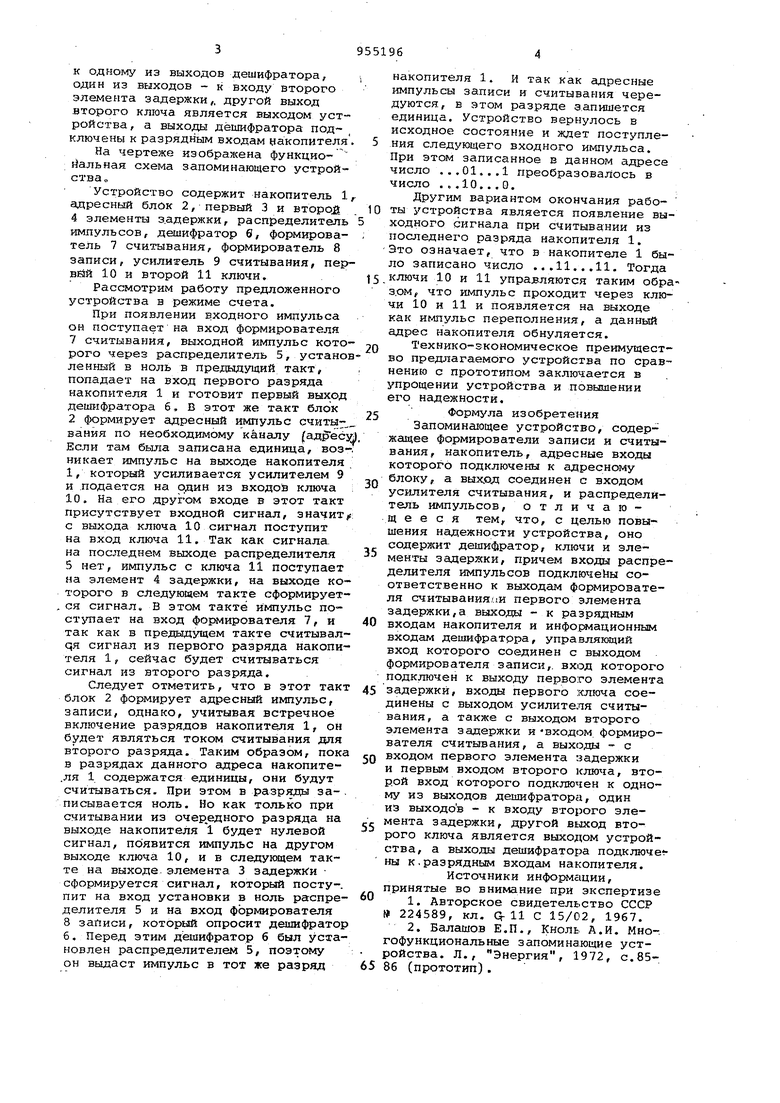

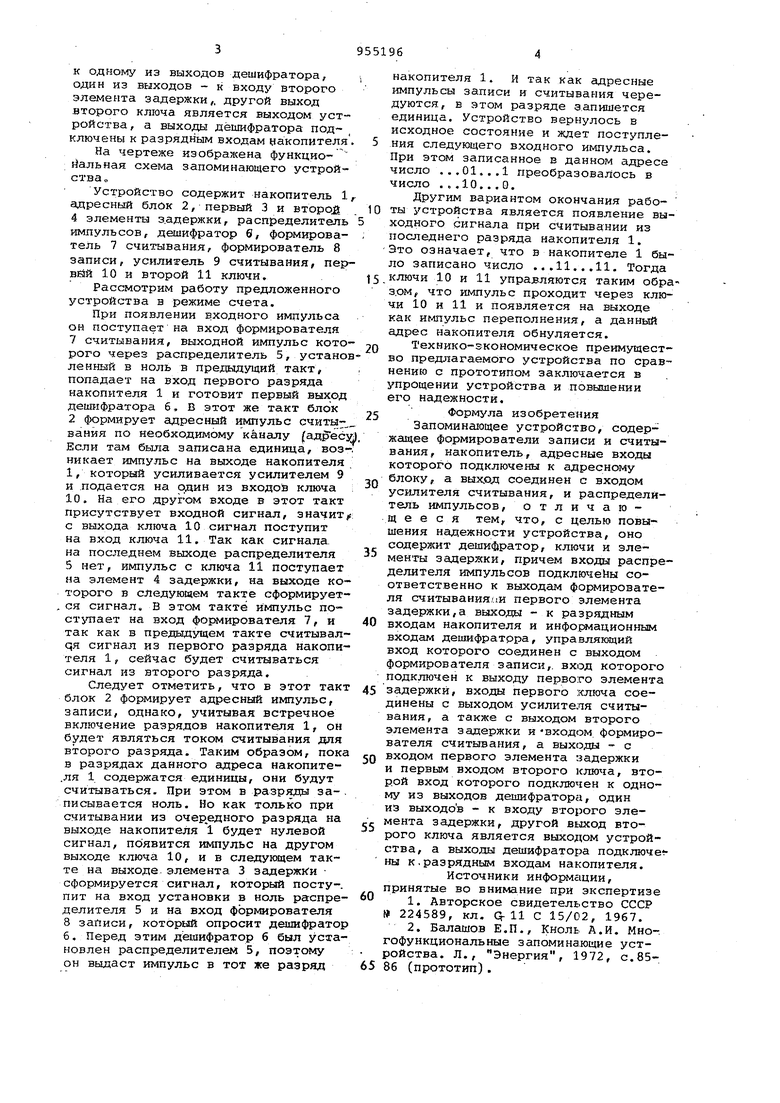

На чертеже изображена функциойальная схема запоминающего устройства „

Устройство содержит накопитель If адресный блок 2, первый 3 и второй

4элементы з.адержки, распределитель импульсов, дешифратор 6, формироватеЛь 7 считывания, формирователь 8 записи, усилитель 9 считывания, первйй 10 и второй 11 ключи.

Рассмотрим работу предложенного устройства в режиме счета.

При появлении входного импульса он поступает на вход формирователя

7считывания, выходной импульс которого через распределитель 5, установленный в ноль в предыдущий такт, попадает на вход первого разряда накопителя 1 и готовит первый выход дешифратора б, В этот же такт блок

2 формирует адресный импульс считы, вания по необходимому каналу (адресй Если там была записана единица, возникает импульс на вьлходе накопителя 1, который усиливается усилителем 9 и подается на один из входов ключа 10. На его другом входе в этот такт присутствует входной сигнал, значит# с выхода ключа 10 сигнал поступит на вход ключа 11, Так как сигнала, на последнем выходе распределителя

5нет, импульс с ключа 11 поступает на элемент 4 задержки, на выходе которого в следующем такте сформируется сигнал. В этом такте импульс поCT TiaeT на вход формирователя 7, и так как в предыдущем такте считывалця сигнал из первого разряда накопителя 1, сейчас будет считываться сигнал из второго разряда,

Следует отметить, что в этот такт блок 2 формирует адресный импульс, записи, однако, учитывая встречное включение разрядов накопителя 1, он будет являться током считывания для второго разряда. Таким образом, пока в разрядах данного адреса накопите.ля 1 содержатся единицы, они будут считываться. При этом в разряды записывается ноль. Но как только при считывании из очер,едного разряда на выходе накопителя 1 будет нулевой сигнал, появится импульс на другом выходе ключа 10, ив следующем такте на выходе, элемента 3 задержки сформируется сигнал, который посту-. пит на вход установки в ноль распределителя 5 и на вход формирователя

8записи, который опросит дешифратор б, Перед этим дешифратор 6 был установлен распределителем 5, поэтому

он выдаст импульс в тот же разряд

накопителя 1. И так как адресные импульсы записи и считывания чередуются, в этом разряде запишется единица. Устройство вернулось в исходное состояние и ждет поступления следующего входного импульса. При этом записанное в данном адресе число .,,01.,. преобразовалось в число . . ,10,,.О,

Другим вариантом окончания работы устройства является появление выходного сигнала при считывании из последнего разряда накопителя 1, Это означает, что в накопителе 1 было записано число ,.,11,,, 11, Тогда ключи 10 и 11 управляются таким обрз.ом, что импульс проходит через ключи 10 и 11 и появляется на выходе как импульс переполнения, а данный адрес накопителя обнуляется.

Технико-экономическое преимущество предлагаемого устройства по сравнению с прототипом заключается в упрощении устройства и повышении его надежности.

Формула изобретения Запоминающее устройство, содержащее формирователи записи и считывания, накопитель, адресные входы которого подключены к адресному блоку, а выход соединен с входом усилителя считывания, и распределитель импульсов, отличающееся тем, что, с целью повышения надежности устройства, оно содержит дешифратор, ключи и элементы задержки, причем входы распределителя импульсов подключены соответственно к выходам формирователя считываниями первого элемента задержки,а выходы - к разрядным входам накопителя и инфо:с 1ационным входам дешифратора, управляющий вход которого соединен с выходом формирователя записи,, вход которого подключен к выходу первого элемента задержки, входы первого ключа соединены с выходом усилителя считывания, а также с выходом второго элемента задержки и «входом формирователя считывания, а выходы с входом первого элемента задержки и первым входом второго ключа, второй вход которого подключен к одному из выходов дешифратора, один из выходов - к входу второго элемента задержки, другой выход второго ключа является выходом устройства, а выходы дешифратора подключе ны к.разрядным входам накопителя.

Источники информсщии, принятые во внимание при экспертизе

1,Авторское свидетельство СССР № 224589, кл, Q-11 С 15/02, 1967,

2.Балашов Е,П,, Кноль А.И, Многофункциональные запоминающие устройства, Л,, Энергия, 1972, с,8586 (прототип),

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1983 |

|

SU1124384A1 |

| Логическое запоминающее устройство | 1977 |

|

SU661609A1 |

| Запоминающее устройство | 1983 |

|

SU1115105A1 |

| Запоминающее устройство типа 2,5 д | 1981 |

|

SU999105A1 |

| Логическое запоминающее устройство | 1978 |

|

SU752479A1 |

| Запоминающее устройство типа 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах | 1979 |

|

SU773731A1 |

| Счетное устройство, сохраняющее информацию при отключении питания | 1987 |

|

SU1492476A1 |

| Магнитное оперативное запоминающее устройство | 1981 |

|

SU980161A1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1983 |

|

SU1088068A1 |

| Запоминающее устройство системы 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах | 1977 |

|

SU693438A1 |

Авторы

Даты

1982-08-30—Публикация

1980-08-15—Подача