Изобретение относится к запоминающим устройствам и может быть использовано при построении постоянных запоминающих устройств (ПЗУ) различных структур со встроенным контролем, ,

Целью изобретения является повышение точности контроля и повышение эффективности.

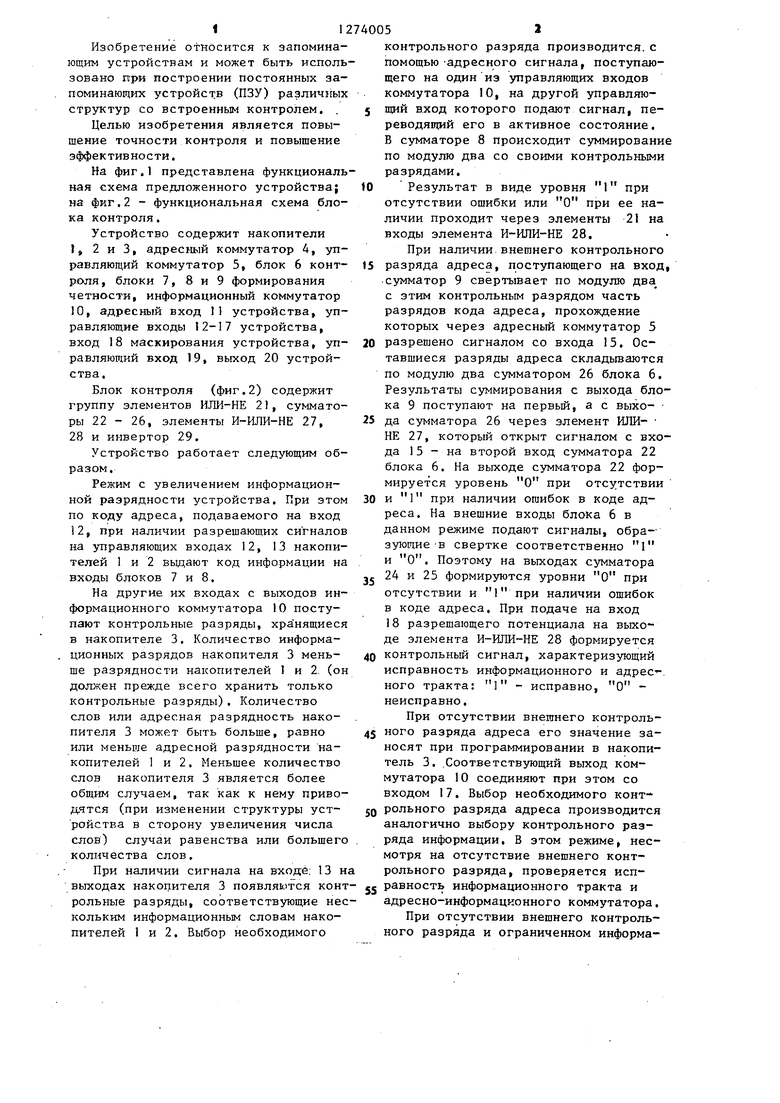

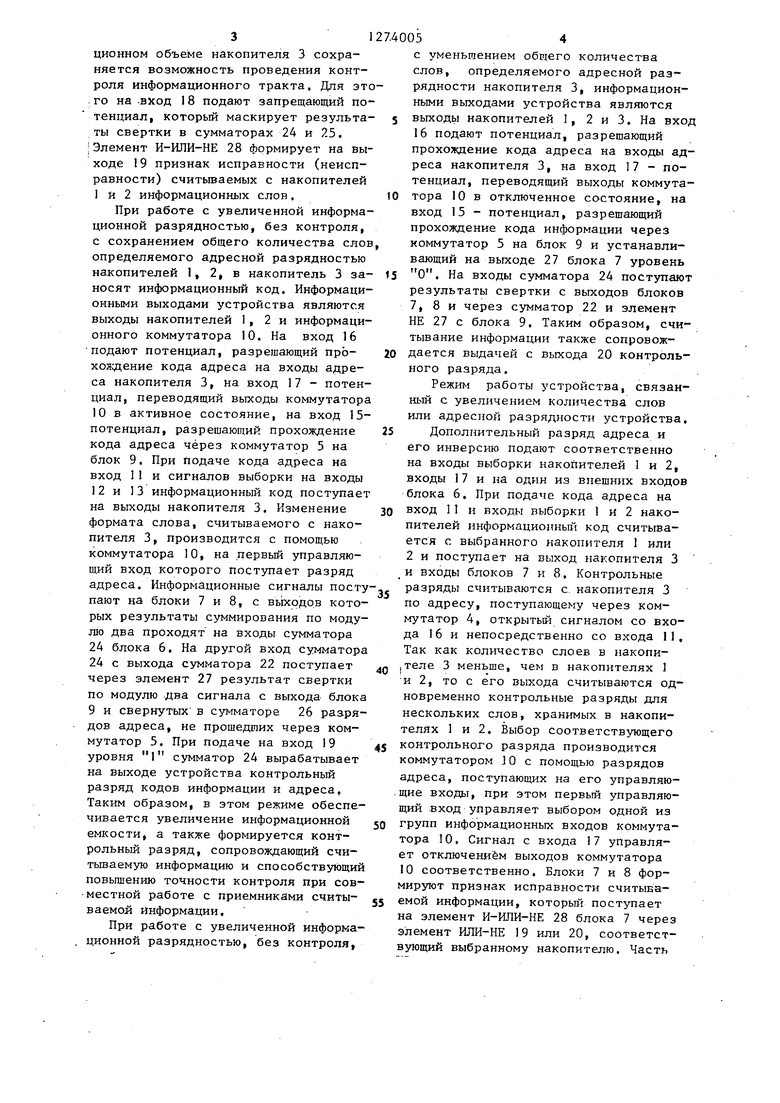

На фиг.1 представлена функциональная схема предложенного устройства; на фиг.2 - функциональная схема блока контроля,

Устройство содержит накопители 1, 2 и 3, адресный коммутатор 4, управляющий коммутатор 5, блок 6 контроля, блоки 7, 8 и 9 формирования четности, информационный коммутатор 10, адресный вход П устройства, управляющие входы 12-17 устройства, вход 18 маскирования устройства, управляющий вход 19, выход 20 устройства.

Блок контроля (фиг.2) содержит группу элементов ИЛИ-НЕ 21, сумматоры 22 - 26, элементы И-ИЛИ-НЕ 27, 28 и инвертор 29.

Устройство работает следующим образом.

Режим с увеличением информационной разрядности устройства. При этом по коду адреса, подаваемого на вход 2, при наличии разрешающих сигналов на управляющих входах 12, 13 накопителей 1 и 2 вьщают код информации на входы блоков 7 и 8.

На другие их входах с выходов информационного коммутатора 10 поступают контрольные разряды, хранящиеся в накопителе 3. Количество информационных разрядов накопителя 3 меньше разрядности накопителей 1 и 2. (он должен прежде всего хранить только контрольные разряды). Количество слов или адресная разрядность накопителя 3 может быть больше, равно или меньше адресной разрядности накопителей 1 и 2. Меньшее количество слов накопителя 3 является более общим случаем, так как к нему приводятся (при изменении структуры устройства в сторону увеличения числа слов) случаи равенства или большего количества слов.

При наличии сигнала на входе. 13 н выходах накопителя 3 появляются контрольные разряды, соответствующие нескольким информационным словам накопителей 1 и 2. Выбор необходимого

контрольного разряда производится.с помощью -адресного сигнала, поступающего на один из управляющих входов коммутатора 10, на другой управляющий В.ХОД которого подают сигнал, переводящий его в активное состояние. В сумматоре 8 происходит суммирование по модулю два со своими контрольньии разрядами.

Результат в виде уровня 1 при отсутствии ошибки или О при ее наличии проходит через элементы 21 на входы элемента И-ИЛИ-НЕ 28.

При наличии внешнего контрольного

разряда адреса, поступающего на вход, сумматор 9 свертывает по модулю два с этим контрольным разрядом часть разрядов кода адреса, прохождение которых через адресный коммутатор 5

разрешено сигналом со входа 15. Оставшиеся разряды адреса складьгеаются по модулю два сумматором 26 блока 6. Результаты суммирования с выхода блока 9 поступают на первый, а с выхо-

да сумматора 26 через элемент ИЛИ- НЕ 27, который открыт сигналом с входа 15 - на второй вход сумматора 22 блока 6. На выходе сумматора 22 формируется уровень О

при отсутствии 1

при наличии ошибок в коде ади реса, На внешние входы блока 6 в

данном режиме подают сигналы, образующие -в свертке соответственно 1 и О. Поэтому на выходах сумматора

24 и 25 формируются уровни О при отсутствии и 1 при наличии ошибок в коде адреса. При подаче на вход 18 разрешающего потенциала на выхо де элемента И-ИЛИ-НЕ 28 формируется

контрольный сигнал, характеризующий исправность информационного и адрес-, ного тракта: 1 - исправно, О неисправно.

При отсутствии внешнего контрольного разряда адреса его значение заносят при программировании в накопитель 3. .Соответствующий выход коммутатора 10 соединяют при этом со входом 17. Выбор необходимого контрольного разряда адреса производится аналогично выбору контрольного разряда информации. В этом режиме, несмотря на отсутствие внешнего контрольного разряда, проверяется испj равность информационного тракта и адресно-информационного коммутатора. При отсутствии внешнего контрольного разряда и ограниченном информационном объеме накопителя 3 сохраняется возможность проведения контроля информационного тракта. Для эт .го на -вход 18 подают запрещающий по тенциал, который маскирует результаты свертки в сумматорах 24 и 25, I Элемент И-ИЛИ-НЕ 28 формирует на вы ходе 19 признак исправности (неисправности) считьшаемых с накопителей 1 и 2 информационных слов. При работе с увеличенной информационной разрядностью, без контроля, с сохранением общего количества слов определяемого адресной разрядностью накопителей 1, 2, в накопитель 3 заносят информационный код. Информационными выходами устройства являются выходы накопителей 1, 2 и информационного коммутатора 10. На вход 16 подают потенциал, разрешающий прохождение кода адреса на входы адреса накопителя 3, на вход 17 - потенциал, переводящий выходы коммутатора 10 в активное состояние, на вход 15потенциал, разрешающий прохождение кода адреса через коммутатор 5 на блок 9. При подаче кода адреса на вход 11 и сигналов выборки на входы 12 и 13 информационный код поступает на выходы накопителя 3. Изменение формата слова, считываемого с накопителя 3, производится с помощью коммутатора 10, на первый управляющий вход которого поступает разряд адреса. Информационные сигналы посту пают на блоки 7 и 8, с вьЬсодов которых результаты суммирования по модулю два проходят на входы сумматора 24 блока 6. На другой вход сумматора 24 с выхода сумматора 22 поступает через элемент 27 результат свертки по модулю два сигнала с выхода блока 9 и свернутых в сумматоре 26 разрядов адреса, не прошедших через коммутатор 5. При подаче на вход 19 уровня 1 сумматор 24 вырабатывает на выходе устройства контрольный разряд кодов информации и адреса. Таким образом, в этом режиме обеспечивается увеличение информационной емкости, а также формируется контрольный разряд, сопровождающий считьшаемую информацию и способствующий повышению точности контроля при совместной работе с приемниками считываемой Информации, При работе с увеличенной информационной разрядностью, без контроля. с уменьшением общего количества слов, определяемого адресной разрядности накопителя 3, информационными выходами устройства являются выходы накопителей I, 2 и 3, На вход 16 подают потенциал, разрешающий прохождение кода адреса на входы адреса накопителя 3, на вход 17 потенциал, переводящий выходы коммутатора 10 в отключенное состояние, на вход 15 - потенциал, разрешающий прохождение кода информации через коммутатор 5 на блок 9 и устанавливающий на выходе 27 блока 7 уровень О. На входы сумматора 24 поступают результаты свертки с выходов блоков 7, 8 и через сумматор 22 и злемент НЕ 27 с блока 9. Таким образом, считывание информации также сопровождается выдачей с выхода 20 контрольного разряда. Режим работы устройства, связанный с увеличением количества слов или адресной разрядности устройства, Дополнительный разряд адреса и его инверсию подают соответственно на входы выборки накопителей 1 и 2, входы 17 и на один из внешних входов блока 6, При подаче кода адреса на вход II и входы выборки 1 и 2 накопителей информационный код считывается с выбранного накопителя 1 или 2 и поступает на выход накопителя 3 к входы блоков 7 и 8, Контрольные разряды считываются с. накопителя 3 по адресу, поступающему через коммутатор 4, открытый сигналом со входа 1 6 и непосредственно со входа 11, Так как количество слоев в накопиТеле 3 меньше, чем в накопителях 1 И 2, то с его выхода считываются одновременно контрольные разряды для нескольких слов, хранимых в накопителях 1 и 2, Выбор соответствующего контрольного разряда производится оммутатором J О с помощью разрядов адреса, поступающих на его управляюие входы, при этом первьгй управляюий вход управляет выбором одной из групп информационных входов коммутатора 10, Сигнал с входа 17 управляет отключением выходов коммутатора 10 соответственно. Блоки 7 и 8 форируют признак исправности считывамой информации, который поступает а элемент И-ИЛИ-НЕ 28 блока 7 через элемент ИЛИ-НЕ 19 или 20, соответстующий выбранному накопителю. Часть разрядов кода адреса проходит через кок утатор 5, открытый для них сигналом со входа 15 и поступает-на вхо ды блока 10. Другая группа разрядов адреса сворачивается по модулю два в сумматоре 26 блока 6.и через элемент 27 проходит вместе с результатом свертки в блоке 6 на входы сумматора 22, При наличии внешнего контрольного разряда адреса, подаваемого на вход 19, на выходе сумматора 22 сформируется сумма по модулю два этого контрольного разряда и группы разрядов адреса (без дополнительного разряда адреса). Эта сумма, равная инверсии дополнительного разряда адреса, суммируется по модулю два с инверсией дополнительного разряда адреса, поступающей по группе внешних входов 4 блока 6, в сумматоре 24, Прямое значение дополнительного разряда, поступающее по группе внешних входов 3, суммируется в сумматоре 23 с прямым значением дополнительного разряда, поступающим с элемента 27, При отсут ствии ошибок в адресном тракте навыходах сумматоров 23 и 24 формируется О, поступающийна элемент И-ИПИ-НЕ 28, который формирует признак исправ ности информационных и адресных цепей. При отсутствии внешнего контрольного разряда его значение заносят в накопитель 3, С помощью разрядов адреса, присутствующих на управляющих входах информационного коммутатора 10, производится выбор как контрольного разряда кода информации, так и контрольного разряда кода адреса. Таким образом, проверяется информационный тракт и коммутатор 10 устройства. При работе с увеличенной адресной разрядностью, без контроля, в накопитель 3 заносят информационный код. Количество слов в устройстве уравнено с количеством слов в накопителях 1 и 2, Таким образом, при подаче код адреса с устройства считьшается информационное слово, количество разрядов которого увеличено за счет информационной емкости накопителя 3, При работе устройства в качестве модуля для построения ПЗУ различных информационных емкостей и структур его используют как депгафратор дополнительных разрядов адреса, для чего 1 5 . е на вход 17 подают потенциал, запрещающий прохождение группы разрядов адреса на накопитель 3, Накопитель 3 другого модуля используют как ПЗУ контрольных разрядов информационных кодов, Выходы накопителя 3 (дешифратора дополнительных разрядов адреса) соединяют с внешними входами блоков 6 обоих модулей. Работа ПЗУ происходит аналогично описанному выше режиму с контролем при увеличенной адресной разрядности и не требует дополнительного оборудования. При этом обеспечивается как контроль кодов адреса и информации, так и контроль дешифратора дополнительных разрядов адреса. Таким образом, предложенное устройство обеспечивает проверку информационного и адресного трактов при изменении информационной структуры, формирование контрольного разряда считываемых слов, что позволяет повысить полноту контроля и точность определения места неисправности при совместной работе с последующими каскадами обработки информации, В устройстве также достигается увеличение информационной емкости, Формула изобретения 1 , Постоянное запоминающее устройство с самоконтролем,содержащее основные и дополнительный накопители, основные и дополнительный блоки формирователей четности, блок контроля, входы первой группы которого соединены с входами выборки основных накопителей, а входы второй группы - с выходами основных и дополнительного блоков формирователей четности, выходы блока контроля являются контрольными выходами устройства, адресные входы основных и дополнительного накопителей являются адресными входами устройства, выходы основных и дополнительного накопителей являются информационными выходами устройства, входы основных блоков формирователей четности соединены с выходами соответствующих основньгх накопи-, телей, о тличающееся тем, что, с целью повьш1ения точности контроля и эффективной емкости, оно содер- . жит управляющий, информационный и адресный коммутаторы, причем информационные входы адресного коммутатора

71

соединены с адресными входами устрой ства, а выходы - с дополнительными адресными входами дополнительного на копителя, выходы которого соединены с информационными входами первой и второй групп информационного коммутатора и информационными входами пер вой группы управляющего коммутатора, информационные входы второй группы которого соединены с адресными входами устройства, а выходы-- с дополнительными входами дополнительного блока формирователей четности, вход управления управляющего коммутатора соединен с первым управляющим входом блока контроля, второй управляющий вход которого является входом маскирования устройства, четверт;ая группа входов блока контроля соединена с группой адресных входов устройства, один из которых соединен с первым управляющим входом информационного коммутатора, группа выходов которого соединена с дополнительными входами основных блоков формирователей четности, входы управления информационного, адресного и управляющего коммутаторов и блока контроля являются Заправляющими входами устройства,

2, Устройство по п., отличающееся тем, что блок контроля содержит группу элементов ИЛИ-НЕ, формирователи четности, элементы НЕ,

.740058

И-ИЛИ-НЕ, ИЛИ-НЕ, причем входы первой группы элементов ИЛИ-НЕ группы являются входами первой группы блока контроля,-а входы второй группы 5 элементов ИЛИ-НЕ группы и первый

вход первого формирователя четностивходами второй группы -блока контроля , первый вход элемента ИЛИ-НЕ является первым управляющим входом

10 блока контроля, а первый вход элемента И-ИЛИ-НЕ - вторым управляющим входом блока контроля, второй и третий входы элемента И-ИЛИ-НЕ соединены с выходами второго и третьего формироt5 вателей четности, а группа входов элементов И-ИЛИ-НЕ - с выходами элементов ИЛИ-НЕ группы, выходы элемента И-ИЛИ-НЕ и четвертого формирователя четности являются контрольными

20 выходами блока, вход четвертого формирователя четности соединен с входом второго формирователя четности и выходом элемента НЕ, вход которого соединен с входом третьего формирова5 теля четности и выходом первого формирователя четности, второй вход которого соединен с выходом элемента ИЛИ-НЕ, второй вход которого соеди- нен с выходом пятого формирователя

0 четности, группы входов втброго,

третьего, четвертого и пятого формирователей четности являются входами третьей и четвертой групп блока контроля ,

(Риз. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1424060A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

| Постоянное запоминающее устройство с контролем | 1988 |

|

SU1575240A1 |

| Запоминающее устройство с обнаружением наиболее вероятных ошибок | 1983 |

|

SU1149313A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1302329A1 |

Изобретение относится к запоминающим устройствам и может быть использовано при построении постоянных запоминающих устройств различных структур со встроенным контролем. Цель изобретения - повышение точности и эффективности устройства достигается введением управляющего, информационного и адресного коммутаторов, их связей с известными блоками устройства и схемным выполнением блока 7 контроля. Устройство содержит накопители 1,2 и 3, адресный коммутатор 4, управляющий коммутатор 5, блок 6 контроля, блоки 7,8 и 9 формирования четности, информационный коммутатор. 10, адрее гный вход II устройства, управляющие входы 12 - 17 устройства, вход 18 маскирования устройства, управляющий вход 19 устройства, выход 20 устройства. Блок -6 контроля содержит группу элементов ИЛИ-НЕ, сумматоры-элементы Н-ИЛИ-НЕ и инвертор. Введение коммутаторов и схемное выполнение блока контроля позволило осуществить проверку информационного и адресного трактов при изменении информационной структуры и повысить точность определения места неисправности. 1 з.п.ф-лы, 2 ил, ГЧЭ « 4;; О о ел вш.4 10

| Запоминающее устройство с автономным контролем | 1976 |

|

SU557419A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-11-30—Публикация

1984-06-05—Подача