(54) ЗАПОМИНАЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2116670C1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| Кодер | 1990 |

|

SU1783623A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1985 |

|

SU1337904A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1999 |

|

RU2149446C1 |

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 2013 |

|

RU2534955C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

| Устройство для контроля блоков памяти | 1979 |

|

SU790019A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ДЛЯ ОПРЕДЕЛЕНИЯ ИНФОРМАЦИОННЫХ СВОЙСТВ ТЕСТА | 1991 |

|

RU2068580C1 |

1

Изобретение относится к запоминающим устройствам.

Известно устройство, содержаще одноступенчатые сдвиговые регистры, выходы которых подключены :к входному регистру, счетчик, один из входов которого подключен к схеме управления, двухступенчатый регистр, дешифратор, группу схем .управления, входы которой подключены к выходам дешифратора, один из выходов - к другому входу счетчика, другие выходы - ко входам двухступенчатого регистра, выходы которого соединены с шинами сдвига и гсшения одноступенчатых регистров, выход счетчика подсоединен ко входу дешифратора

Недостатком этого устройства является низкая надежность его работы.

Наиболее близким техническим решением к предлагаемому является запоминающее устройство с самоконтролем, содержащее ряд сдвиговых накопителей, соединенных последовательно между собой, схему контроля,, подключенную ко входу и выходу каждого накопителя, и Олок управления t - Недостатком этого устройства является то, что при наличии отказов в сдвиговых накопителях значительная часть устройства не участвует в работе, что снижает надежность устройства.

Цель изобретения - повышение надежности устройства.

Поставленная цель достигается

0 тем, что в запоминающее устройство с самоконтролем, содержащее накопители, блок управления и блок обнаружения отказов, входы которого подключены к выходам, а одни из

5 выходов - ко входам кода отказа соответствующих накопителей, одни из выходов блока управления соединены соответственно с управляющими входами накопителей и блока об0наружения отказов, адресный вход первого накопителя подключен ко входу устройства, введены коммутаторы, регистры сдвига и дешифраторы - по .числу накопителей,

5 и формирователь кодовых сигналов сдвига, причем первый вход каждого коммутатора соединен с выходом одноименного накопителя, а выход каждого коммутатора кроме

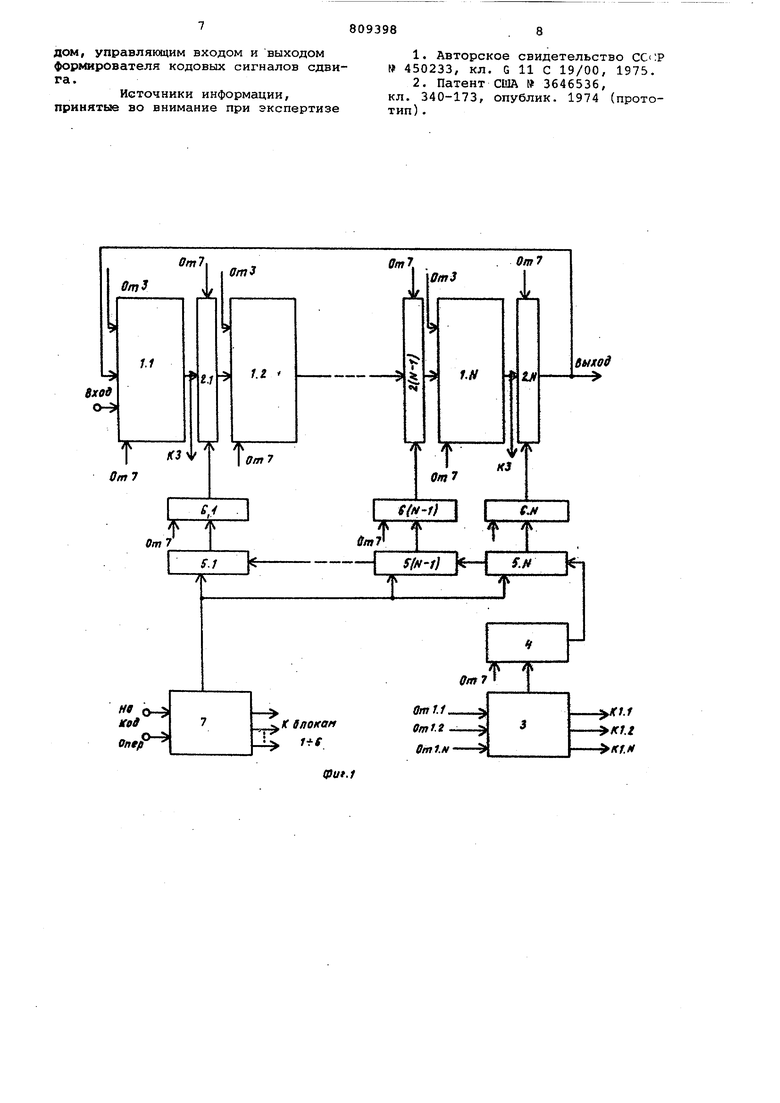

0 последнего - со входом последукяцего накопителя, выход последнего коммутатора подключен к выходной шине устройства и входу первого накопителя, вторые входы коммутаторов соединены с выходами одноименных дешифраторов, входы каждого из которых подключены к первому выходу одноименного регистра сдвига, первый вход каждог предыдущего регистра сдвига, кроме последнего, соединен со вторым выхо дом последующего регистра сдвига, первый вход последнего регистра сдв га подключен к выходу формирователя кодовых сигналов сдвига вход которого соединен с другим выходом блок обнаружения отказов, вторые входы регистров сдвига и управляющие вход коммутаторов, формирователя кодовых сигналов сдвига и дешифраторов подключены к другим выходам блока упра ления соответственно. При этом формирователь кодовых сигналов сдвига целесообразно выпол нить содержащим два регистра, вычитатель, три элемента И, два триггера и счетчик, причем выходы регис ров подключены соответственно к пер вому и второму входам вычитателя, первый выход которого соединен с пе выми входами первого и второго элементов И, выходы которых подключены соответственно ко входам первого триггера, единичный выход которого соединен со вторым входом второго элемента И,первым входом третьего элемента И и первым входом второго триггера, единичный выход которого подключен ко второму входу первого элемента И, выход третьего элемента И соединен с первым входом счетчика, вторые входы третьего элемента И и счетчика подключены ко второму выходу вычитателя, входы регистров вторые вход второго триггера и выхо вычитателя, третий вход вычитателя и выход счетчика соединены соответ ственно с входом, управляющим входом и выходом формирователя кодовых сигналов сдвига. На фиг. 1 изображена функциональ ная схема предлагаемого устройства на фиг. 2 - схема формирователя кодовых сигналов сдвига. Устройство содержит (фиг. 1) на копители 1.1-1.N, коммутаторы 2.1блок 3 обнарух ения отказов, формирователь 4 кодовых сигналов сдви га, регистры сдвига 5.1-5.N, дешифраторы 6.1-6.N и блок 7 управлени Входы блока 3 обнаружения отказ , подключены к выходам, а одни из выходов - к входам кода отказа соответствующих накопителей 1.1-1.N. Одни из выходов блока 7 управления соединены соответственно с управляющими входами накопителей 1.1-1. и блока 3 обнарухс-ения отказов. Адресный вход первого накопителя 1.1 подключен ко входу устройства. Первый вход каждого коммутатора 2.1-2.N соединен с выходом одноименного накопителя 1.1-1.N, а выход ка5кдого коммутатора 2..N, кроме последнего - с входом последующего накопителя 1.2-1.N. Выход последнего коммутатора 2.N подключен к выходной шине устройства и входу первого накопителя 1.1. Вторые входы коммутаторов 2.1-2.N соединены с выходами одноименных дешифраторов 6.1-6.N, входы каждого из которых подключены к первому выходу одноименного регистра сдвига 5.1-5.N. Первый вход каждого предыдущего регистра сдвига 5.1-5.N, кроме последнего, соединен со вторым выходом каждого последующего регистра сдвига 5.2-5.N. Первый вход последнего регистра сдвига 5.N подключен к выходу формирователя 4 кодовых сигна лов сдвига, вход которого соединен с другим выходом блока 3 обнаружения отказов. Вторые входы регистров сдвига 5.1-5.N, управляющие входы коммутаторов 2.1-2.N, формирователя 4 кодовых сигналов сдвига и дешифраторов 6.1-6.N подключены к другим выходам блока 7 управления соответственно. При этом формирователь 4 кодовых сигналов сдвига выполнен содержащим (фиг. 2) первый 4.1 и второй 4.2 регистры, вычитатель 4.3, первый 4.4 и второй 4.5 элементы И первый триггер 4.6, третий элемент 4.7 И, второй триггер 4.8 и счетчик 4.9. Выходы регистров 4.1 и 4.2 подключены соотв.етственно к первому и второму входс1М вычитателя 4.3, первый выход которого соединен с первыми входами первого 4.4 и второго 4.5 элементов И. Выходы элементов И 4.4 и 4.5 поключены соответственно к входам первого триггера 4.6, единичный выход которого соединен со вторым входом второго элемента 4.5 И, первым входом третьего элемента 4.7 И и первым входом второго триггера 4.8. Единичный выход второго триггера 4.8 подключен ко второму входу первого элемента 4.4 И. Выход третьего элемента 4.7 И соединен с первым; входом счетчика 4.9. Вторые входы третьего элемента 4.7 И и счетчика 4.9 подключены ко второму выходу вычитателя 4.3. Входы регистров 4.1 и 4.2, вторые вход второго триггера 4.8 и выход вычитателя 4.3, выход счетчика 4.9 и третий вход вычитателя 4.3 соединены соответственно со входом, управляющим входом и выходом формирователя 4 кодовых сиг-налов сдвига. Устройство работает следующим образом.

Перед началом работы проводится тестовый контроль, при котором выясняется, в каких разрядах накопителей 1.1-1.N произошли отказы. Блок 7 управления (фиг. 1) поочередно подключает входы и выходы накопителей 1.1-1.N к блоку 3 обнаружения отказов, который вырабатывает код отказа. В этом коде отказавшие разряды накопителей 1.1-1.N отмечаются единицами, работающие ряды - нулями. Код отказа поступа в формирователь 4 кодовых сигнало сдвига, который вырабатывает код сдвига информации с учетом отказа ших разрядов накопителей 1.1-1.N. Коды отказа накопителей 1.1-1. с блока 3 обнаружения отказов пос пают соответственно на регистры 4.1 и 4.2 (фиг. 2). Коды с обоих регистров поступают на вычитатель 4.3 и,после вычитания первого код из второго, знак резулйтата, опре деляющий направление сдвига, поступает в старший разряд регистра сдвига 5.N (фиг. 1). Содержимое вычитателя 4.3 сдвигается вправо и первая единица, поступившая на вход первого элемента 4.4 И, устанавливает первый триггер 4.6 в еди ничное состояние, открывая третий элемент 4.7 И, и тактовые импульсы поступают на счетчик 4.9. Втора единица, поступившая с вычитателя 4.3, через открытый второй элемент 4.5И устанавливает второй триггер 4.6в нулевое состояние и закрывает третий элемент 4.7 И. Затем значение счетчика 4.9 переписывает в регистр 5.N сдвига. Определяются коды сдвига для всех накопителей 1.1-1.N. С регистров сдвига 5.1-5. коды сдвига поступшот на соответствующие дешифраторы 6.1-6.N. Ком- мутаторы 2.1-2.N в соответствии с выходными сигналами дешифраторов 6.1-6.N переключают выходные и вхо ные шины накопителей 1.1-1.N таким образом, что отказавший разряд предьвдущего из накопителей 1.1-1.N подключается к отказавшему разряду последующего из накопителей 1.1-1.N. Технико-экономическое преимущество предлагаемого устройства заключается в том, что оно позволяет обнаруживать неработающие ячейки накопителей и пере страивать схему их соединения таки образом, что все единичные отказы в накопителях не влияют на работу запоминающего устройства, что повы ет его надежность. Формула изобретения 1. Запоминающее устройство с сам контролем, содержащее накопители, б управления и блок обнаружения отка

зов, входы которого подключены к выходам, а одни из выходов - ко входам кода отказа соответствующих накопителей, одни из выходов блока управления соединены соответственно с управляющими входами накопителей и блока обнаружения отказов, адресный вход первого накопителя подключен ко входу устройства, о тличающееся тем, что. с целью повышения надежности устройства, оно содержит коммутаторы, регистры сдвига и дешифраторы - по числу накопителей, и формирователь кодовых сигналов сдвига, причем первый вход каждого коммутатора соединен с выходом одноименного накопителя , а выход каждого коммутатора, кроме последнего, - со входом последующего накопителя, выход последнего коммутатора подключен к выходной шине устройства и входу первого накопителя, вторые входы коммутаторов соединены с выходами одноименных дешифраторов, входы каждого из которых подключены к первому выходу одноименного регистра сдвига, первый вход каждого регистра сдвига, кроме последнего, соединен со вторым выходом последующего регистра сдвига, первый вход последнего регистра сдвига подключен к выходу формирователя кодовых сигналов сдвига, вход которого соединен с другим выходом блока обнаружения отказов, вторые входы регистров сдвига и управлянждае входы коммутаторов, формирователя кодовых сигналов сдвига и дешифраторов подключены к другим выходам блока управления соответственно . 2. Устройство по п. 1, о т л и чающееся тем, что формирователь кодовых сигналов сдвига содержит два регистра, вычитатель, три элемента И, два триггера и счетчик, причем выходы регистров подключены соответственно к первому и второму входам вычитателя, первый выход которого соединен с первыми входами первого и второго элементов И, выходы которых подключены соответственно ко входам первого триггера, единичный выход которого соединен со вторым входом второго элемента И, первым входом третьего элемента И и первым входом второго триггера, единичный выход которого подключен ко второму входу первого элемента И/ вы од третьего элемента И соединен с ервым входом -счетчика, вторые входы ретьего элемента И и счетчика подлючены ко второму выходу вычитаеля, входы регистров, вторые вход торого триггера и выход вычитателя, ретий вход вычитателя и выход счетика соединены соответственно с вхоДОМ, управляющим входом и выходом формирователя кодовых сигналов сдвига.

Источники информации, принятые во внимание при экспертизе

кл. 340-173, опублик. 1974 (прототип) . ОтЗ KS.tf fut. 2 9т Т

Авторы

Даты

1981-02-28—Публикация

1979-05-18—Подача