1

Изобретение относится, к запоминающим устройствам.

Известно устройство для контроля блоков памяти, в котором информация, считанная из 3anoN:HHarom,ero блока, сравнивается с эталоном,.соответствующим адресу проверки Cl.

Однако в нем производится только контроль содержимого запрограммированного накопителя запоминающего блока.

Наиболее близким по технической сущности к предлагаемому является устройство для контроля однократно программируемых запоминающих блоков, со- держащее блок управления, выходы и входы которого соединены соответственно с входами и выходами первого и второго счетчиков, коммутаторы, управляющие входы которых соединены с - выходами блока управления, кодовые входы с выходами одного из счетчиков, а выходы коммутаторов подключены к входам блока сравнения 2j.

Однако это устройство не может быть использовано для контроля однократно программируемых блоков памяти, так как запись приводит к необратимому изменению элемента памяти,что сужает область применения устройства.

Цель изобретения - расширение области применения устройства за счет обеспечения возможности контроля од10нократно nporpaMNrnpysMbix блоков памяти.

Поставленная цель достигается тем, что в устройство для контроля блоков памяти, содержащее счетчики, коммутатор, схему сравнения и блок управления, одни из выходов которого ПОДК.ПЮчекы соответственно ко входам счетчиков, первому входу коммутатора и первому выходу устройства, одни из входов блока управления соединены с первыми выходами счетчиков и выходом схемы сравнения, первый вход которой соединен со входом устройства, вторые

входа счетчиков подключены соответственно ко второму и третьему входам коммутатора, выход которого соединен со вторым выходом устройства, введены триггер и регистр сдвига, причем входы триггера подключены к первым выходам счетчиков, выход триггера соединен с первым входом регистра сдвига, второй вход и первый выход которого подключены соответственно к другим выходу и входу блока управления, второй выход регистра сдвига соединен с третьим выходом устройс.ва и вторым входом схемы сравнения.

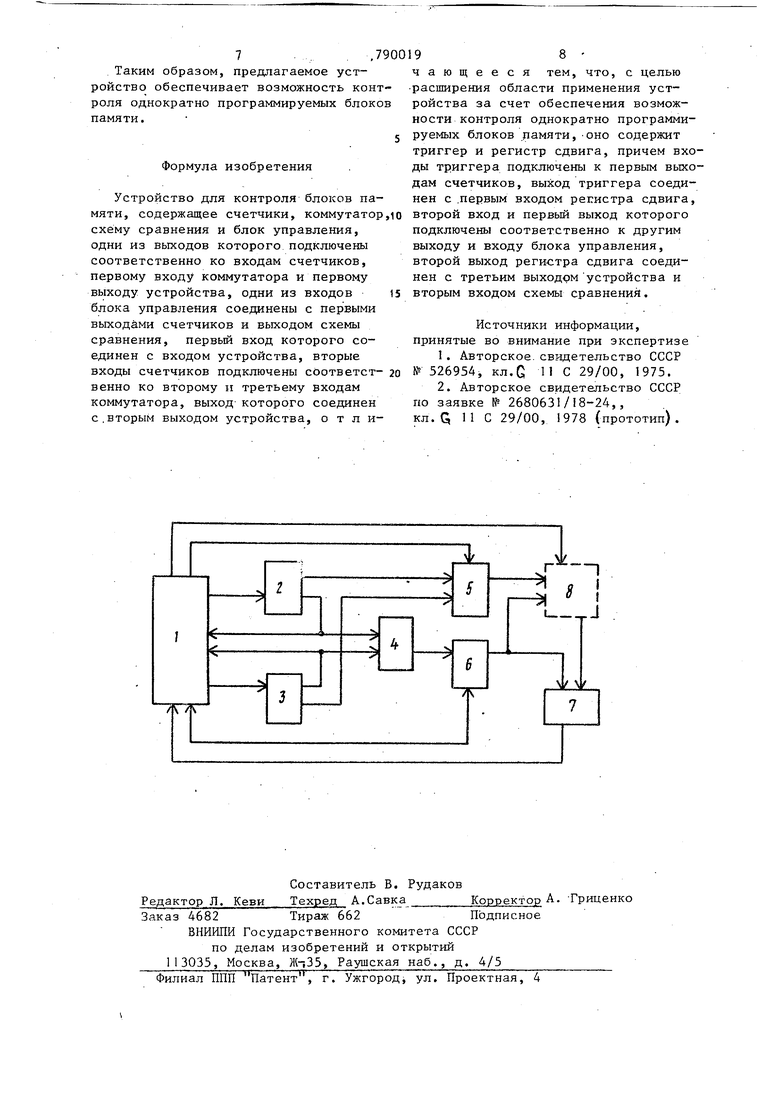

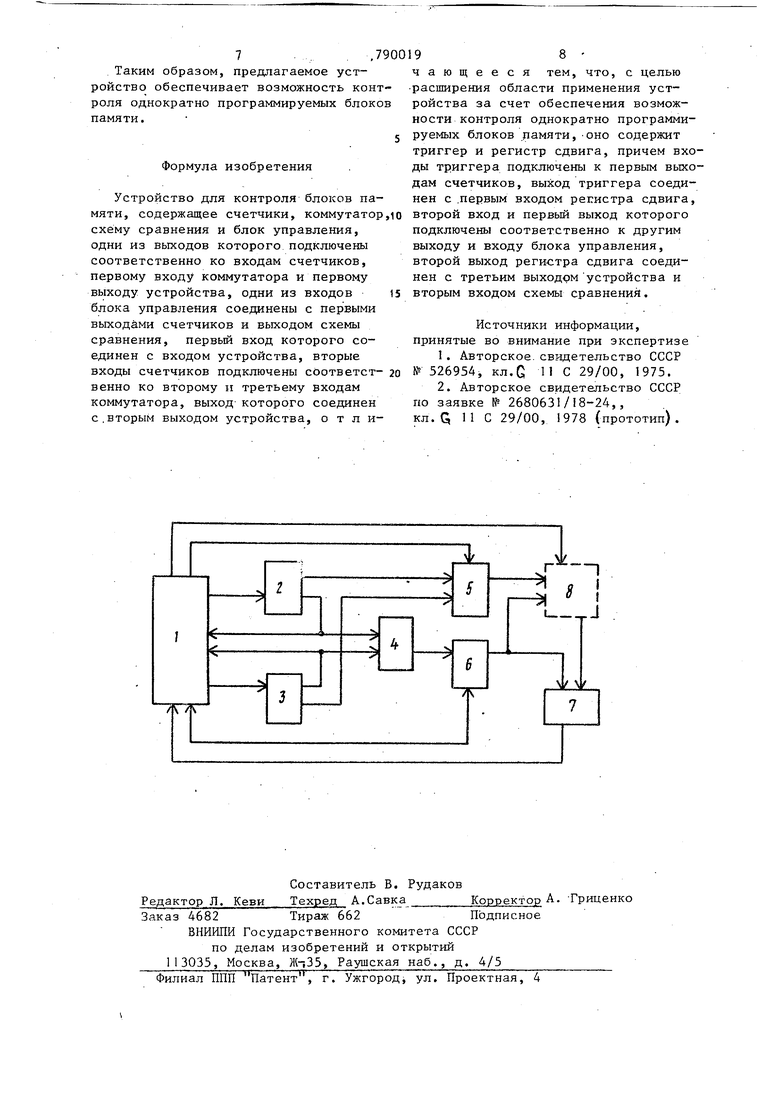

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит блок 1 управЬения, счетчики 2 и 3, служащие для формировйния кодов адресов, триггер 4 служащий для формирования контрольного разряда Кода эталона, коммута тор 5, регистр 6 сдвига, схему 7 сравнения. Вход и выходы устройства соединяются с выходом и входами контролируемого блока 8 памяти,

Одни из выходов блока 1 подключены соответственно ко входам счетчиков, первому входу коммутатора 5 и первому выходу устройства. Одни из входов блока 1 соединены с первыми выходами счетчиков 2 и 3 и выходом схемы 7 сравнения, первый вход которого соединен Со входом устройства Вторые входы счетчиков 2 и 3 подключены соответственно ко второму и третьему входам коммутатора 5, выход которого соединен со вторым выходом устройства. Входы триггера 4 подключены к первым выходам счетчиков 2 и 3. Выход триггера 4 соединен с первым входом регистра 6 сдвига, второй вход и первый выход которого подключены соответственно к другим выходу и входу блка 1 управления. Второй выход регистра 6 сдвига соединен с третьим выходом устройства и вторьм входом схемы 7 сравнения .

Допустим, что емкость контролируемого блока 8 памяти составляет

(N+1)x(n+1) бит,где N - емкость накопителя блока памяти, an- разрядность накопителя. Единицы добавляются за счет дополнительного контрольного 5 адреса (ЛК) и контрольного разряда (РК). Для полной функциональной проверки однократно программируемого блока памяти необходимо убедиться в работоспособности его составных ком10 понентов: адресных и разрядных формирователей, дешифраторов адреса, усилителей воспроизведения, формирователей сигналов управления, а также необходимо проектировать целостность 15 самих элементов памяти накопителя. Для контроля работоспособности компонентов блока памяти необходимо и достаточно убедиться в отсутствии замыкания и обрывов адресных и разрядных 20 цепей и шин накопителя, так как любой отказ вышеперечисленных компонентов можно интерпретировать как обрыв или замыкание шин. Для контроля разрядных цепей и шин необходимо последовательн 25 произвести запись в каждый разряд накопителя, включая ВК, по контрольному адресу АК, причем после каждой записи необходимо производить считывание и контроль по адресу АК, с целью проверки правильности записи в данный разряд и отсутствия записи в остальных разрядах. Далее, для контроля адресных цепей и шин, необходиЫо последовательно произвести запись 35 в контрольный разряд по каждому адрес накопителя (кроме АК), причем после каждой записи необходимо производить считывание и контроль информации по всем адресам, с целью проверки правильности записи по данному адресу и отсутствия записи по остальным адресам.

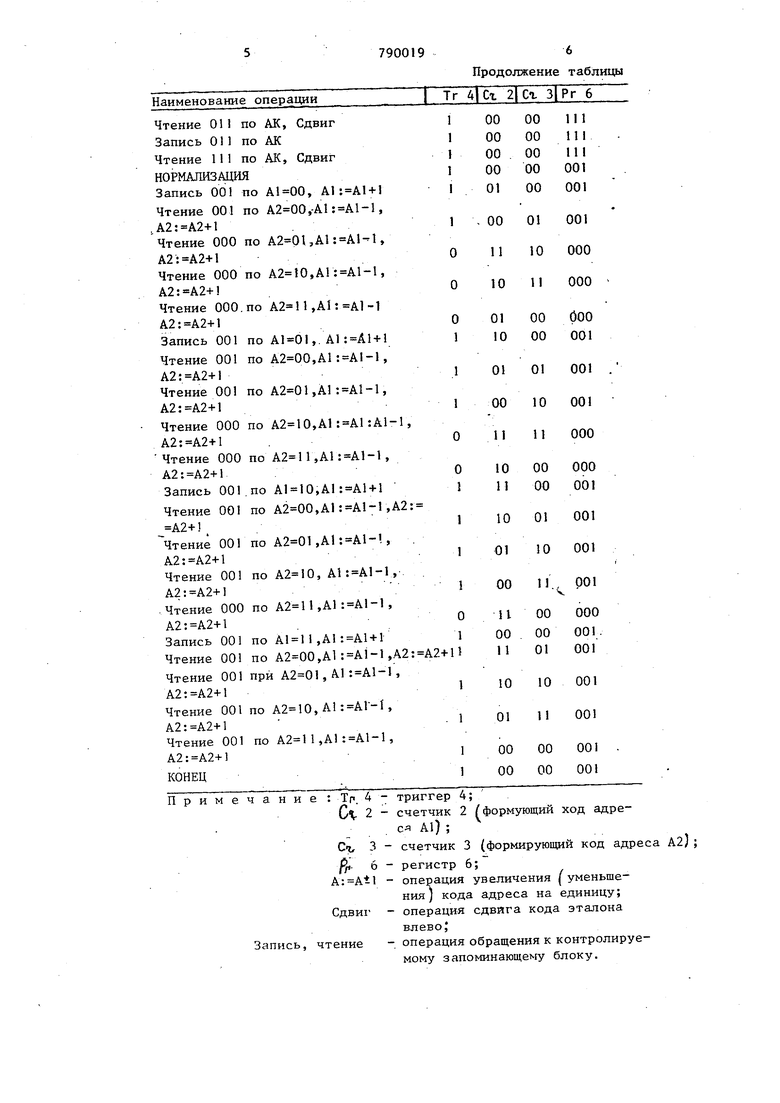

Устройство для контроля блоков памяти работает следующим образом. 45 Пусть емкость контролируемого блока (4+)х(2+0 т.е. N 4, П 2,- тогда последовательность операции по проверке блока памяти имеет вид, представленный в. таблице.

Продолжение таблицы

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1986 |

|

SU1363308A1 |

| Устройство для обработки элементов сканерных изображений | 1983 |

|

SU1134945A1 |

| Двухуровневое оперативное запоминающее устройство | 1982 |

|

SU1043742A1 |

| Устройство для анализа логических состояний | 1980 |

|

SU1096648A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1439681A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для контроля доменной памяти | 1982 |

|

SU1022216A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1105940A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1297115A1 |

Примечание : Тр, 4 С%- 2 Сг, 3 6 Сдвиг Запись, чтение триггер 4; счетчик 2 (формующий ход адреся AI) ; счетчик 3 (формирующий код адреса А2); регистр 6; операция увеличения уменьшения) кода адреса на единицу; операция сдвига кода эталона влево операция обращения к контролируемому запоминающему блоку.

Таким образом, предлагаемое устройство обеспечивает возможность контроля однократно программируемых блоков памяти.

Формула изобретения

Устройство для контроля блоков памяти, содержащее счетчики, коммутатор схему сравнения и блок управления, одни из выходов которого подключены соответственно ко входам счетчиков, первому входу коммутатора и первому выходу устройства, одни из входов блока управления соединены с первыми выходами счетчиков и выходом схемы сравнения, первый вход которого соединен с входом устройства, вторые входы счетчиков подключены соответственно ко второму и третьему входам коммутатора, выход которого соединен с,вторым выходом устройства, о т л ичающееся тем, что, с целью расширения области применения устройства за счет обеспечения возможности контроля однократно программируемых блоков памяти,-оно содержит триггер и регистр сдвига, причем входы триггера подключены к первым выходам счетчиков, выход триггера соединен с .первым входом регистра сдвига второй вход и первый выход которого подключены соответственно к другим выходу и входу блока управления, второй выход регистра сдвига соединен с третьим выходом устройства и вторым входом схемы сравнения.

Ис точ НИКИ информации, принятые во внимание при экспертизе

кл. Q 11 С 29/00, 1978 (прототип).

Авторы

Даты

1980-12-23—Публикация

1979-01-26—Подача