12

П

05 Ю СЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с каналом связи | 1988 |

|

SU1656544A1 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ПОВЫШЕННОЙ ТОЧНОСТИ (ВАРИАНТЫ) | 2008 |

|

RU2376625C1 |

| Устройство для программного управления технологическими процессами | 1989 |

|

SU1633377A1 |

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

| Устройство для сопряжения электронных вычислительных машин | 1980 |

|

SU962905A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Адаптивное телеметрическое устройство | 1987 |

|

SU1492361A1 |

1. УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ СИГНАЛОВ ИНФОРМАЦИОННО-ИЗМЕРИТЕЛЬНОЙ СИСТЕМЫ, содержащее дешифратор адреса канала, выход которого соединен с первым входом коммутатора, выход которого подключен к первому входу элемента сравнения, выход которого и выход программно-временного блока соединены соответственно с первым и вторым входами формирователя кода, выход которого соединен с входом регистра, выход регистра соединен с входом цифроаналогового преобразователя, выход которого подключен к второму входу элемента сравнения, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены блок управления, блок прерывания цикла и формирователь уровней округления, первый вход блока управления соединен с выходом дешифратора адреса канала, первый выход - с входом блока прерывания цикла, выход которого соединен с третьим входом формирователя кода, второй выход блока управления подключен к входу формирователя уровней округления, выход которого соединен с третьим входом элемента сравнения. /)

/J

10

1

Изобретениеотносится к измерительной технике и может быть использовано в информационно-измерительных системах, гибридных вычислительных комплексах, системах автоматики, регулирования и контроля.

Известен АЦП, содержащий устройство сравнения, ПКН, триггерный регистр, распределитель синхропотенциалов, дешифратор пределов, элементы И и ИЛИ, причем входы дешифратора пределов присоединены к старшим триггерам регистра, выходы дешифратора связаны с первыми входами элементов И схемы сдвига разрядов, вторые входы связаны с триггерами регистра, а входы элементов И объединены группами по числу пределов элементами ИЛИ 1.

Недостатком такого устройства является отсутствие возможности выполнения операции округления результатов преобразования.

Наиболее близким к изобретению техническим решением является устройство для преобразования сигналов, содержащее дешифратор адреса канала, выход которого соединен с первым входом коммутатора, выход которого подключен к первому входу элемента сравнения, выход которого и выход программно-временного блока соединены соответственно с первым и вторым входами формирователя кода, выход которого соединен с входом регистра, выход которого соединен с входом цифроаналогового преобразователя, выход которого подключен к вто рому входу элемента сравнения 2.

Недостатком известного устройства является отсутствие возможности выполнения операции округления результата преобразования.

Целью изобретения является повышение быстродействия устройства при округлении результата.

Поставленная цель достигается тем, что в устройство, содержащее дешифратор адреса канала, выход которого соединен с пергенератор, регистр сдвига, элементы И по числу округляемых разрядов и элемент ИЛИ, выход генератора соединен с входом регистра сдвига, выходы которого подключены к первым входам элементов И, выходы которых соединены с входами элемента ИЛИ, выход которого соединен с первым входом генератора, входом блока прерывания цикла является второй вход генератора и вторые входы элементов И, выходом - выход элемента ИЛИ.

вым входом коммутатора, выход которого подключен к первому входу элемента сравнения, выход которого и выход программновременного блока соедины соответственно с первым и вторым входами формирователя кода, выход которого соединен с входом регистра, выход регистра соединен с входом цифроаналогового преобразователя, выход которого подключен к второ.му входу элемента сравнения, введены блок управления, блок прерывания цикла и формирователь уровней округления, первый вход блока управления соединен с выходом дешифратора адреса канала, первый выход - с входом блока прерывания цикла, выход которого соединен с третьим входом фор.мирователя кода, второй выход блока управления подключен к входу формирователя уровней округления, выход которого соединен с третьим входом элемента сравнения.

Примем блок управления содержит элемент памяти, дешифратор и кодер, выходы элемента памяти подключены к входам дешифратора и входам кодера, первые и вторые входы элемента памяти являются соответственно первым и вторым входами блока управления, первым и вторым выходами которого являются соответственно выходы дешифратора и выходы кодера.

Кроме того, блок прерывания цикла содержит генератор, регистр сдвига, элементы И по числу округляемых разрядов и элемент ИЛИ, выход генератора соединен с входом регистра сдвига, выходы которого подключены к первым входам элементов И, выходы которых соединены с входами элемента ИЛИ, выход которого соединен с первым входом генератора, входом блока прерывания никла является второй вход генератора и вторые входы элементов И, выходом - выход элемента ИЛИ.

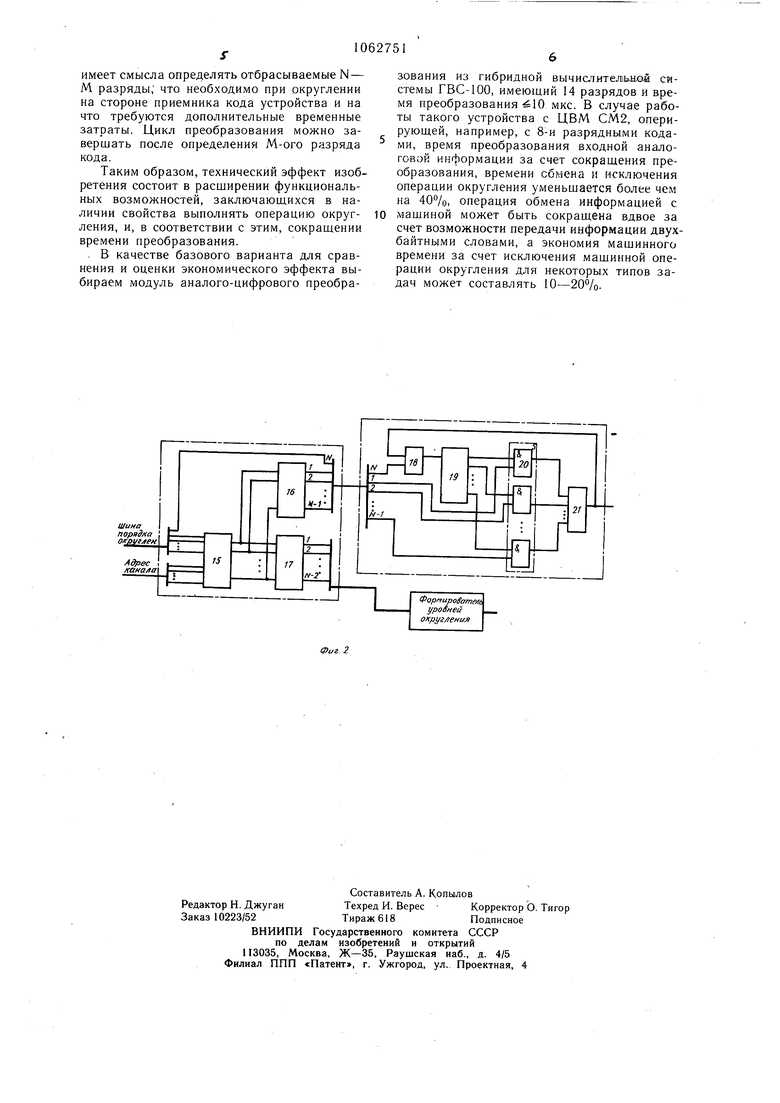

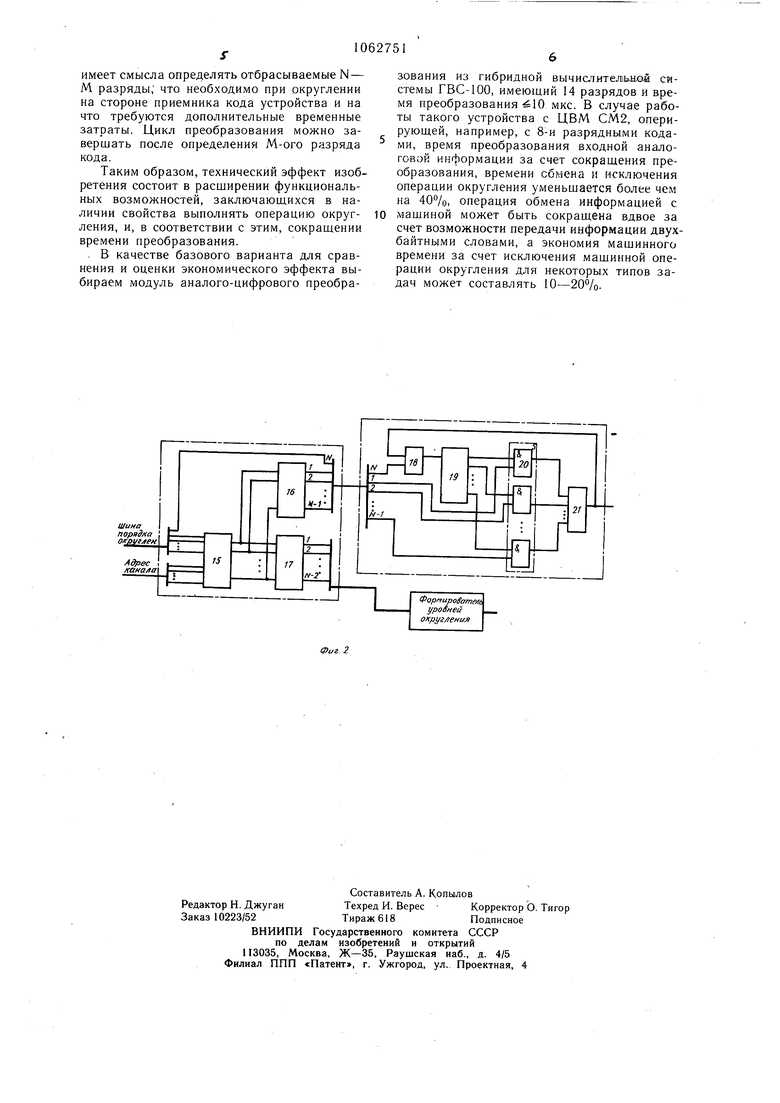

Устройство позволяет изменять разрядность выходного слова в зависимости от условия обмена между устройством и абонентом с округлением на передающей стороне, а также изменять длительность цикла преобразования в зависимости от разрядности выходного слова. На фиг. 1 представлена схема устройства; на фиг. 2 - схема блока управления режимом округления и блока прерывания цикла. Устройство содержит коммутатор 1, элемент сравнения 2, формирователь кода 3, блок 4 программно-временной, блок 5 прерывания цикла, регистр 6, цифроаналоговый преобразователь (ЦАП) 7, дешифратор 8 адреса канала, блок 9 управления, формирователь 10 уровней округления, шину 11 входных аналоговых сигналов, шину 12 адреса канала, шину 13 порядка округления и шину 14 результата преобразования. Блок 9 управления состоит из элемента памяти 15, шифратора 16 и кодера 17. Блок прерывания цикла состоит из генератора 18 импульсов, регистра 19 сдвига, элементов И 20 и элемента ИЛИ 21. Устройство работает, следующим образом. Аналоговые сигналы с шины 1 Г через коммутатор 1 поступают на вход элемента сравнения 2, которое совместно с узлами 3, 4, 6 и 7 реализует алгоритм аналого-цифрового преобразования, например алгоритм поразрядного кодирования. Блок 4 вырабатывает сигнал начала преобразования и поочередно включает и в соответствии -с выходным сигналом сравнивающего устройства выключает или оставляет включенным соответствующий разряд формируемого кода. Формируемый код через регистр 6 взводит поочередно, начиная со старшего, и при необходимости сбрасывает разряды ЦАП 7. По окончании цикла преобразования сформированный цифровой эквивалент входного аналогового сигнала из регистра 6 по шине 14 может быть передан абоненту. Схема построена таким образом, что поз воляет осуществлять квантования входного сигнала с точностью до 2 , где N - максимально возможное число двоичных разрядов в выходном коде преобразователя. С выхода регистра 6 двоичный цифровой эквивалент входного аналогового сигнала передается для дальнейшей обработки абоненту, которым в большинстве случаев является какое-либо цифровое вычислительное устройство или машина. Устройство это для принятия N-разрядных чисел от АЦП должно иметь входнбй регистр с числом разрядов N. Перед началом процесса преобразований по шине 13 в элемент памяти 15 блока 9 записывается информация о количестве разрядов выходного кода по каждому каналу измерения. В процессе преобразования по шине 12 в блок 9 поступает адрес канала, в соответствии с который из элемента памяти считывается количество разрядов кода, требуемое данным каналом, которое декодируется шифратором 16. В результате на один из элементов И блока 5, номер которого соответствует младшему разряду округленного кода, поступает разрешающий сигнал. В момент начала цикла преобразования включается генератор 18 тактовых импульсов, синхронных с управляющими импульсами устройства. Импульсы с генератора 18 поступают на вход регистра 19 и вызывают продвижение вправо единицы, записанной первоначально в младшем разряде. После того как единица появится в разряде, номер которого соответствует младшему разряду округленного кода, срабатывает соответствующий элемент И и сигнал появляется на выходе элемента ИЛИ 21. Этот сигнал выключает генератор 18; а также прерывает работу формирователя кода 3. Таким образом, процесс преобразования продолжается ровно столько тактов, сколько разрядов выходного кода требуется по данному каналу. Одновременно количество требуемых разрядов с кодера 17 блока 9 поступает в формирователь уровней округления 10, который формирует аналоговую добавку к измеряемой величине, равную половине младщего разряда округленного кода. Суммирование аналоговой добавки с измеряемой аналоговой величиной производится в -л icменте сравнения. Это эквивалентно смещению характеристики устройства на половину младшего разряда, т.е. в случае превышения величиной отбрасываемого остатка половины своего диапазона, величина эта в сумме с добавкой превышает значение младшего из остающихся разрядов. Выходной код, формирующийся в регистре 6 и поступающий на щину 14, в этом случае на один квант превышает код, полученный простым усечением. В случае, если величина отбрасываемого остатка меньше половины своего диапазона, в сумме с добавкой она не превышает значения младшего из остающихся разрядов. Выходной код устройства в этом случае совпадает с кодом, полученным при усечении. Величина же методической ошибки в обоих случаях -не превышает половины младщего разряда округленного кода. Не превышает половины младшего разряда и ошибка при кодировании с округлением в случае равенства суммы величин отбрасываемого остатка и добавки. В этом случае значение соответствующего разрядного коэффициента (О или 1) определяется случайным образом, согласно закону распределения значения выходного сигнала в зоне нечувствительности данного сравнивающего устройства. При округлении результата преобразования N-разрядного устройства до М разрядов описанным способом, очевидно, не имеет смысла определять отбрасываемые N- М разряды; что необходимо при округлении на стороне приемника кода устройства и на что требуются дополнительные временные затраты. Цикл преобразования можно завершать после определения М-ого разряда кода. Таким образом,технический эффект изобретения состоит в расширении функциональных возможностей, заключающихся в наличии свойства выполнять операцию округления, и, в соответствии с этим, сокращении времени преобразования. В качестве базового варианта для сравнения и оценки экономического эффекта выбираем модуль аналого-цифрового преобраГгзования из гибридной вычиа1ител1ь,ы.ой системы ГВС-100, имеющий 14 разрядов и время преобразования ёЮ мкс. В случае работы такого устройства с ЦВМ СМ2, оперирующей, например, с 8-и разрядными кодами, время преобразования входной аналоговой информации за счет сокращения преобразования, времени обмена н исключения операции округления уменьшается более чем на 40%, операция обмена информацией с мащиной может быть сокращена вдвое за счет возможности передачи информации двухбайтными словами, а экономия машинного времени за счет исключения мащинной операции округления для некоторых типов задач может составлять 10-20%.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ДВОИЧНЫЙ КОД | 0 |

|

SU190073A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Каган Б | |||

| М | |||

| и др | |||

| Системы связи УВМ с объектами управления в АСУ ТП | |||

| М., «Советское радио, 1978, с | |||

| Ручной прибор для загибания кромок листового металла | 1921 |

|

SU175A1 |

Авторы

Даты

1983-12-23—Публикация

1982-06-28—Подача