1

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для умножения частоты в диапазонах низких и инфранизких частот при обеспечении равенства скважностей выходных и входных импульсных сигналов.

Известен умножитель частоты 1, содержандий генератор опорной частоты, делитель частоты, элемент задержки, счетчик, регистр памяти и управляемый делитель частоты.

Известен также умножитель частоты 2, содержащий ген.ератор опорной частоты, управляемый делитель частоты, формирователь импульсов, блок управления, элементы И и ИЛИ, счетчики импульсов, группы элементов И и регистр памяти.

Наиболее близким по технической сущности к изобретению является умножитель частоты 3, содержащий делитель частоты, генератор опорной частоты, подключенный выходом к первым входам первого и второго элементов И, соединенных вторыми входами соответственно с прямым и инверсным выходами триггера, формирователь, вход которого подключен к входу импульсов умножаемой частоты, а выход - ко входу блока управления, соединенного первым выходом с управляющим входом первого регистра памяти, подключенного информационными входами к выходам разрядов первого счетчика, а выходами - к первым входам элементов И первой группы, выходы которых соединены с установочными входами- второго счетчика, подключенного счетным входом к выходу дополнительного генератора опорной частоты и к первому входу схемы фиксации нулей, соединенной выходом с выходом умножите-ия

частоты, а остальными входами - с выходами разрядов второго счетчика, причем первый вход триггера подключен к первому выходу блока управления, соединенного вторым выходом с входом обнуления первого счетчика, счет}1ый вход которого подключен к выходу первого элемента И, а второй вход триггера соединен через делитель частоты с выходом второго элемента И.

Такие устройства пе позволяют прп умножении частоты обеспечить равенство скважности входных и выходных нмпульсов, что ограничивает его функциональные возможности.

Целью изобретепия является расширение функц1 О11а.льных возможностем за счет обеспечения скважностг выходных импульсов, равной скважности входных импульсов. Эта цель достигается тем, что в умножг тель частоты, содержащий делитель частоты, генератор опорной частоты, нодключеннын выходом к первым входам первого и второго элементов И, соединенных вторымн входамн соответственно с нрямым н ннверсным выходами трнггера, формирователь, вход которого подключен к входу пмнульсов умножаемой частоты, а выход - к входу блока управлення, соеднненного нервым выходом с управляющим входом первого регистра памяти, подключенного информационными входами к выходам разрядов первого счетчика, а выходамп - к нервым входам элементов PI нервой группы, выходы которых соединены с установочными входами второго счетчика, введены вторые регистр иамятн и группа элементов И, третий счетчик и элемент ИЛИ, иодключеиный выходом ко входу обизления нервого счетчика, первым входом - к первому выходу б.тока унравления, а вторым входом - к второму выходу блока унравления и к управляющему входу второго регистра памяти, соеднненного информационными входами с выходами разрядов нервого счетчика, счетный вход которого нодключен через делитель частоты к выходу генератора опорной частоты. Выходы второго регистра памяти соединены с нервымн входами элементов И второй грунны, выходы которых нодключены к установочным входам третьего счетчика, а вторые входы - к инверсному выходу триггера, соединенного нрямым выходом с выходом умножителя частоты и с вторыми входами элементов И нервой грунны, а иервым и вторым входами - с выходами обиулепия соответственно третьего и второго счетчиков. Счетный вход второго счетчика нодключен к выходу нервого элемента И, а счетный вход третьего счетчика - к выходу второго элемента И.

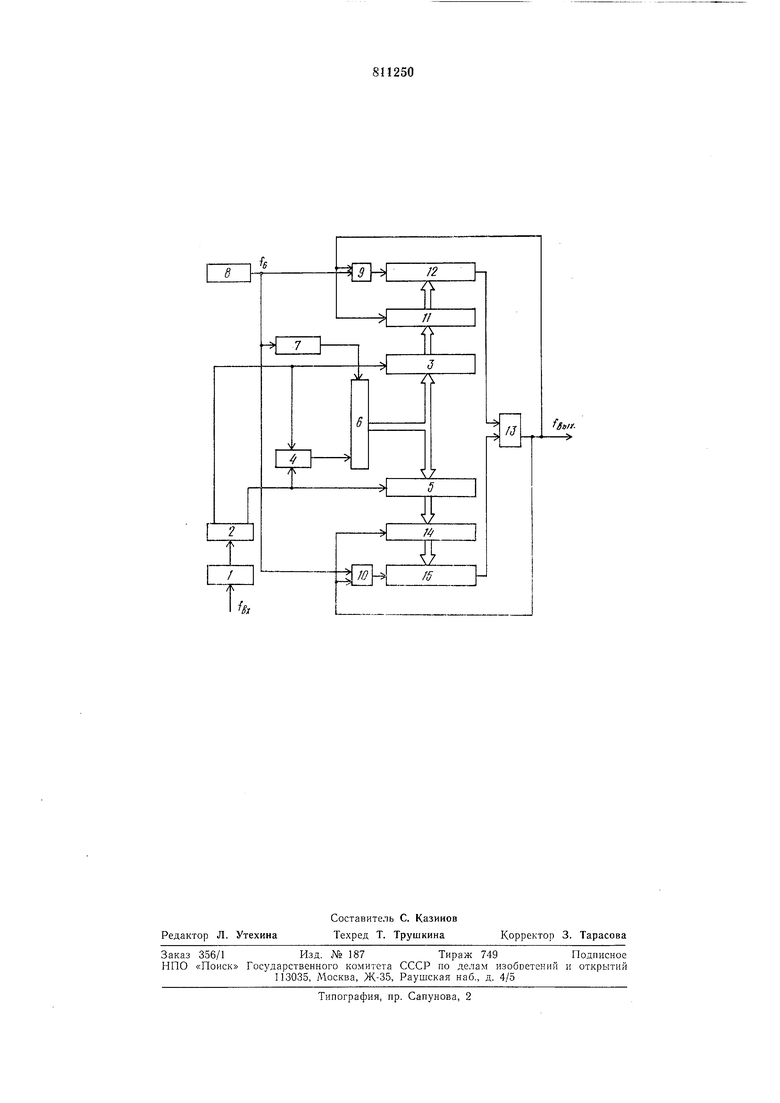

На чертеже дана структурная схема умножнтеля частоты.

Умножитель частоты еодержнт формирователь 1, вход которого нодключен к входу пмнульсов умножаемой частоты, а выход - к входу блока унравления 2. Блок унравления соединен иервым выходом с управляющим входом нервого регистра памяти 3 и с первым входом элемента ИЛИ 4, а вторым выходом - с унравляющим входом второго регистра памяти 5 и со вторым входом элемепта ИЛИ 4. Выход элемента ИЛИ 4 нодключен ко входу обнуления первого счетчика 6, работающего в режиме суммирования. Выходы разрядов счетчика 6 соединены с информационными входами регистров 3 и 5. Счетный вход счетчика 6 нодключеи через делитель частоты 7 к выходу генератора опорной частоты 8 и к иервым входам первого и второго элементов И 9 и 10. Выходы регистра 3 соедииены с первыми входами элементов И первой группы И, подключенных выходами к уетановочным входам второго счетчика 12, работающего в режиме вычитания импульсов. Счетчик 12 соединен счетным входом с выходом элемента И 9, а выходом обнуления - со вторым входом триггера

13, прямой выход которого нодключен к выходу умножителя частоты, второму входу элемента PI 9 и к вторым входам элементов И грунны 11. Выходы регистра 5 соединены с первыми входамн элементов И второй

груины 14, нодключенных выходами к установочным входам третьего счетчика 15, работающего в режиме вычитания имиульсов. Счетчик 15 соединен счетным входом с выходом эле.мента И 10, а выходом обнулеПИЯ - с третьнм входом триггера 13, инверсный выход которого подключен к второму входу элемента И 10 и к вторым входам элементов И грунны 14. Делитель частоты 7 может быть выполнен управляемым.

Умножитель частоты работает следующим образом.

Входной сигнал /вх, нернод новторения которого равен сумме длител ности нмнульеа ти Д-чительностн паузы тц, поступает на вход формирователя 1, который формирует из него нрямоугольные импульсы, ностунающне на вход блока управлення 2. На нервом выходе блока унравлення 2 импульсы коротко длительности

появляются в момепт начала паузы умножаемого сигнала, а на втором выходе - в момепт начала имиульса у.множаемого CIH нала. Блок управления 2 .может быть реализован, например, на двух одновибратоpax и инверторе, который нодключен входом к входу блока унравления и к входу нервого одновибратора, а выходом -- к входу другого одновибратора. Выходы одновибраторов соединены с соответствующими

выходамп блока управления. Одиовибраторы формируют выходиые импульсы короткой длительности нри иоложительн1:,1х иеренадах на их входах.

Имнульсы с В1)ходо.1 блока унравле1тя

2 через элемент ИЛИ 4 осуществ.1яют обиулеипе счетчика () перед иачалом очередного импульса или паузы входного сигнала. Генератор 8 пеирерывно заполняет счетчнк 6 импульсами опорной частоты /о, прошедшими через де.1итель частоты 7 с коэффнциеитом ./(. В течеиие длительности импульса входиого С1нл- ала иа счетчик 6 поступит количество импульсов Лл, равиое

Ивх- :

yV -д,

С иачалом иаузы входного сигиала импульс с первого выхода блока управлеиия 2 перепишет число N в регистр памяти 3 и затем сбросит счетчик 6 в пулевое состояпие. В течение иоследующей паузы входиого сигнала на счетчик 6 ноступит число имиульсов Л-п, равное

пвх-/о / С началом последнего импульса входной умножаемой частоты будет сформирован сигнал на втором выходе блока управления 2. Этот сигнал перепишет число NU в регистр памяти 5 и затем обнулит счетчик 6. 5 Далее описанный выше процесс счета и запоминания чисел , Лп повторяется в каждом периоде входного сигнала. Одновременно с этим ироцессом идет процесс формирования выходного сигнала О умножителя частоты. Пусть в рассматриваемый момент времени триггер 13 находится в единичном состоянии, тогда число переписывается из регистра 3 в счетчик 12 через группу элементов И П. Посколь-15 ку при этом элемент И 9 открыт, то имиульсы опорной частоты поступают на счетчик 12, уменьшая его содержимое. Когда счетчик 12 обнулится, импульс с выхода этого счетчика переведет триггер 13 в20 нулевое состояние. При этом элемент И 9 и группа элементов И 11 закроются, а откроются элемент И 10 и группа элементов И 14. Через открытую группу элементов И 14 число перепишется из регистра па-25 мяти 5 в счетчик 15, а имиульсы опорной частоты с выхода элемента И 10 начнут поступать на вход счетчика 15, уменьшая его содержимое. Когда счетчик 15 обнулится, имиульс с его выхода снова переключит30 триггер 13 в единичное состояние, при котором на его прямом выходе появится едипичный уровень, отпирающий элемент И 9 и группу элементов И 11, и далее процесс повторяется. Соответственно длительность35 выходного и паузы Тд импульсов Ти сигнала умножителя частоты (с ирямого выхода триггера 13) будут вых/с выхк а частота выходного сигнала будет равна у вых - А /вхПри этом скважность выходных импульсов, определяемая как отношение длитель- 45 иости периода выходного сигнала к длительности импульса выходного сигнала, будет равна скважности входных импульсов. Таким образом, рассмотренный умножитель нозволяет обеспечить равенство скваж- 50 иостей выходных и входных импульсов при умпол еиии частоты, что расширяет функциональные возмол ности умнол ;ителя, так как скважность входных импульсов нести доиолнительиую информацию о про- 55 Формула изобретения Умнол итель частоты, содержаший делитель частоты, геиератор опорной частоты. 40 60 подключенный выходом к первым входам первого и второго элементов И, соединенных вторыми входами соответственно с прямым и инверсным выходами триггера, формирователь, вход которого подключен к входу импульсов умножаемой частоты, а выходом - к входу блока управления, соедииенного первым выходом с управляюи;им входом первого регистра памяти, подключенного информационными входами к выходам разрядов первого счетчика, а выходами - к первым входам элементов И первой группы, выходы которых соединены с установочными входами второго счетчика, отл и ч а ю ид и и с я тем, что, с целью расширения функциональных возможностей за счет обеспечения скважности выходных импульсов, равной сквалсности входных импульсов, в умнол итель частоты дополнительно введены вторые регистр иамяти и груииа элементов И, третий счетчик и элемент ИЛИ, подключенный выходом к входу обнуления первого счетчика, первым входом - к первому выходу блока управления, а вторым входом - к второму выходу блока управления и к управляющему входу второго регистра памяти, соединенного информационными входами с выходами разрядов первого счетчика, счетный вход которого подключен через делитель частоты к выходу геператора опорной частоты, причем выходы второго регистра памяти соединеиы с первымп входами элементов И второй группы, выходы которых подключены к установочным входам третьего счетчика, а вторые входы - к инверсному выходу триггера, соединенного прямым выходом с выходом умножителя частоты и с вторыми входами элементов И первой группы, а первым и вторым входами - с выходами обнуления соответственно третьего и второго счетчиков, причем счетиый вход второго счетчика подключен к выходу первого элемента И, а счетный вход третьего счетчика - к выходу второго элемента И. Источники информации, принятые во внимание при эксиертизе 1.Авторское свидетельство СССР До 561185, кл. G 06 F 7/39, 1975. 2.Кириаиаки И. В. и др. Методы и устройства цифрового измерения низких иифранизких частот, Львов, «Высшая школа, 1975. 3. Авторское свидетельство СССР Ло 503238, кл. G 06 F 7/52, 1974 (иротоTim).

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1979 |

|

SU807281A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU1012431A1 |

| Умножитель частоты следования импульсов | 1984 |

|

SU1173537A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU991614A2 |

| Умножитель частоты | 1979 |

|

SU907781A1 |

| Умножитель частоты | 1983 |

|

SU1135004A1 |

| Многоканальный микропрограммный умножитель частоты | 1983 |

|

SU1144107A1 |

| Следящий умножитель частоты | 1979 |

|

SU851406A1 |

| Умножитель частоты следования импульсов | 1984 |

|

SU1188846A1 |

| Умножитель частоты | 1987 |

|

SU1448394A2 |

Авторы

Даты

1981-03-07—Публикация

1979-03-11—Подача