1

Известно запо.микающее устройство с автономным контролем, содержащее накопительные модули, регистр адреса, состоящий из регистра номера модуля, выход которого подсоединен ко входу дещифратора номера модуля и регистра номера ячейки, выход которого подсоединен ко входам регистров адреса накопительных модулей, выходной регистр, соединенный с блоком управления.

Однако известное устройство при отказе одной или нескольких ячеек накопительного модуля приходится ремонтировать. Кроме того, ремонт не гарантирует исправной работы устройства при повторном отказе того же модуля. В некоторых случаях (например, при использовании интегральной технологии) такой ремонт вообще невозможен, а коррекция разработанных в мащинном языке программ требует больших непроизводительных затрат рабочего времени.

Предлагаемое запоминающее устройство отличается от известного тем, что оно содержит блок коммутации модулей, один вход которого подключен к выходу дешифратора номера модуля, а выход - ко входам накопительных модулей; блок коррекции, выходы которого подсоединены соответственно к другому входу блока коммутации модулей и выходному регистру, а входы - к выходам введенных в устройство блоков схем «ИЛИ, входы

которых подключены к выходам регистров слов накопительных модулей. Это позволяет повысить надежность схемы.

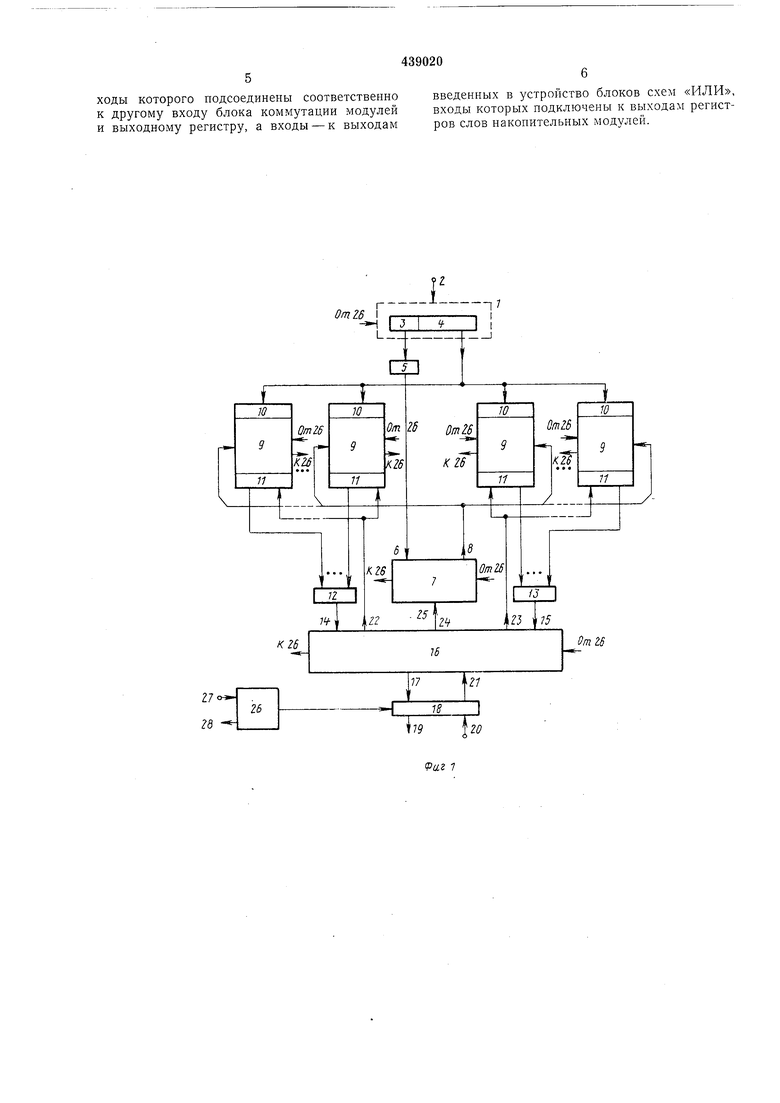

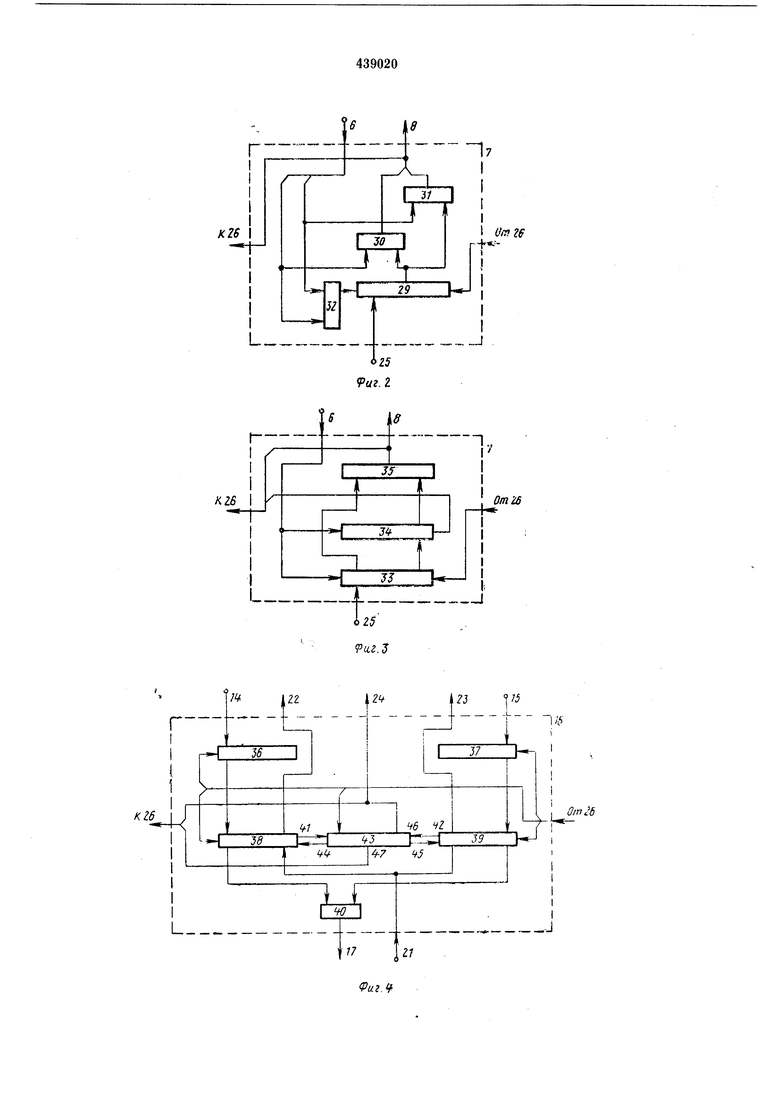

На фиг. 1 изображена блок-схема устройства; на фиг. 2 и 3 - варианты реализации блока коммутации модулей; на фиг. 4 - одна из возможных схем блока коррекции.

Регистр адреса 1 с информационным входом

2 состоит из регистра номера модуля 3 и регистра номера ячейки 4. Выход регистра 3 соединен со входом дешифратора номера модуля 5. Выход дешифратора 5 связан со входом 6 блока коммутации модулей 7. Каждая

из 2п шин 8 выхода блока 7 подключена к управляющему входу соответствующего накопительного модуля 9 (2п - число накопительных модулей). Выход регистра 4 соединен со входом каждого из регистров адреса 10. Выход каждого из регистров слова 11 накопительных модулей 9 через блок схем «ИЛИ 12 и блок схем «ИЛИ 13 связан соответственно со входами 14 и 15 блока коррекции 16. Выход 17 блока 16 соединен с выходным

регистром 18, имеющим выход 19 и вход 20. Регистр 18 подключен ко входу 21 блока 16. Выходы 22, 23 блока 16 связаны соответственно с регистрами слова 11. Выход 24 блока 16 подключен ко входу 25 блока 7. Регистры 1 и 18, блоки 7 и 16 и накопительные модули 9 соединены с блоком управления 26, который имеет вход 27 и выход 28.

Блок коммутации модулей 7 (фиг. 2) содержит регистр состояния модулей 29, имеющий л разрядов. Выход регистра 29 соединен с одним из входов блока схем «ИЛИ 30 и блока схем «ИЛИ 31. Выходные шины блоков 30 и 31 подключены ко входу 8 блока 7. С другими входами блоков 30, 32 связаны соответ-ственно шины входа 6 блока 7.

Регистр 29, а выходы блоков 30 и 31 связаны с блоком 26.

Другой вариант блока коммутации модулей 7 (фиг. 3) содержит регистр состояния модулей 33, имеющий 2п разрядов. Вход регистра 33 соединен со входом 25 блока 7. Один выход регистра 33 подключен ко входу коммутатора 34, один выход которого соединен с блоком 26, а другой - с одним из входов блока схем «ИЛИ 35. С другим входом блока 35 связан другой выход регистра 33. Выходные щины блока 35 соединены с выходом 8 блока 7.

Регистр 33, а также выход блока 35 связаны с блоком 26.

Блок коррекции 16 (фиг. 4) состоит из двух регистров слова 36 и 37, входы которых соединены соответственно со входами 14 и 15 блока 16, а выходы через блоки кодирования и декодирования 38 и 39 с блоком схем «ИЛИ 40. Выход 40 подключен к выходу 17 блока 16. Вход 21 блока 16 через блоки 38 и 39 соединен с выходами 22 и 23 блока 16. Выходы 41 блока 38 и 42 блока 39 подключены к схеме контроля 43, выходы которой 44 и 45 соединены соответственно со входами блоков 38 и 39. Выход 46 схемы 43 связан с выходом 24 блока 16 и блоком 26, выход 47 схемы 43 - с блоком 26.

Работает устройство следующим образом.

Адрес ячейки, к которой необходимо обратиться, записывается в регистр 1 по входу 2 (см. фиг. 1). Единичный сигнал, возникающий на выбранной в соответствии с содержимым регистра 3 выходной щине дешифратора 5, поступает в блок 7. Блок 7 задает один из двух возможных в устройстве режимов работы в зависимости от наличия или отсутствия отказов в ячейках накопительного модуля 9.

Рассмотрим первый режим (отсутствие отказов в ячейках накопительного модуля).

Блок 7 по единичному сигналу с дешифратора 5 подключает соответствующий накопительный модуль 9. Содержимое регистра 4 принимается на регистр адреса 10 подключенного модуля.

Информация в регистр 11 накопительного модуля 9 записывается с регистра 18 через блок 16 по его входу 21 и выходу 22 или 23.

При считывании содержимое регистра 11 через блок 12 либо блок 13 поступает в блок 16. Блок 16 определяет наличие отказов в ячейке подключенного накопительного модуля 9, и, если ячейка исправна, информационное слово поступает в регистр 18.

В случае обнаружения отказа в ячейке накопительного модуля 9 устройство переводится во второй режим работы, что происходит следующим образом. Сигнал «Отказ из блока 16 поступает в блок 7, где регистрируется неисправность /-того накопительного модуля 9 (, 2, ..., 2п), и в блок 26. По этому сигналу информация переводится, например, из 2п - /+1-ГО накопительного модуля, который должен стать дублирующим для /-того модуля, в другое запоминающее устройство (на чертеже не показано). В освободившиеся ячейки накопительного модуля заносится информация, записанная в одноименных ячейках отказавщего модуля.

Рассмотрим второй режим (наличие отказов в ячейках накопительного модуля).

Блок 7 по единичному сигналу с дещифратора 5 подключает /-тый и 2п-/+ 1-вый накопительные модули. Содержимое регистра 4 принимается на соответствующие регистры адреса 10.

При записи информационное слово поступает с регистра 18 в блок 16 и далее - в соответствующие регистры. При считывании содержимое этих регистров поступает соответствепно через блоки 12 и 13 в блок 16. Блок 16 корректирует считанную информацию, после чего информационное слово с выхода 17

блока 16 записывается в регистр 18. Если коррекция невозможна, из блока 16 в блок 26 поступает сигнал «неисправимая ощибка. В случае использования в устройстве первого варианта реализации блока 7 с п-разрядиым регистром состояния модулей (см. фиг. 2) обращение по старому адресу к ячейкам дублирующего накопительного модуля 9 запрещается программным путем, поскольку сам блок 7 такого запрета не обеспечивает. Если

же используется вариант реализации блока 7 с 2п-разрядным регистром состояния модулей (см. фиг. 3), то при обращении по старому адресу к ячейкам дублирующего накопительного модуля блок 7 запрещает его подключение и выдает в блок 26 сигнал «Повтор. Это значит, что хранившаяся в 2п-/+1-вом накопительном модуле информация переведена в другое запоминающее устройство.

Предмет изобретения

Запоминающее устройство с автономным контролем, содержащее накопительные модули, регистр адреса, состоящий из регистра номера модуля, выход которого подсоединен ко входу дещифратора номера модуля, и регистра номера ячейки, выход которого подсоединен ко входам регистров адреса накопительных модулей, выходной регистр, соединенный

с блоком управления, отличающееся тем, что, с целью повышения надежности, оно содержит блок коммутации модулей, один вход которого подключен к выходу дешифратора номера модуля, а выход - ко входам

накопительных модулей, блок коррекции, выходы которого подсоединены соответственно к другому входу блока коммутации модулей и выходному регистру, а входы - к выходам

введенных в устройство блоков схем «ИЛИ, входы которых подключены к выходам регистров слов накопительных модулей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с исправ-лЕНиЕМ ОшибОК | 1979 |

|

SU841059A1 |

| Резервированное многоканальное запоминающее устройство | 1980 |

|

SU942142A1 |

| Запоминающее устройство | 1973 |

|

SU475663A1 |

| Устройство для исправления ошибокВ блОКЕ пАМяТи | 1979 |

|

SU842976A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО„. -..,-•. ."р л С^аог^'-.---'^--:: '•^k^Vfi''-'- | 1973 |

|

SU375675A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU368647A1 |

| Запоминающее устройство | 1983 |

|

SU1104582A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1049968A1 |

| Многокоординатная система числового программного управления | 1972 |

|

SU448435A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU385319A1 |

К 26

I

Л 25

ЛS±.

.

1:

I

1 ttT 26 Jf-K Л.

Z5 9иг.1

П.

Oml

I

9аг.7

Авторы

Даты

1974-08-05—Публикация

1972-05-10—Подача