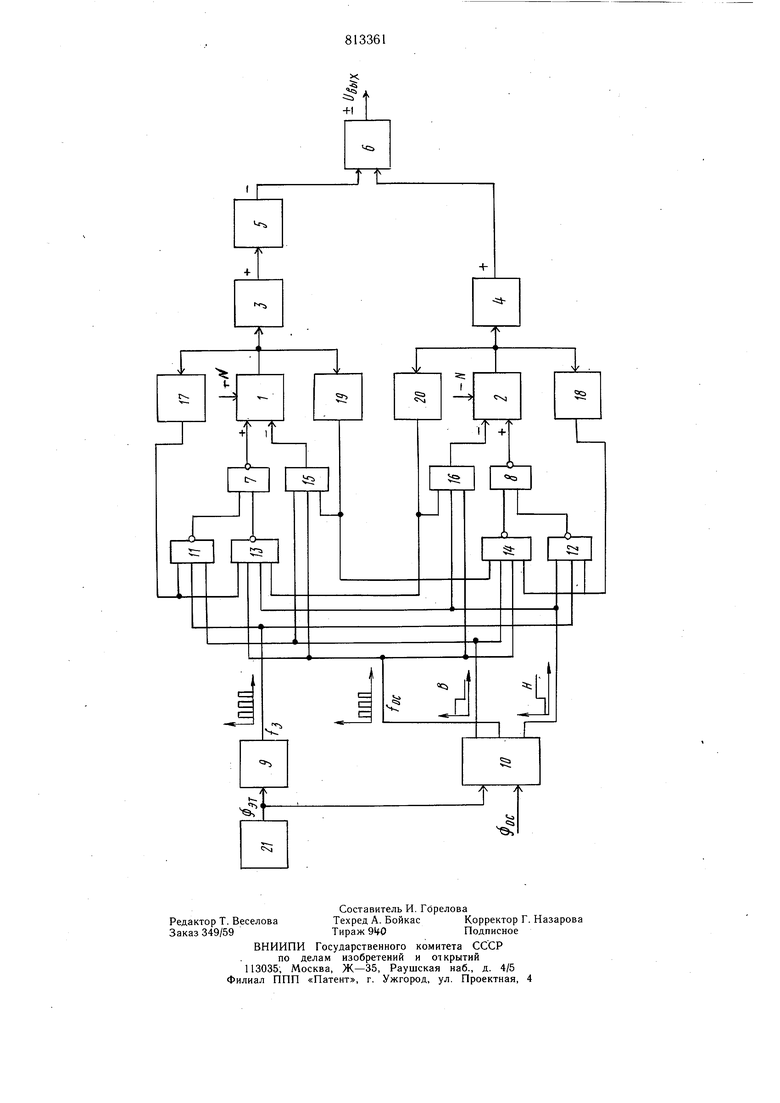

ходы которых подключены ко входам второго элемента ИЛИ-НЕ, выход первого блока контроля нулевого состояния счетчика соединен со входами первого элемента И и четвертого элемента И-НЕ, выход второго блока контроля нулевого состояния счетчика соединен со входами второго элемента И и третьего элемента И-НЕ, первый выход блока формирования частоты обратной связи и направления соединен со входами первого элемента И, первого и четвертого элементов И-НЕ, второй выход того же блока соединен со входами второго элемента И, второго и третьего элементов И-НЕ, третий выход того же блока подключен ко входам первого и второго -элементов И, третьего и четвертого элементов И-НЕ, выходы первого и второго элементов И соединены со входами вычитания соответственно первого и второго реверсивных счетчиков. На чертеже показана функциональная блок-схема реверсивного цифроаналогового преобразователя. Интегратор-преобразователь содержит первый 1 и второй 2 реверсивные счетчики, соединенные с цифроаналоговыми преобразователями 3 и 4, выходы которых, первый через инвертор 5, а второй непосредственно, подключены к сумматору 6, а шины «сложение - к выходам элементов ИЛИ-НЕ 7 и 8, блок 9 формирования частоты задания, блок 10 формирования частоты обратной связи и направления, четыре элемента ИНЕ 11 - 14 и два элемента И 15 и 16, выходы которых подсоединены к шинам «вычитание счетчиков 1 и 2, а входы - к блоку 10 формирования частоты обратной связи и направления, первые управляюш,ие входы первого и второго элементов И-НЕ 11 и 12 подсоединены к блоку 9 формирования частоты задания, их вторые входы и вторые входы элементов И-НЕ 13 и 14 - к первому и второму выходам блока 10 формирования частоты обратной связи и направления, первые входы третьего и четвертого элементов И-НЕ 13 и 14 подсоединены к третьему выходу этого же блока, причем выходы треть его, второго и четвертого элементов И-НЕ 11 и 13, 14 и 12 попарно подключены к входам первого и второго элементов ИЛИ-НЕ 7 и 8. Между входами элементов И-НЕ 11 и 13 и соответственно элементов И-НЕ 11 и 12 и выходами счетчиков 1 и 2 включены блоки 17 и 18 контроля переполнения счетчика, а между выходом счетчика 1 и входом элемента И-НЕ 14 и между счетчиком 2 и входом элемента И-НЕ 13 включены соответственно блоки 19 и 20 контроля нулевого положения счетчика. Устройство содержит также генератор 21 импульсов, подключенный ко входам блока 9 формирования частоты задания и блока 10 обратной связи и направления. Устройство содержит два канала. Первый канал включает в себя два элемента И-НЕ 11 и 13, по одному элементу И и ИЛИ-НЕ (15 и 7 соответственно). первый счетчик 1, первый цифроаналоговый преобразователь 3, инвертор 5 и блоки контроля переполнения и нулевого состояния счетчика 1 (17 и 19 соответственно); второй канал содержит два элемента И-НЕ 12 и 14, по одному элементу И и ИЛИ-НЕ (16 и 8 соответственно), второй счетчик 2, второй цифроаналоговый преобразователь 4 и втоые блоки контроля переполнения и нулевого положения счетчика 2 (18 и 20 соответственно). Сумматор 6, блок 10 формирования частоты обратной связи и направления, блок 9 формирования частоты задания и генератор 21 импульсов являются общими для обоих каналов. При опережающем фазовом сдвиге между сигналами задания и обратной связи (ipXl) суммирующий вход счетчиков 1 или 2 в зависимости от направления подключен к блоку 9 формирования частоты задания, а вычитающий вход счетчиков 1 или 2 - к блоку 10 формирования частоты обратной связи и направления. При отстающем фазовом сдвиге («f)0) и нулевом состоянии обоих счетчиков блок 10 формирования частоты обратной связи и направления переключается на суммирующий вход противоположного счетчика. При этом выходное напряжение интегратора-преобразователя меняет знак. Устройство работает следующим образом. Перед началом работы производится обнуление счетчиков 1 и 2. Импульсы частоты задания (ли обратной связи foe. отсутствуют, на выходе сумматора 6 - нулевой сигнал. После предварительного выбора направления работы, например вперед, на первом выходе блока 10 формирования обратной связи и направления появится сигнал логической «1, а на его втором выходе логического «О. Блок 9 формирования частоты задания через последовательно включенные элементы 11 и 7 подключается на шину «суммирование счетчика 1. Первый импульс в счетчике 1 преобразуется цифроаналоговым преобразователем 3 и на выходе сумматора 6 появляется сигнал Uftj О, что через внешние устройства (усилитель мощности, двигатель, датчик импульсный) вызывает появление импульсов частотой fot на третьем выходе блока 10 формирования обратной связи и направления, которые проходят на шину «вычитание счетчика 1 через элемент И 15. Импульсы ij и lot с целью неодновременного попадания их на входы счетчика 1 синхронизированы прямой и инверсной последовательностью эталонной частоты f соответственно. В счетчике 1 появляется число, равное разности частот - fee, а на выходе сумматора 6 аналоговый сигнал + UAioc Второй канал Интегратора-преобразователя при этом закрыт, что .обеспечивается логическим «О по входам элемента И 16 и элемента И-НЕ 12 со второго выхода блока 10 формирования обратной связи и направления и по

входу элемента И-НЕ 14 с выхода блока 22. Счетчик 2 находится в нулевом состоянии и на выходе преобразователя 4 напряжение отсутствует.

При выборе направления работы «назад (Н) из исходного состояния устройства сигналом логической «1 со второго выхода блока 10 формирования частоты обратной связи и направления, открывается второй канал интегратора-преобразователя, импульсы частотой f через элемент И-НЕ 12

поступают на шину «суммирование второго счетчика 2 и на выходе сумматора 6 появляется сигнал (- ). Это вызывает появление импульсов частотой foe, которые через элемент И 16 поступают на шину «вычитание счетчика 2. В последнем выделяется интегральная составляющая от частот U-и foj. Число счетчика 2 преобразуется цифроаналоговь1м преобразователем 4, и на выходе сумматора 6 появляется напряжение - U/иж- При превышении частоты импульсов 1л над частотой импульсов foe. или наоборот, напряжение на выходе сумматора 6 и,испо абсолютной величине соответственно возрастает или убывает. В случае прекращения подачи f, например при работе «вперед, импульсами частоты foe содержимое счетчика 1 уменьшается до О, блок 19 контроля нулевого положения счетчика через элемент И 15 заблокирует прохождение импульсов частоты на шину «вычитание счетчика 1, а по входу элемента И-НЕ 14 дается разрешение на прохождение импульсов частоты на шину «суммирование счетчика 2 второго канала, в результате этого на выходе сумматора 6 напряжение А«х изменяет знак с ( + ) на (-), и если внешней схемой не прекращается подача импульсов частотой или не изменится направление работы на обратное, то переполнение счетчика 2 через второй блок 18 контроля переполнения счетчика 2 накладывает запрет на прохождение импульсов частотой foe на его шину «суммирование, на выходе сумматора 6 будет сохраняться максимальное значение выходного напряжения Vff со знаком минус.

Предлагаемый интегратор-преобразователь применяется в приводах с цифроаналоговым управлением для выделения интегральной составляющей импульсных последовательностей h и . В режиме позиционирования управление приводом производится записью определенного числа импульсов ± N, пропорционального углу поворота вала двигателя или величине перемещения привода в счетчики 1 или 2, в зависимости от направления перемещения. Описанное выполнение логической схемы управления интегратора-преобразователя, на базе потенциальных элементов позволяет повысить точность работы устройства и упростить

его, обеспечить в приводе диапазон регулирования до 1 :2- 10 (L 1 Гц -2- 10 кГц).

Формула изобретения

Реверсивный цифроаналоговый интегратор-преобразователь, содержащий первый и второй реверсивные счетчики, выход каждого из которых соединен со входами соответствующего цифроаналогового преобразователя, блока контроля переполнения и блока контроля нулевого состояния счетчика, выход первого цифроаналогового преобразователя через инвертор соединен со входом сумматора, ко второму входу которого подключен выход второго цифроаналогового

преобразователя, генератор импульсов, выход которого соединен со входами блока формирования частоты задания и блока формирования частоты обратной связи и направления, первый и второй элементы ИЛИ-НЕ, выходы которых подключены ко

входам сложения соответственно первого и второго реверсивных счетчиков, элементы И и И-НЕ, отличающийся тем, что, с целью повыщения точности преобразования, выход блока формирования частоты задания соединен со входами первого и второго элементов И-НЕ, выход первого блока контроля переполнения соединен со входами первого и третьего элементов И-НЕ, выходы которых подключены ко входам первого элемента ИЛИ-НЕ, выход второго блока контроля

переполнения соединен со входами второго и четвертого элементов И-НЕ, выходы которых подключены ко входам второго элемента ИЛИ-НЕ, выход первого блока контроля нулевого состояния счетчика соединен со входами первого элемента И и четвертого

элемента И-НЕ, выход второго блока контроля нулевого состояния счетчика соединен со входами второго элемента И и третьего элемента И-НЕ, первый выход блока формирования частоты обратной связи и направления соединен со входами первого элемента И, первого и четвертого элементов И-НЕ, второй выход того же блока соединен со входами второго элемента И, второго и третьего элементов И-НЕ, третий выход того же блока подключен ко входам первого и вгорого элементов И, третьего и четвертого элементов И-НЕ, выходы первого и второго элементов И соединены со входами вычитания соответственно первого и второго реверсивных счетчиков.

Источники информации,

принятые во внимание при экспертизе

1. Слежановский О. В. и др. Устройства унифицированной блочной системы регулирования дискретного типа. М., «Энергия, 1975, с. 160.

2. Богорад Г. 3. и др. Цифровые регуляторы и измерители скорости. М., «Энергия, 1967, с. 97, 104-107 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный цифро-аналоговый интегратор-преобразователь | 1984 |

|

SU1247833A1 |

| Реверсивный цифровой интегратор | 1984 |

|

SU1238030A1 |

| Устройство для стабилизации частоты вращения электродвигателя | 1990 |

|

SU1707723A1 |

| Вычислительное устройство для определения соотношений между частотными сигналами | 1977 |

|

SU748426A2 |

| Фазовый дискриминатор | 1978 |

|

SU809482A1 |

| УСТРОЙСТВО ДЛЯ ОПЕРАТИВНОГО КОНТРОЛЯ СУММАРНОЙ МОЩНОСТИ НАГРУЗКИ ГРУППЫ ЭНЕРГОПОТРЕБИТЕЛЕЙ | 1997 |

|

RU2130191C1 |

| Устройство для контроля метрологических характеристик средств измерений | 1982 |

|

SU1117592A1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2009 |

|

RU2433528C2 |

| Устройство для измерения времени установления выходного напряжения цифроаналоговых преобразователей | 1986 |

|

SU1332530A1 |

| ЦЕЗИЕВЫЙ СТАНДАРТ ЧАСТОТЫ | 1994 |

|

RU2076411C1 |

Авторы

Даты

1981-03-15—Публикация

1977-12-26—Подача