1

Изобретение относится к автоматике, в частности к программному управлению технологическим оборудованием.

Известно устройство для программной реализации переключательных схем, содержащее матрицу коммутирующих элементов, блок памяти и блок уцравления 1.

Недостатком его является невозможность вычисления скобочных форм булевых функций.

Наиболее близким к предлагаемому является устройство для программной реализации переключательных схем, содержащее триггер, триггер результата, элемент И, элемент ИЛИ, первый и второй узел инвертирования 2.

Недостатком его является невозможность реализации скобочных форм.

Цель изобретения - расщирение функциональных возможностей за счет реализации скобочных форм.

Поставленная цель достигается тем, что в устройство введены блок проверки на нечетность, ячейки памяти, распределитель и блок подсчета числа ответвлений диаграммы, причем первые входы блока проверки

на нечетность, ячейки памяти и распределителя объединены между собой и являются управляющим входом устройства, второй вход блока проверки на нечетность является входом аргумента, а выход соединен с первым входом триггера и вторым входом ячейки памяти, выход которого соединен со вторым входом распределителя, третий вход которого подключен к выходу ячейки памяти, а выходы распределителя соединены с входами блока подсчета числа ответвлений

0 диаграммы, выход которого соединен со вторым входом триггера.

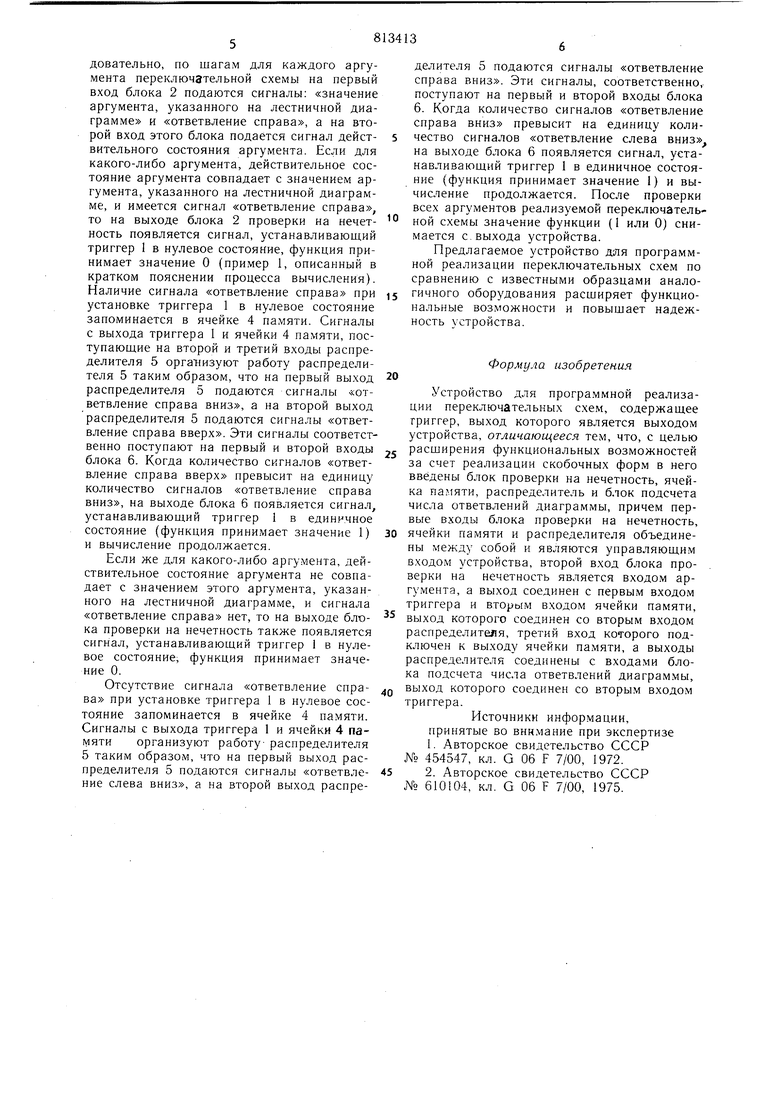

На фиг. 1 приведена схема устройства;

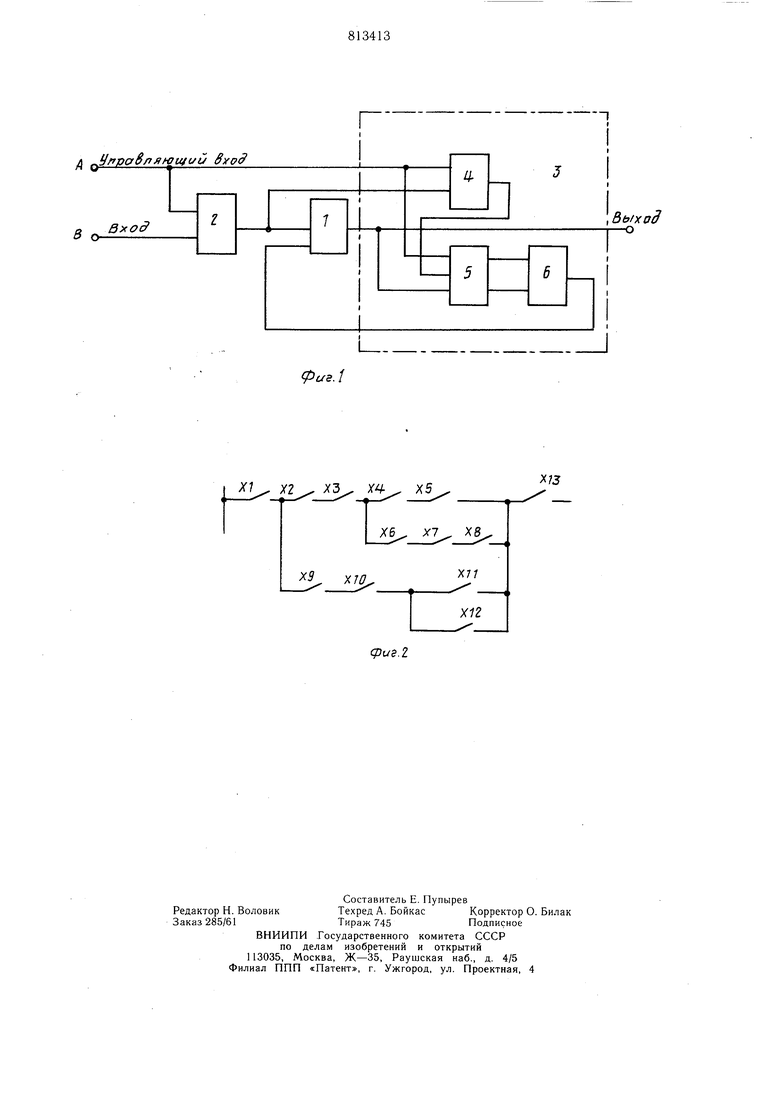

на фиг. 2 - пример лестничной диаграммы.

Устройство содержит триггер 1, блок 2

проверки на нечетность, блок 3 определения

5 конфигурации диаграммы, включающий ячейку 4 памяти, распределитель 5, блок 6 подсчета числа ответвлений диаграммы.

На первый вход блока проверки на нечетность через управляющий вход устройства подаются сигналы: «значение аргумента, указанное на лестничной диаграмме и «ответвление справа вниз. На первый вход ячейки 3-1 памяти подается сигнал «ответвление справа вниз, а на первый вход распределителя 3-2 подаются сигналы: «ответвление слева вниз, «ответвление справа вниз и «ответвление справа вверх. Блок 6 подсчета числа ответвлений диаграммы может, например состоять из двоичного реверсивного счетчика и дешифратора. Двоичный реверсивный счетчик имеет в.ход «сложение, вход «вычитание и вход установки нуля, выходы двоичного реверсивного счетчика соединены со входами депшфратора. При этом первы.м входом блока 3-3 нужно принять вход «вычитание двоичного реверсивного счетчика, вторым входом блока 3--3 нужно принять вход «сложение двоичного реверсивного счетчика, а выходом блока 3-3 будет выход дешифратора. Устройство работает следующи.м образом. В качестве при.мера для пояснения процееса вычисления используется переключательная схема, изображенная в виде лестничной диаграммы (фиг. 2). Для любой перек.лючательной схемы вычисле1П1е ведется в следующем порядке: вычис.;|е1П1е начинается с аргу.мента, расноложе1п-юго в верхней левой части схемы (для схе.мы на (риг. 2 это аргу.мент XI). Затем проверяютс5 последовательно все аргументы, расположенные на этой же ступеьп лестничной диа1ра.1мы, до ближайшего ответв.лепия от аргумента справа вниз. При наличии Огбетвления справа вниз опускаемся на с.ледуюплую ступепь лестничной диагра.м.мы вниз и продолжаем Бычис; ение этой ступени, начиная с крайнего левого аргумента и т. д. После проверки аргумента, имеющего только ответвление справа вверх, подпимаемся на верхнюю ступеньку .лестничной диагра.1мы н продолжаем вычисление в то.м же порядке как описано Bbinje. На фиг. 2 для иллюстрации все аргу.менты пронумерованы в порядке вычисления. На фпг. 2 ответвления «справа вниз обозначены стрелками справа от аргументов Х5, Х8, XII; ответвления «справа вверх обозначены стрелками справа от аргументов Х8, XII, Х12. Д,ля определения конфигурации лестничной диаграм.хп прн вычислении исиользуются также ответвления «слева вниз. отвств.ления па фиг. 2 обозначены стрелками с.лева от аргументов Х2, Х4, .XII. В начале вычисле1шя значение функции устапавливается равное i. В процессе вычисления функция может при.ни-мать зпачение О в двух случая.х . Пример . Функция прини.мает значение «О при проверке аргу.мента, имеюп;его «ответвление сираза, еели действительгюе значение этого аргу.мента совпадает ео значением аргумента,указапного па лестничной диаграм.ме, и зпачепие функции при проверке предыдущего аргумента было равно 1. пример 2. Функция принимает значение «О при проверке аргумента, не имеющего «ответвления справа, если действительное 81 значение этого аргумента противололожно значению аргумента, указанного на лестничной диаграмме и значение функции при проверке предыдущего аргумента было равно 1. В первом случае сразу же (по наличию ответвления справа) обнаруживается дизл юнктивный член (параллельная цепочка) для той части функции, в которую входит проверяемый аргумент, и уетановка значения «О для функции означает, что проверенный член дизъюнкции равен 1, следовательно, вся дизъюнкция равна 1 и остается найти лишь последний аргу.мепт последнего члена дизъюнкции, после проверки :- оторого функция вновь должна принять З1 ачение равное 1. Этот последний аргу.мент па ходят по следующему правилу. По ходу вычисления (описанно.му выше) подсчитывается число ответвлений «справа вниз и «справа вверх. Тот ближайший шаг вычислений, в котором число ответвлений «справа вверх превышает на единицу число ответвлений «справа вниз указывает на пос..ледпий аргу.мент носледнего члена данной дизлж)нкции. При это.м функция вновь принимает значение 1 и вычиеление продолжается. Еели же при проверке аргумента, и.меющего «ответвление «справа вниз, его действительное состояние не совнадает с состоянием, указанны.м на лестничной диаграмме и нредыдущее значение функции равно 1, то это значение функц.чи сохраняется. Это означает, что проверенный член дизъюнкции равен О и необходимо вычислять остальные члены дизъюнкции. Во втором случае необходи.мо выяснить имеет ли часть функции, в которую входит что проверенный аргу.мепт, дизъюнктлвиый член. Если такого члена нет, то можно утверждать, что функция равна «О и это значение сохраняется до конца вычиелепий. Наличие дизъюнктивного члена определяется по следующе.му правилу. По ходу вычисления функции подсчитывается количество ответвлений «слева вниз и «справа вниз. Если в како.м-то из шагов вычислений число ответвлений «справа вниз превысит на единицу число ответвлений «слева вниз, это является указание.м на наличие дизъюнктивного члена к той части функции, которая приняла значение «О. При этом в следующе.м таге вычислений функция вновь принимает значение 1 и вычисление нродолжается. Описанный порядок и правила вычисления позволяют однозначно определить значение функции, а, следовательно, автоматизировать процесс програм.мной реализации любой сколь-угодно минимизированпой переключательной схемы. В начале вычисления триггер 1 находится в единичном состоянии (значение функции равно 1). В процессе вычисления последовательно, по шагам для каждого аргумента переключательной схемы на первый вход блока 2 подаются сигналы: «значение аргумента, указанного на лестничной диаграмме и «ответвление справа, а на второй вход этого блока подается сигнал действительного состояния аргумента. Если для какого-либо аргумента, действительное состояние аргумента совпадает с значением аргумента, указанного на лестничной диаграмме, и имеется сигнал «ответвление справа, то на выходе блока 2 проверки на нечетность появляется сигнал, устанавливающий триггер 1 в нулевое состояние, функция принимает значение О (пример 1, описанный в кратком пояснении процесса вычисления). Наличие сигнала «ответвление справа при установке триггера 1 в нулевое состояние запоминается в ячейке 4 памяти. Сигналы с выхода триггера 1 и ячейки 4 памяти, поступающие на второй и третий входы распределителя 5 организуют работу распределителя 5 таким образом, что на первый выход распределителя 5 подаются сигналы «ответвление справа вниз, а на второй выход распределителя 5 подаются сигналы «ответвление справа вверх. Эти сигналы соответственно поступают на первый и второй входы блока 6. Когда количество сигналов «ответвление справа вверх превысит на единицу количество сигналов «ответвление справа вниз, на выходе блока 6 появляется сигнал, устанавливающий триггер 1 в единичное состояние (функция прини.мает значение 1) и вычисление продолжается. Если же для какого-либо аргумента, действительное состояние аргумента не совпадает с значением этого аргумента, указанного на лестничной диаграмме, и сигнала «ответвление справа нет, то на выходе блока проверки на нечетность также появляется сигнал, устанавливающий триггер 1 в нулевое состояние, функция принимает значение 0. Отсутствие сигнала «ответвление справа при установке триггера 1 в нулевое состояние запоминается в ячейке 4 памяти. Сигналы с выхода триггера 1 и ячейки 4 памяти организуют работу распределителя 5 таким образом, что на первый выход распределителя 5 подаются сигналы «ответвление слева вниз, а на второй выход распределителя 5 подаются сигналы «ответвление справа вниз. Эти сигналы, соответственно, поступают на первый и второй входы блока 6. Когда количество сигналов «ответвление справа вниз превысит на единицу количество сигналов «ответвление слева вниз, на выходе блока 6 появляется сигнал, устанавливающий триггер 1 в единичное состояние (функция принимает значение 1) и вычисление продолжается. После проверки всех аргументов реализуемой переключательной схемы значение функции (I или 0) снимается с. выхода устройства. Предлагаемое устройство для программной реализации переключательных схем по сравнению с известными образцами аналогичного оборудования расширяет функциональные возможности и повышает надежность устройства. Формула изобретения Устройство для програ.ммной реализации переключательных схем, содержащее триггер, выход которого является выходом устройства, отличающееся тем, что, с целью расщирения функциональных возможностей за счет реализации скобочных форм в него введены блок проверки на нечетность, ячейка па.мяти, распределитель и блок подсчета числа ответвлений диаграммы, причем первые входы блока проверки на нечетность, ячейки памяти и распределителя объединены между собой и являются управляющим входом устройства, второй вход блока проверки на нечетность является входом аргумента, а выход соединен с первым входом триггера и вторым в.ходом ячейки памяти, выход которого соединен со вторым входом распределителя, третий вход которого подключен к выходу ячейки памяти, а выходы распределителя соединены с входами блока подсчета числа ответвлений диаграм.мы, выход которого соединен со вторым входом триггера. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 454547, кл. G 06 F 7/00, 1972. 2.Авторское свидетельство СССР № 610104, кл. G 06 F 7/00, 1975. л .JflpcBfl touiuu Bifod ri Q - Bxod

fpus.i Вь/жад о

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для подсчета числа ответвлений диаграммы | 1983 |

|

SU1160391A1 |

| Процессор программируемого контроллера | 1984 |

|

SU1269150A1 |

| Устройство для вычисления булевых функций | 1982 |

|

SU1049898A1 |

| Устройство для программной реализации переключательных схем | 1990 |

|

SU1836679A3 |

| Программируемый контроллер | 1986 |

|

SU1328815A1 |

| Устройство для подсчета числа ответвлений диаграммы | 1988 |

|

SU1539766A1 |

| Устройство для вычисления булевых функций | 1984 |

|

SU1218376A2 |

| Устройство для вычисления булевых функций | 1984 |

|

SU1242928A1 |

| Устройство для вычисления булевых функций | 1986 |

|

SU1372319A1 |

| Программируемый контроллер | 1985 |

|

SU1352484A1 |

n X3 W X5

X7

X7J

X6 X X8 X7/

Авторы

Даты

1981-03-15—Публикация

1978-12-25—Подача