Изобретение относится к вычисли- тельной технике, а именно к программному управлению технологическим оборудованием, и может быть использовано при построении программируемых контроллеров, в частности, реализующих функции алгебры логики.

Цель изобретения - сокращение объма блока памяти микрокоманд устрой- ства.

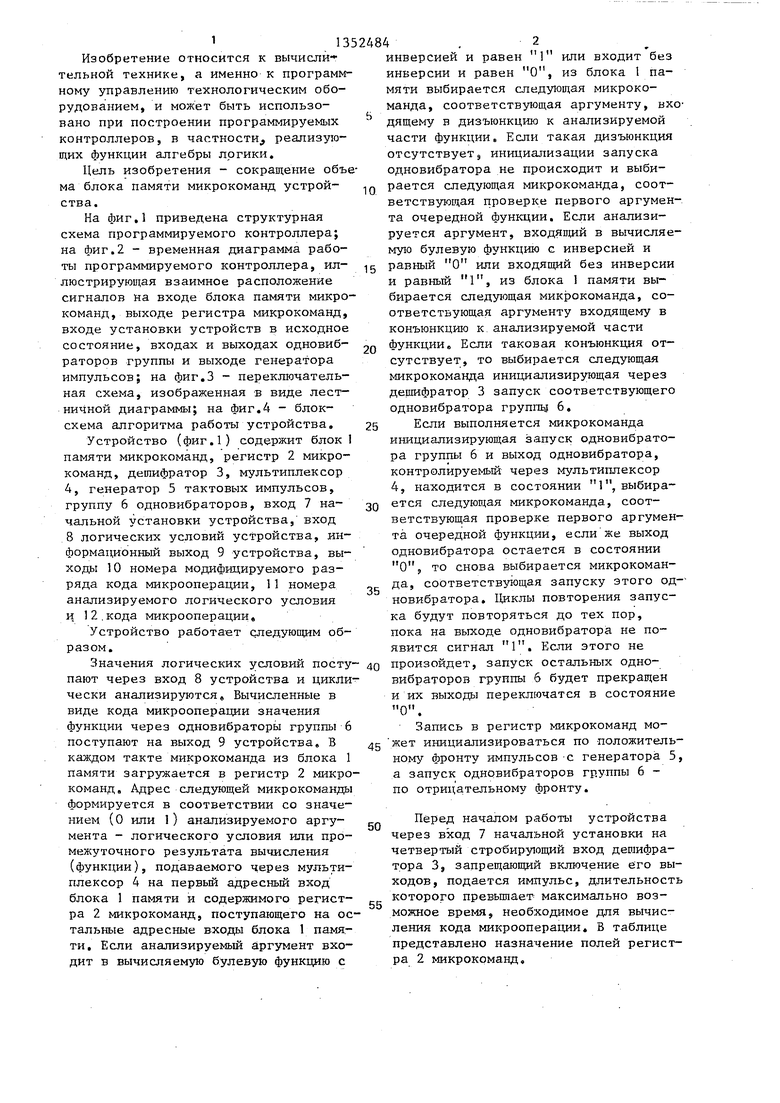

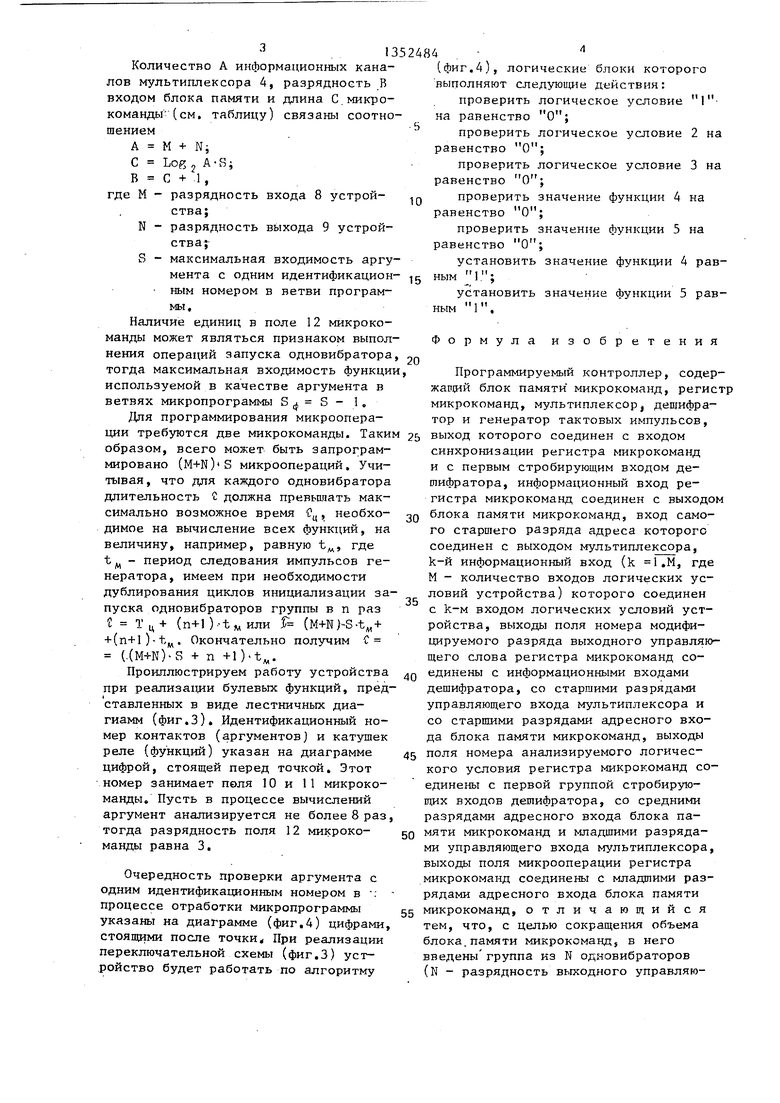

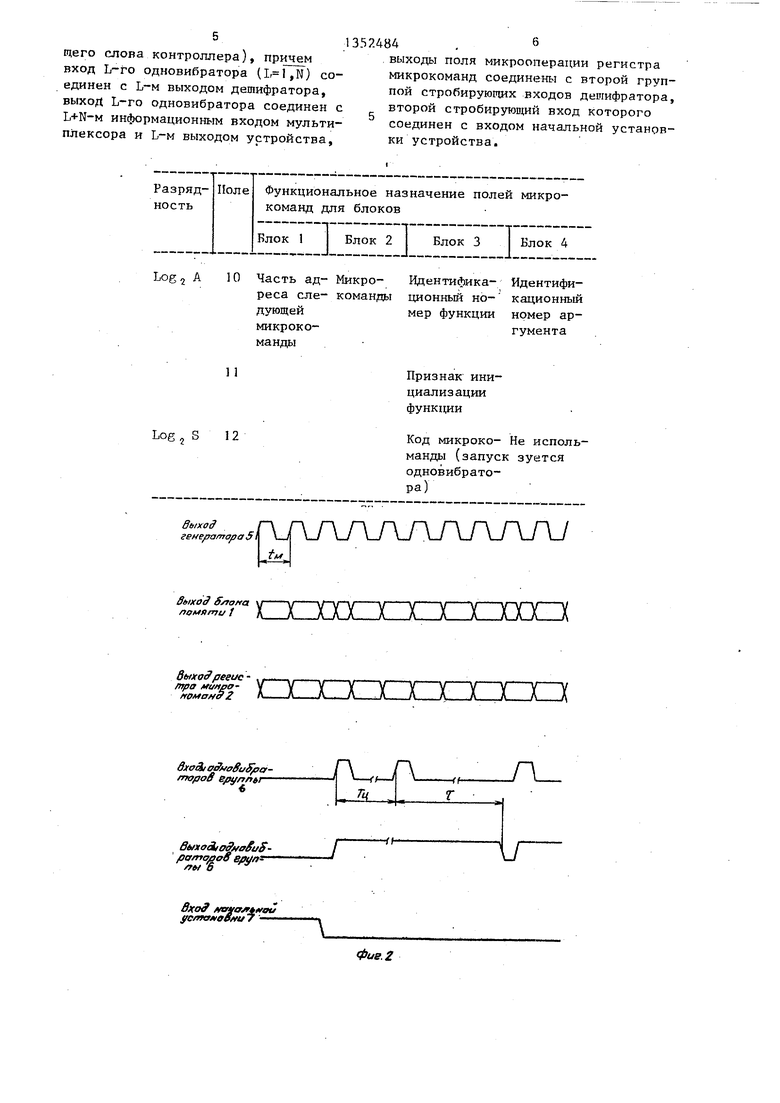

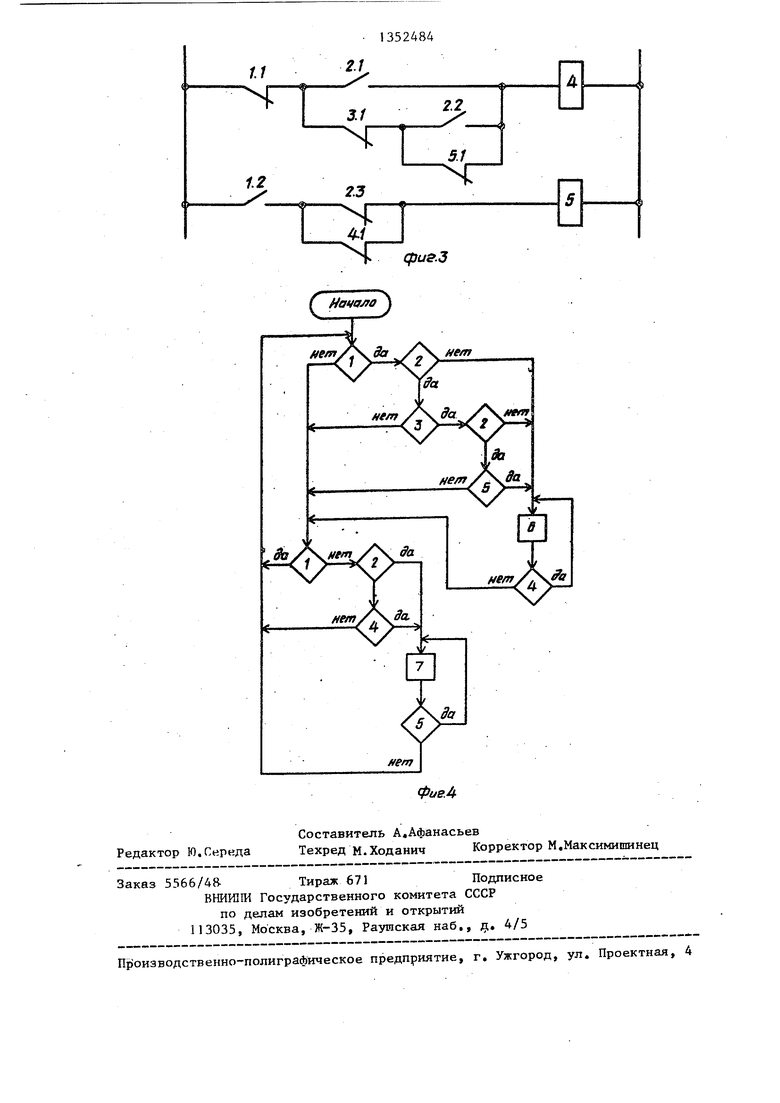

На фиг,1 приведена структурная схема программируемого контроллера; на фиг.2 - временная диаграмма работы программируемого контроллера, ил- люстрирующая взаимное расположение сигналов на входе блока памяти микрокоманд, выходе регистра микрокоманд, входе установки устройств в исходное состояние, входах и выходах одновиб- раторов группы и выходе генератора импульсов; на фиг.З - переключательная схема, изображенная в виде лестничной диаграммы; на фиг.4 - блок- схема алгоритма работы устройства.

Устройство (фиг.1) содержит блок памяти микрокоманд, регистр 2 микрокоманд, дешифратор 3, мультиплексор 4, генератор 5 тактовых импульсов, группу 6 одновибраторов, вход 7 на- чальной установки устройства, вход 8 логических условий устройства, информационный выход 9 устройства, выходы 10 номера модифицируемого разряда кода микрооперации, 11 номера анализируемого логического условия и. 12.кода микрооперации.

Устройство работает следуюпщм образом.

Значения логических условий посту пают через вход 8 устройства и циклически анализируются. Вычисленные в виде кода микрооперации значения функции через одновибраторы группы 6 поступают на выход 9 устройства, В каждом такте микрокоманда из блока 1 памяти загружается в регистр 2 микрокоманд. Адрес следзтощей микрокоманды формируется в соответствии со значением (о или 1) анализируемого аргумента - логического условия или промежуточного результата вычисления (функции), подаваемого через мультиплексор 4 на Первый адресный вход блока 1 памяти и содержимого регистра 2 микрокоманд, поступающего на остальные адресные входы блока 1 памяти. Если анализируемый аргумент входит в вычисляемую булевую функцию с

5

о

о 5

5

5

инверсией и равен 1 или входит без инверсии и равен О, из блока 1 памяти выбирается следующая микрокоманда, соответствующая аргументу, входящему в дизъюнкцию к анализируемой части функции. Если такая дизъюнкция отсутствует, инициализации запуска одновибратора не происходит и выбирается следующая микрокоманда, соответствующая проверке первого аргумента очередной функции. Если анализируется аргумент, входяпщй в вычисляемую булевую функцию с инверсией и равный О или входящий без инверсии и равный 1, из блока 1 памяти выбирается следующая микрокоманда, соответствующая аргументу входящему в конъюнкцию к анализируемой части функции. Если таковая конъюнкция отсутствует, то выбирается следующая микрокоманда инициализирующая через дещифратор 3 запуск соответствующего одновибратора группц 6,

Если выполняется микрокоманда инициализирующая запуск одновибратора группы 6 и выход одновибратора, контролируемый через мультиплексор 4, находится в состоянии 1, выбирается следующая микрокоманда, соответствующая проверке первого аргумента очередной функции, если же выход одновибратора остается в состоянии О, то снова выбирается микрокоманда, соответствующая запуску этого од-- новибратора. Циклы повторения запуска будут повторяться до тех пор, пока на выходе одновибратора не появится сигнал 1. Если этого не произойдет, запуск остальных одно- вибраторов группы 6 будет прекращен и их выходы переключатся в состояние О.

Запись в регистр микрокоманд мо- жет инициализироваться по положительному фронту импульсов-с генератора 5, а запуск одновибраторов группы 6 - по отрицательному фронту.

Перед началом работы устройства через вход 7 начальной установки на четвертый страбирзпощий вход дешифратора 3, запрещающий включение е го выходов, подается импульс, длительность которого превьплает максимально возможное время, необходимое для вычисления кода микрооперахщи, В таблице представлено назначение полей регистра 2 микрокоманд.

3

Log AS; С + .1 .

Количество A информационных каналов мультиплексора 4, разрядность В входом блока памяти и длина С.микрокоманды - (см, таблицу) связаны соотношением

А М + N; Q -

В .

где М - разрядность входа 8 устройства;N - разрядность выхода 9 устройства;

S - максимальная входимость аргумента с одним идентификацион- ным номером в ветви программы.

Наличие единиц в поле 12 микрокоманды может являться признаком выполнения операций запуска одновибратора тогда максимальная входимость функции используемой в качестве аргумента в ветвях микропрограммы S S - 1. Для программирования микроопера-

ции требуются две микрокоманды. Таким 25 выход которого соединен с входом образом, всего может быть запрограммировано (M+N) S микроопераций. Учитывая, что для каждого одновибратора длительность С должна превьшшть максимально возможное время 1, необходимое на вычисление всех функций, на

30

синхронизации регистра микрокоман и с первым стробирующим входом де шифратора, информационный вход ре гистра микрокоманд соединен с вых блока памяти микрокоманд, вход са го старшего разряда адреса которо соединен с выходом мультиплексора k-й информационный вход (k 1.М, М - количество входов логических ловий устройства) которого соедин с k-M входом логических условий у ройства, выходы поля номера модиф цируемого разряда выходного управл щего слова регистра микрокоманд с единены с информационными входами дешифратора, со старшими разрядами управляющего входа мультиплексора со старшими разрядами адресного вх да блока памяти микрокоманд, выход поля номера анализируемого логичес кого условия регистра микрокоманд единены с первой группой стробирую щих входов дешифратора, со средним разрядами адресного входа блока па мяти микрокоманд и младшими разряд ми управляющего входа мультиплексо выходы поля микрооперации регистра микрокоманд соединены с младшими р рядами адресного входа блока памят микрокоманд, отличающийс тем, что, с целью сокращения объем блока.памяти микрокоманд, в него введены группа из N одновибраторов (N - разрядность выходного управля

величину, например, равную t,, где t - период следования импульсов генератора, имеем при необходимости дублирования циклов инициализации запуска одновибраторов группы в п раз t Тц+ (п+1 ).-tA, или 1Г (,+ + (n+l)-tn,. Окончательно получим С (.(M+K)-S + п +l)-t,.

Проиллюстрируем работу устройства при реализахщи булевых функций, пред ставленных в виде лестничных диа- гиамм (фиг.З), Идентификационный номер контактов (аргументов) и катушек реле (функций) указан на диаграмме цифрой, стоящей перед точкой. Этот номер занимает поля 10 и 11 микрокоманды. Пусть в процессе вычислений аргумент анализируется не более 8 раз тогда разрядность поля 12 микрокоманды равна 3.

Очередность проверки аргумента с одним идентификационным номером в т процессе отработки микропрограммы указаны на диаграмме (фиг,4) цифрами, стоящими после точки При реализации переключательной схемы (фиг,3) устройство будет работать по алгоритму

10

g(фиг.4), логические блоки которого выполняют следуюише действия:

проверить логическое условие на равенство

проверить логическое условие 2 на равенство

проверить логическое условие 3 на равенство

проверить значение функции 4 на равенство

проверить значение функции 5 на равенство

установить значение функции 4

равным

установить ным 1.

значение функции 5 равФормула изобретения

Программируемый контроллер, содер- жап{ий блок памяти микрокоманд, регистр микрокоманд, мультиплексор, дешифратор и генератор тактовых импульсов.

25 выход которого соединен с входом

30

35

0

5

0

5

синхронизации регистра микрокоманд и с первым стробирующим входом дешифратора, информационный вход регистра микрокоманд соединен с выходом блока памяти микрокоманд, вход самого старшего разряда адреса которого соединен с выходом мультиплексора, k-й информационный вход (k 1.М, где М - количество входов логических условий устройства) которого соединен с k-M входом логических условий устройства, выходы поля номера модифицируемого разряда выходного управляющего слова регистра микрокоманд соединены с информационными входами дешифратора, со старшими разрядами управляющего входа мультиплексора и со старшими разрядами адресного входа блока памяти микрокоманд, выходы поля номера анализируемого логического условия регистра микрокоманд соединены с первой группой стробирую- щих входов дешифратора, со средними разрядами адресного входа блока памяти микрокоманд и младшими разрядами управляющего входа мультиплексора, выходы поля микрооперации регистра микрокоманд соединены с младшими разрядами адресного входа блока памяти микрокоманд, отличающийся тем, что, с целью сокращения объема блока.памяти микрокоманд, в него введены группа из N одновибраторов (N - разрядность выходного управляющего слова контроллера), причем вход L-ro одновибратора (,N) соединен с L-M выходом дешифратора, выход L-ro одновибратора соединен с L+N-M информационным входом мультиплексора и L-M выходом устройства.

10 Часть ад- Микро- реса еле- команды дующей микрокоманды

1

Log J S

12

выход генератора 5

9t,ixo уу rY V Г -VVV У

памяти / Л Л лЛЛл А ЛАА-А-А/

sF ncjazizxiDaaija

влсА/ oAfoSuSfia- fnopoS еруггпб

о

Bb/xoatfoAffffuS- рата/зов ы 6

Blfoff

ус/яомве/м 7 -

6

выходы ПОЛЯ микрооперации регистра микрокоманд соединены с второй группой стробирующих входов девшфратора, второй стробир5пощий вход которого соединен с входом начальной установки устройства.

Идентификационный но- мер функции

Признак инициализациифункции

Код микроко- Не исполь- манды (запуск зуется одновибратора)

л

C HawJJO

фи.З

Редактор Ю.Снркда

фиеЛ

Составитель А,Афанасьев

Техред м.Ходанич Корректор М.Максимишинец

Заказ 5566/48- Тираж 671Подписное

ВНИИ11И Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, ц, 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1987 |

|

SU1444762A1 |

| Устройство микропрограммного управления | 1984 |

|

SU1236476A1 |

| Программируемый контроллер | 1988 |

|

SU1612276A1 |

| Мультимикропрограммная управляющая система | 1989 |

|

SU1631542A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Многотактное микропрограммное устройство управления | 1983 |

|

SU1151963A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1397908A1 |

| Устройство для программного управления | 1989 |

|

SU1656498A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134936A1 |

Изобретение относится к области вычислительной техники, а именно к программному управлению технологическим оборудованием, и может быть использовано при построении программируемых контроллеров. Цель изобретения - сокращение объема блока памяти микрокбманд устройства. Устройство содержит блок 1 памяти микрокоманд, регистр 2 микрокоманд, дешифратор 3, мультиплексор. 4, генератор 5 тактовых импульсов и группу 6 одновибра- торов. Введение группы одновибрато- ров приводит к достижению цели. 4 ил., 1 табл. фиеЛ

| Мейзда Ф | |||

| Интегральные схемы, технология и применение | |||

| М.: Мир, 1981 | |||

| Конвейерное устройство для изготовления маканых резиновых изделий | 1958 |

|

SU122607A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-11-15—Публикация

1985-09-26—Подача