(54) МНОЖИТЕЛЬНО-ДБЛИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1978 |

|

SU813419A1 |

| Множительно-делительное устройство | 1981 |

|

SU1015373A1 |

| Множительно-делительное устройство | 1980 |

|

SU902026A1 |

| Множительно-делительное устройство | 1977 |

|

SU788128A1 |

| Частотно-импульсное вычислительное устройство | 1980 |

|

SU881744A1 |

| Множительно-делительное устройство | 1978 |

|

SU746511A1 |

| Устройство для преобразования разности частотно-импульсных сигналов в код | 1976 |

|

SU750728A1 |

| Множительно-делительное устройство | 1975 |

|

SU590736A1 |

| Частотно-импульсное делительное устройство | 1978 |

|

SU763914A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1968 |

|

SU217718A1 |

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам для выполнения множительно-делительных операций с частотно-импульсными сигналами.

Известно множительно-делительное устройство, содержащее счетчики,делитель частоты, регистр памяти, блоки управления и группы элементов И С }Недостатком устройства является конструктивная сложность.

Известно также множительно-дели тельное устройство, содержащее счетчики, регистр памяти, блок сравнения кодов, буферный узел, дифференцирукмцую цепь и элемент ИЛИ lДанное устройство характеризуется сложностью технической реализации при широком диапазоне изменения входных частот.

Известно также множительно-делительное устройство, содержащее делитель частоты, вход которого соединен с шиной ввода первого сомножителя делимого, элемент задержки, подключенный входом к управляющему входу регистра памяти, а выходом - к входу управления установкой кода первого счетчика, соединенного выходом с информационным входом памяти, подключенного выходом к первому входу блока сравнения кодов, соединенного вторым входом с выходом второго счетчика, а выходом - с выходом шиной устройства и с входом управления установкой кода второго счетчика,счетный вход которого подключен к шине ввода второго сомножителя делимого, а счетный вход первого счетчика сое10динен с выходом элемента И, подключенного первым входом к шине ввода делителя, а вторым входом - к выходу делителя частоты и к первому входу формирователя импульсов, соединенно15го вторым входом с выходом блока сравнения кодов, а выxoдo л - с входом элемента 3.

Недостатком прототипа является сложность технической.реализации

20 из-за необходимости использования счетчиков и регистра памяти повышенной разрядности для выполнения множительно-делительных операций с заданной точностью в широком диапазоне

25 изменения входных частот.

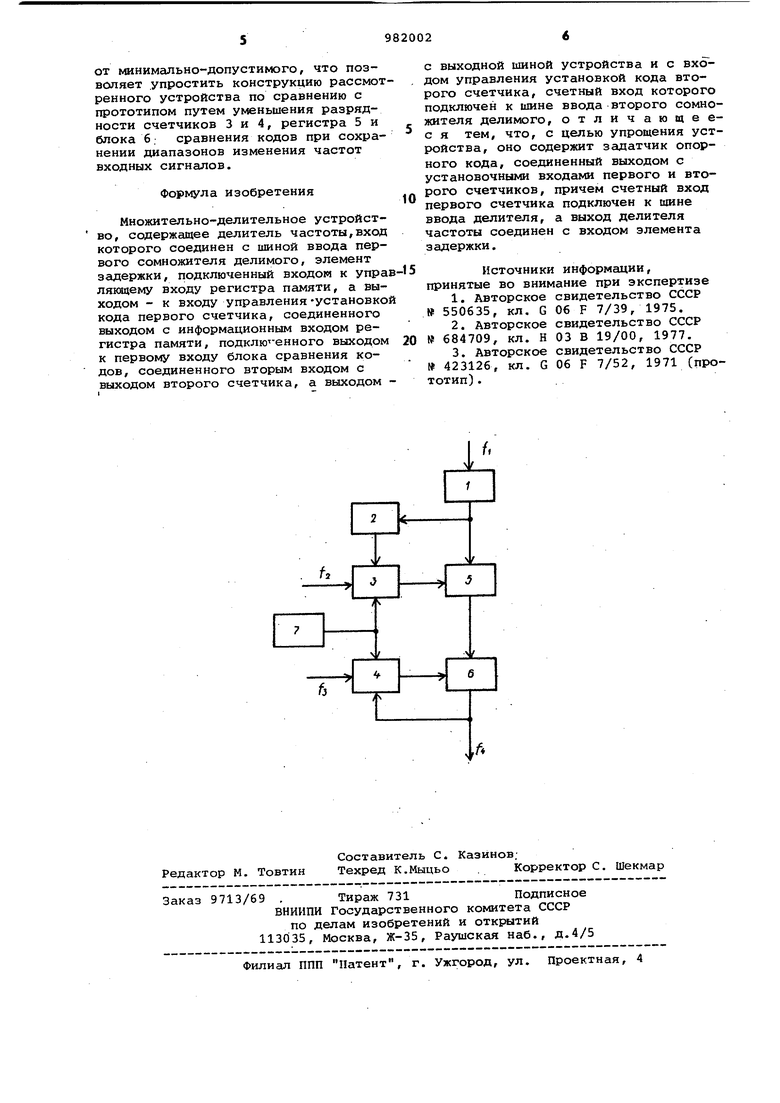

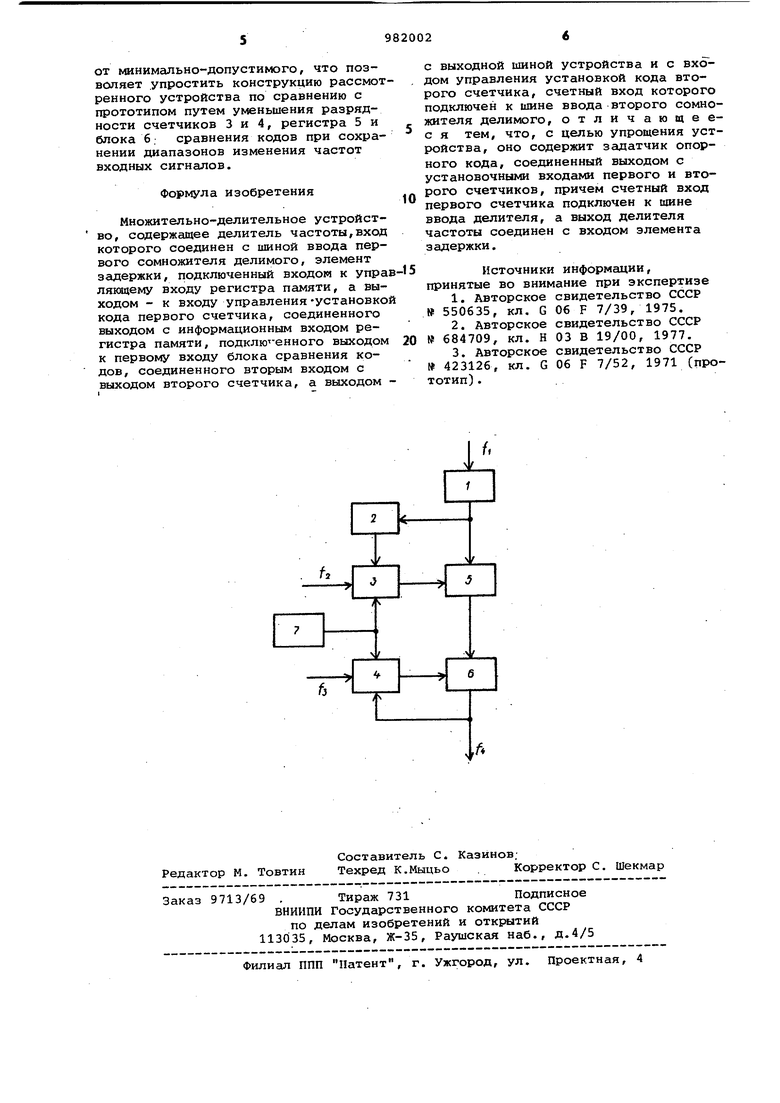

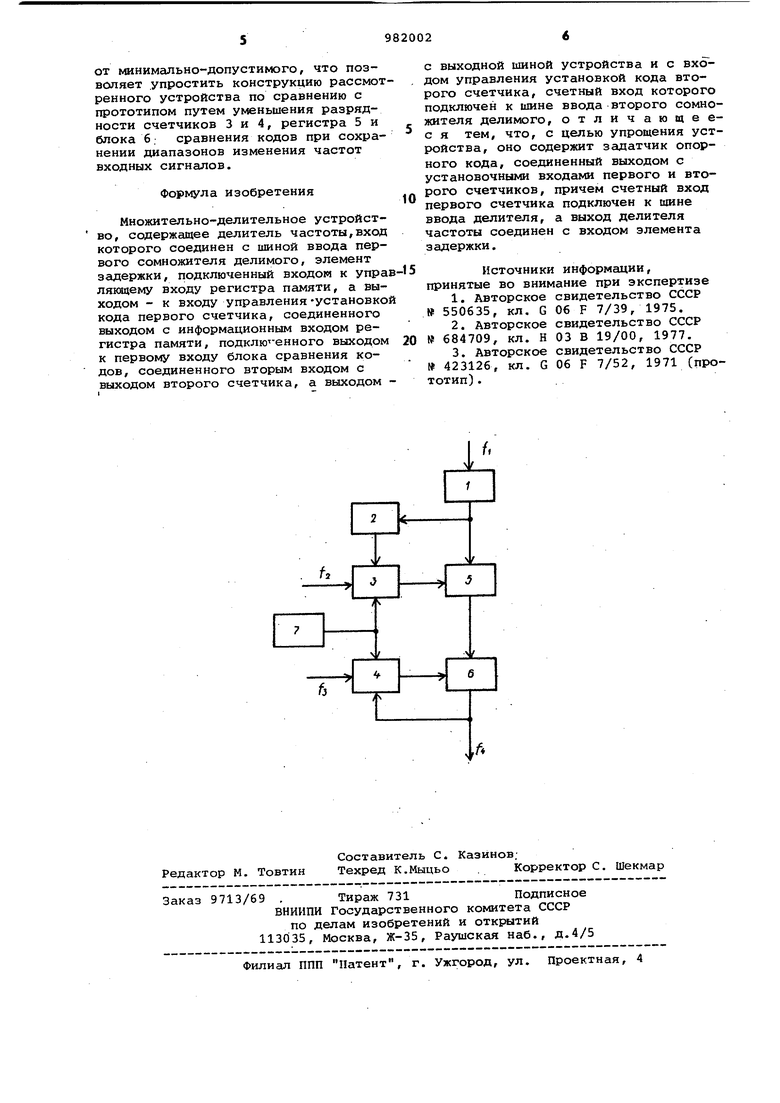

Цель изобретения - упрощение устройства. Цель достигается тем,что множительно-делительное устройство, содер30жащее делитель частоты, вход которого соединен с шиной ввода первого сомножителя делимого, элемент задержки, подключенный входом к управляющему входу регистра памяти, а выходом к входу управления установкой кода первого .счетчика, соединенного выходом с информационным входом регистра памяти, подключенного выходом к первому входу блока сравнения кодов, соединенного входом с выходом входного счетчика, а выходом - с выходной шиной устройства и с входом управле.ния установкой кода второго счетчика, счетный вход которого подключен к шине ввода второго сомножителя делимого, содержит задатчик опорного кода, соединенный выходом с установочными входами первого и второго счетчиков, причем счетный вход первого счетчика подключен к шине ввода делителя, а выход делителя частоты соединен с входом элемента задержки. На чертеже изображена блок-схема множительно-делительного устройства. Устройство содержит делитель 1 ча тоты, элемент 2 задержки, первый и второй счетчики 3 и 4, регистр 5 памяти, блок б сравнения кодов и задатчик 7 опорного кода. Делитель 1 соединен входом с шиной ввода первого сомножителя делимого, а выходом - с входом элемента 2 задержки и с управ ляющим входом регистра 5 памяти. Выход элемента 2 задержки подключен к входу управления установкой кода сче чика 3, соединенного счетным входом с шиной -ввода делителя, а выходом - с информационным входом регистра 5. Выход регистра 5 подключен к первому входу блока 6 сравнения кодов, соединенного вторым входом с ВЫ25ОДОМ счетчика 4, а вькодом - с выходной шиной устройства и с входом управления установкой кода счетчика 4. Счетчик 4 подключен счет ным входом к шине ввода второго сомн жителя делимого. Задатчик 7 опорного кода соединен выходом с установочным входами счетчиков 3 и 4. Множительно-делительное устройств работает следующим образом. Частота поступает на вход делителя 1 частоты, с выхода которого импульсы частотой , /К (где К коэффициент деления делителя 1) пост пают на вход элемента 2 задержки и н управляющий вход регистра 5. При это в регистре 5 записывается текущее значение кода с выхода счетчика 3, н счетный вход которого непрерывно поступают импульсы частоты -2. делимого По истечении времени, необходимого для записи кода в регистр 5 с выхода элемента 2 задержки на вход управления установкой кода счетчика 3 посту пает импульс, по которому счетчик 3 устанавливается в исходное состояние При этом в счетчик 3 через его установочный вход записывается в обратном коде число Hfo (где NO - опорный код, задаваемый задатчиком 7). Таким обазом, исходное состояние счетчика 3будет соответствовать числу N - paaномуN а - N o Of где основание кода; п - количество разрядов счетчика 3. Импульсы частоты 2 делимого,поступая на счетный вход счетчика 3, переполняют этот счетчик и к моменту поступления на управлякядий вход регистра 5 импульса с выхода делитея 1 на выходе счетчика 3 формируется код, соответствующий числу N : N-я, непрерывно поступает с выхода регистра 5 на первый вход блока б сравнения, на второй вход которого поступает текущее значение кода счетчика 4, накапливающего импульсы частоты 2 второго сомножлтеля делимого. При совпадении кодов блока б вырабатывает импульс выходной частоты , который подается на выходную шину устройства-и на вход управления установкой кода счетчика 4. Счетчик 4 устанавливается в исходное состояние,при этом по установочному входу в счетчик 4записывается в обратном коде число NO, т.е. в исходном состояние в счетчик 4 аналогично счетчику 3 записывается число Np. Очевидно, что к моменту совпадения кодов на входах блока 6 (т.е. за интервал времени, равный периоду выходной частоты устройства) в счетчике 4 будет сформирован код числа N .-.No Учитывая, что N N получаем fi-f Таким образом, выходная частота множительно-делительного устройства равна отношению произведения частот первого и третьего частотных сигналов к произведению коэффициента деления делителя 1 частоты и частоты второго частотного сигнгша. При установке кода на выходе задатчика 7 должно выполняться соотношение NP (где минимальное значение накапливаемого кода, определяемое требуемой точностью выполнения операций умножения и деления в устройстве). В этом случае коды N и N-j будут представлять собой отклонение текущих значений кодов

от минимально-допустимого, что позволяет упростить конструкцию рассмотренного устройства по сравнению с прототипом путем уменьшения разрядности счетчиков 3 и 4, регистра 5 и блока 6. сравнения кодов при сохранении диапазонов изменения частот входных сигналов.

Формула изобретения

Множительно-делительное устройство, содержащее делитель частоты,вход которого соединен с шиной ввода первого сомножителя делимого, элемент задержки, подключенный входом к упра лякяцему входу регистра памяти, а выходом - к входу управления-установко кода первого счетчика, соединенного выходом с информационным входом регистра памяти, подклю-енного выходом к первому входу блока сравнения кодов, соединенного вторым входом с выходом второго счетчика, а выходом с выходной шиной устройства и с входом управления установкой кода второго счетчика, счетный вход которого подключен к шине ввода -второго сомножителя делимого, отличаювдеес я тем, что, с целью упрощения устройства, оно содержит задатчик опорного кода, соединенный выходом с установочными входами первого и второго счетчиков, причем счетный вход первого счетчика подключен к шине ввода делителя, а выход делителя частоты соединен с входом элемента задержки.

Источники информации, принятые во внимание при экспертизе

№ 423126, кл. G 06 F 7/52, 1971 (прототип).

,

/

Авторы

Даты

1982-12-15—Публикация

1981-05-25—Подача