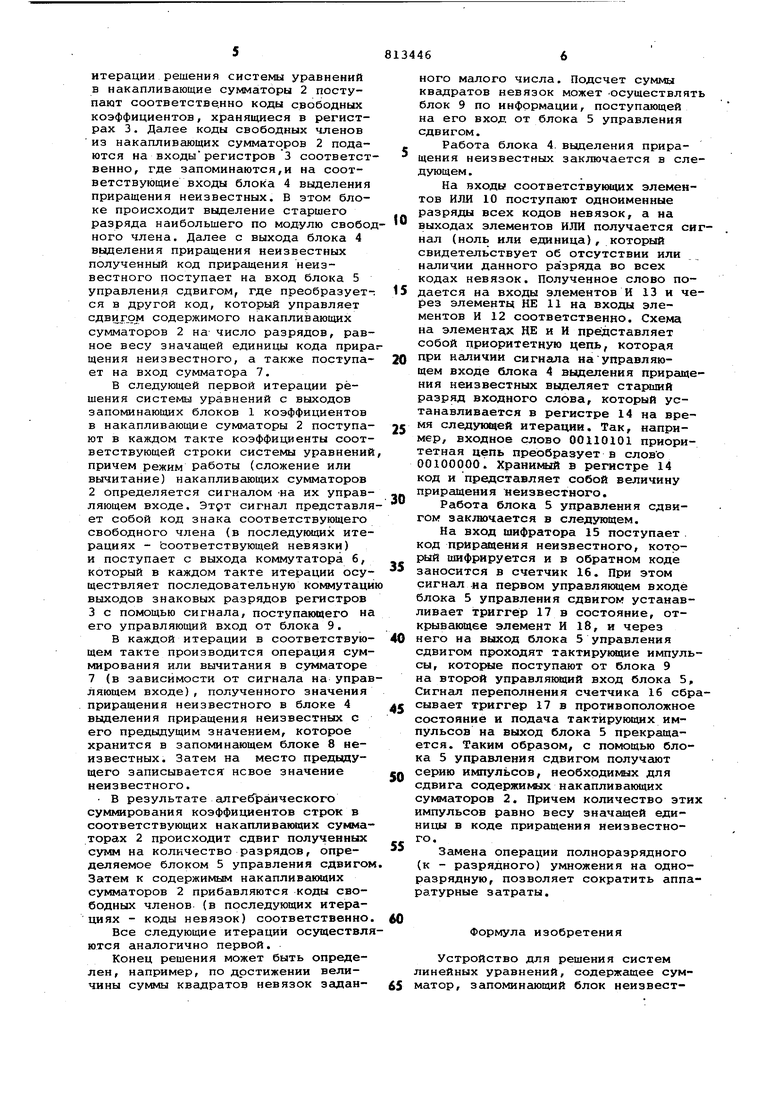

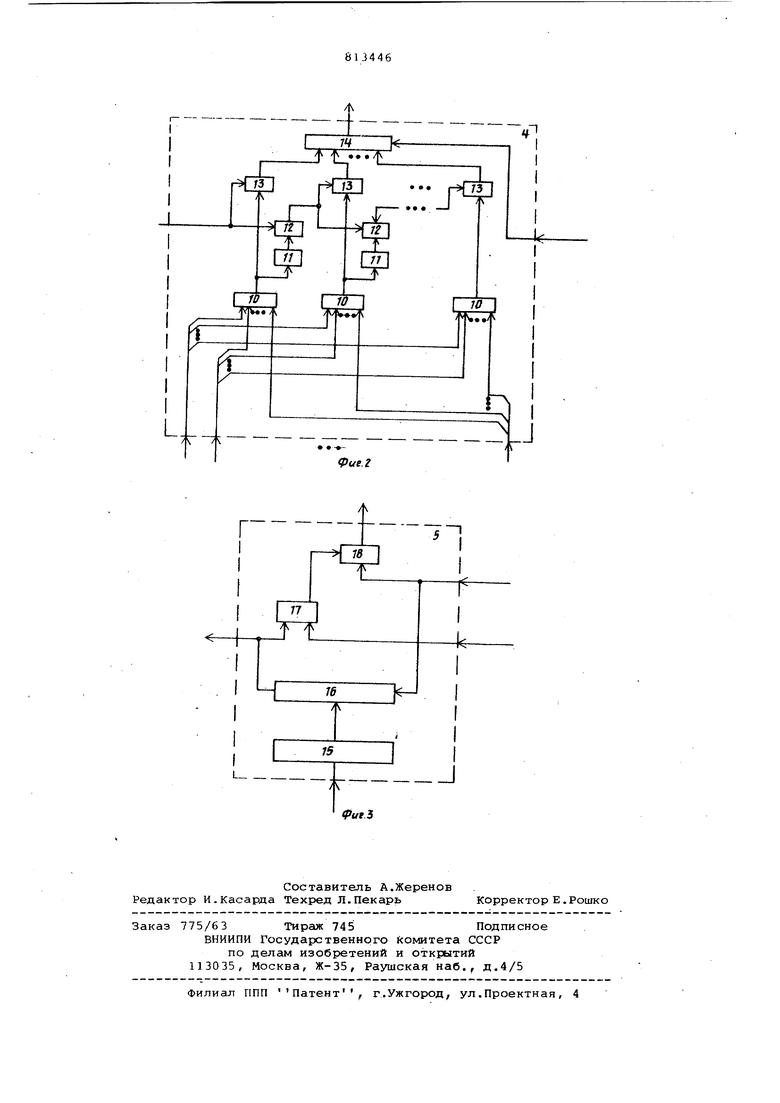

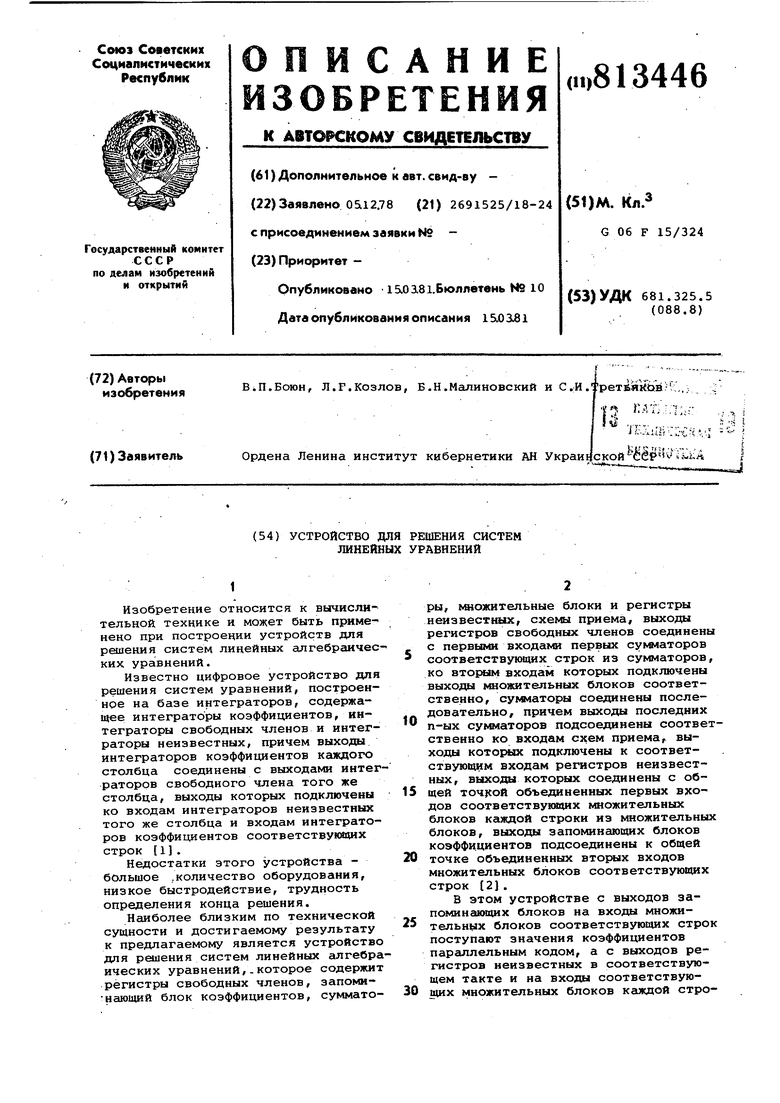

(54) УСТРОЙСТВО для РЕШЕНИЯ СИСТЕМ ЛИНЕЙНЫХ УРАВНЕНИЙ ки подаются последовательно, начина с младших, разряды неизвестных. Полученные разряды произведений коэффициентов на неизвестные в соответствующем такте суммируются между со бой и с кодом свободного члена на последовательном сумматоре, состоящем из п сумматоров. Результат выполненных операций (код невязки) передается в -схему приема, которая преобразует поступивший код невязки в код неизвестного (например, выделяется часть величины невязки), Полученное таким образом новое прибли жение неизвестного используется в следующей итерации. Недостаток этого устройства большое количество оборудования, ко торое заключается в основном в п строках из сумматоров и в п строках из п множительных блоков, причем каждый из последних, в свою очередь содержит к - разрядный сумматор и к разрядный регистр. Цель изобретения - сокращение об рудования, Поставленная цель достигается тем, что устройство для решения сис тем линейных уравнений, содержгицее сумматор, запоминающий блок неизвес ных, регистры, накапливающие суммат ры и запоминающие блоки коэффициентов, выход каждого из которых подключен к, первому входу соответству ющего накапливающего сумматора, вто рой вход которого соединен с первым выходом соответствующего регистра, содержит блок выделения приращения .неизвестных, блок управления сдвигом, коммутатор и блок формирования тактовых сигналов, выходы которого подключены соответственно к первому и второму управляющим входам блоков выделения приращения неизвестных, блока управления сдвигом и к управляющему входу коммутатора, выход каждого накапливающего сумматора подключен к входу соответствующего регистра и к соответствующему информационному входу блока выделения приращения неизвестных, выход которого подключен к первому входу сумматора и к входу блока управления сдвигом, первый выход которого сое динён с входом блока формирования тактовых сигналов, второй выход бло ка управления сдвигом подключен к первым управляющим входам накапливающих сумматоров, вторые управляющие входы которых соединены с выходом коммутатора, второй выход каждого регистра соединен с соотВетствукицим входом коммутатора, ко торого подключен к управляющему вхо ду сумматора J, второй вход которого соединен с выходом запоминающего блока неизвестных, вход которого подключен к выходу сумматора, Кроме того, в устройстве блок выделения приращения неизвестных содержит регистр, две группы элементов И, элементы НЕ и группу элементов ИЛИ, входы которых соединены с информационными входами блока, выход каждого элемента ИЛИ, кроме последнего, подключен к первому входу соответствующего элемента И первой группы и через элемент НЕ к первому входу соответствующего элемента И второй группы, вторые входы первых элементов И первой и второй групп соединены с первым управляющим входом блока, выходы элементов И первой группы подключены соответственно к входам регистра, выход которого является выходом блока, выход каждого элемента И второй группы подключен к вторым входам последующих элементов И первой и второй групп, выход последнего элемента ИЛИ соединен с первым входом последнего элемента И первой группы, управляющий вход регистра является вторым управляющим входом блока, а блок управления сдвигом содержит элемент И, триггер, счетчик и шифратор, вход которого является входом блока, выход шифратора соединен с входом счетчика, выход которого соединен с первым входом триггера и с первым выходом блока, второй вход триггера подключен к первому управляющему входу блока, второй управляющий вход которого соединен с управляющим входом счетчика и с первым входом элемента И, второй вход которого подключен к выходу триггера, выход элемента И является вторым выходом-блока. На фиг.1 представлена схема устройства; на фиг.2 и 3 - схемы соответственно блока выделения приращения неизвестных и блока управления сдвигом. Устройство содержит запоминающие блоки 1 коэффициентов, накапливающие сумматоры 2, регистры 3, блок 4 выделения приращения неизвестных,блок 5 управления сдвигом, коммутатор 6, сумматор 7, запоминающий блок 8 неизвестных, блок 9 формирования тактовых сигналов, группа элементов ИЛИ 10, элементы НЕ 11, группы элементов И 12, 13, регистр 14, шифратор 15, счетчик 16, триггер 17, элемент И 18, Устройство работает следующим образом. В запоминающий блок 1 коэффициентов заносятся коды коэффициентов соответствующих строк, в регистрах 3 устанавливаются соответственно коды свободных членов, в запоминающий блок 8 неизвестных заносятся нулевые начальные приближения неизвестных. Накапливающие сумматоры 2 устанавливгиотся в ноль, В нулевой

итерации решения системы уравнений в накапливающие сумматоры 2 поступают соответственно коды свободных коэффициентов, хранящиеся в регистрах 3. Далее коды свободных членов из накапливающих сумматоров 2 подаются на входырегистровЗ соответственно, где запоминаются,и на соответствующие входы блока 4 выделения приращения неизвестных. В этом блоке происходит выделение старшего разряда наибольшего по модулю свободного члена. Далее с выхода блока 4 выделения приращения неизвестных полученный код приращения неизвестного поступает на вход блока 5 управления сдвигом, где преобразуется в другой код, который управляет сдвигрм содержимого накапливающих сумматоров 2 на число разрядов, равное весу значащей единицы кода приращения неизвестного, а также поступает на вход сумматора 7.

В следующей первой итерации решения системы уравнений с выходов запоминающих блоков 1 коэффициентов в накапливающие сумматоры 2 поступают в каждом такте коэффициенты соответствующей строки системы уравнений причем режим работы (сложение или вычитание) накапливающих сумматоров

2определяется сигналом На их управляющем входе. Этрт сигнал представляет собой код знака соответствующего свободного члена (в последующих итерациях - Ьоответствующей невязки)

и поступает с выхода коммутатора б, который в каждом такте итерации осуществляет последовательную колмутаци выходов знаковых разрядов регистров

3с помощью сигнала/ поступающего на его управляющий вход от блока 9.

В каждой итерации в соответствующем такте производится операция суммирования или вычитания в сумматоре 7 (в зависимости от сигнала на управляющем входе), полученного значения приращения неизвестного в блоке 4 выделения приращения неизвестных с его предыдущим значением, которое хранится в запоминающем блоке 8 неизвестных. Затем на место предыдущего записывается новое значение неизвестного.

В результате алгебраического суквлирования коэффициентов строк в соответствующих накапливающих сумлаторах 2 происходит сдвиг полученных сумм на количество разрядов, определяемое блоком 5 управления сдвигом Затем к содержимым накапливающих сумматоров 2 прибавляются коды свободных членов (в последующих итерациях - коды невязок) соответственно

Все следующие итерации осуществлются аналогично первой.

Конец решения может быть определен, например, по достижении величины суммы квадратов невязок заданного малого числа. Подсчет суммы квсщратов невязок может осуществлят блок 9 по информации, поступающей на его вход от блока 5 управления сдвигом.

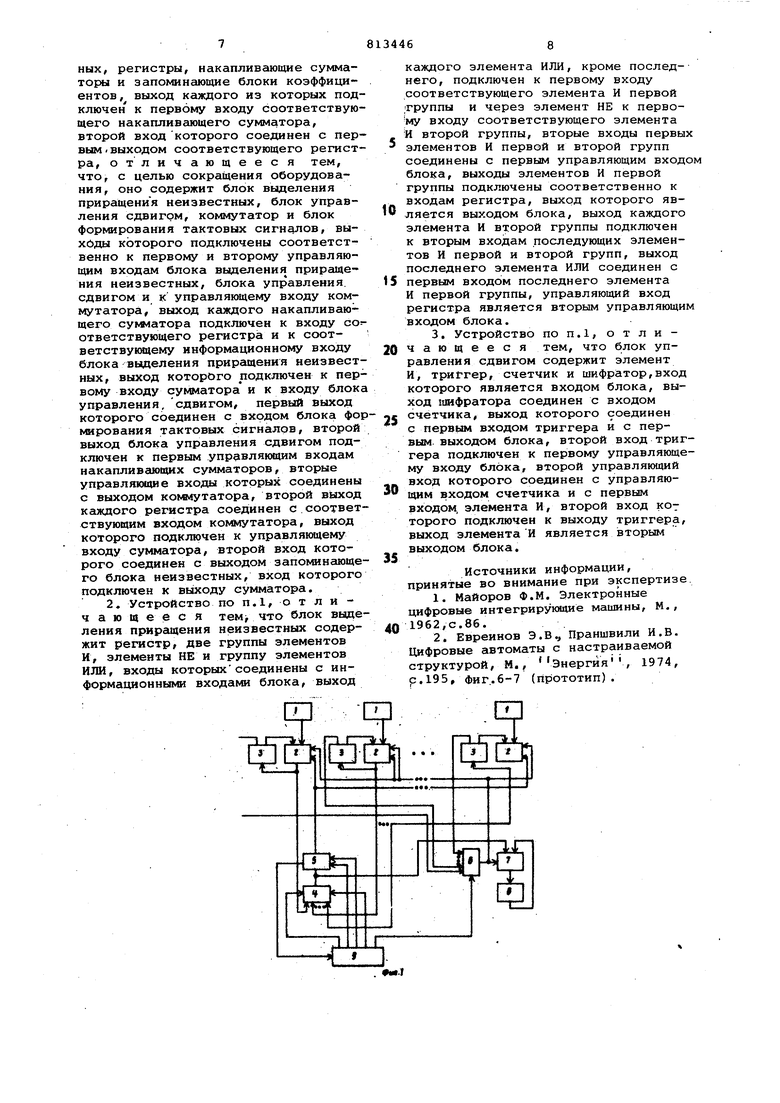

Работа блока 4. выщеления приращения неизвестных заключается в следующем .

На входы соответствующих элементов ИЛИ 10 поступают одноименные разряды всех кодов невязок, а на выходах элементов ИЛИ получается синал (ноль или единица), который свидетельствует об отсутствии или наличии данного разряда во всех кодах невязок. Полученное слово подается на входы элементов И 13 и через элементы НЕ 11 на входы элементов И 12 соответственно. Схема на элементах НЕ и И прёйставляет собой приоритетную цепь, которая при наличии сигнала на управляющем входе блока 4 выделения приращения неизвестных выделяет стагмиий разряд входного слова, который устанавливается в регистре 14 на время следующей итерации. Так, например, входное слово 00110101 приоритетная цепь преобразует в слово 00100000. XpaHHNffidt в регистре 14 код и представляет собой величину приращения неизвестного.

Работа блока 5 управления сдвигом заключается в следующем.

На вход шифратора 15 поступает код приргацения неизвестного, который шифрируется и в обратном коде заносится в счетчик 16. При этом сигнал -На первом управлякяцем входе блока 5 управления сдвигом устанавливает триггер 17 в состояние, открывающее элемент И 18, и через него на выход блока 5 управления сдвигом проходят тактирукяцие импульсы, которые поступгиот от блока 9 на второй управляющий вход блока 5, Сигнал переполнения счетчика 16 сбрсывает триггер 17 в противоположное состояние и подача тактирующих импульсов на выход блока 5 прекращается. Таким образом, с помощью блока 5 управления сдвигом получгиот серию импульсов, необходимых для сдвига содержиг их накапливающих сумматоров 2. Причем количество эти импульсов равно весу значащей единицы в коде приращения неизвестного.

Замена операции полноразрядного (к - разрядного) умножения на одноразрядную, позволяет сократить аппаратурные затраты.

Формула изобретения

Устройство для решения систем линейных уравнений, содержащее сумматор, запоминающий блок неизвестных, регистры, накапливающие сумматоры и запоминающие блоки коэффициентов, выход каждого из которых подключен к первому входу соответствующего накапливающего сумматора, второй вход которого соединен с первым выходом соответствующего регистра, отлич ающеес я тем, что, с целью сокращения оборудования, оно содержит блок выделения приращения неизвестных, блок управления сдвигом, коммутатор и блок фор1 {рования тактовых сигналов, выхйды которого подключены соответственно к первому и второму управляющим входс1м блока выделения приращения неизвестных, блока управления, сдвигом и к управляющему входу коммутатора, выход каждого накапливающего сумматора подключен к входу со ответствующего регистра и к соотдействующему информационному входу блока выделения приращения неизвестных, выход которого подключен к первому входу сукв атора и к входу блока управления, сдвигом, первый выход которого соединен с входом блока формирования тактовых сигналов, второй выход блока управления сдвигом подключен к первым управляющим входам накапливающих сумматоров, вторые управлякйцие входы которых соединены с выходом коьвлутатора, второй выход ксикдого регистра соединен с соответствующим входом коммутатора, выход которого подключен к управляющему входу сумматора, второй вход которого соединен с выходом запоминающего блока неизвестных, вход которого подключен к вьисоду сумматора.

2. Устройство по П.1, отличающееся тем что блок выделения приращения неизвестных содержит регистр, две группы элементов И, элементы НЕ и группу элементов ИЛИ, входы которыхсоединены с информационными входами блока, выход

каждого элемента ИЛИ, кроме последнего, подключен к первому входу соответствующего элемента И первой ;группы и через элемент НЕ к перво му входу соответствующего элемента И второй группы, вторые входы первы элементов И первой и второй групп соединены с первым управляющим вход блока, выходы элементов И первой группы подключены соответственно к входам регистра, выход которого является выходом блока, выход каждого элемента И второй группы подключен к вторым входам последующих элементов И первой и второй групп, выход последнего элемента ИЛИ соединен с первым входом последнего элемента И первой группы, управляющий вход регистра является вторым управляющи входом блока.

3. Устройство по П.1, отличающееся тем, что б;лок управления сдвигом содержит элемент И, триtrep, счетчик и шифратор,вход которого является входом блока, выход 1гмфратора соединен с входом счетчика, выход которого соединен с первым входом триггера и с первым выходом блока, второй вход триггера подключен к первому управляющему входу блока, второй управляющий вход которого соединен с управляющим входом счетчика и с первым входом, элемента И, второй вход ког торого подключен к выходу триггера, выход элемента И является вторым выходом блока.

Источники информации, принятые во внимание при экспертизе

1.Майоров Ф.М. Электронные цифровые интегрирукмцие машины, М., 1962,с.86.

2.Евреинов Э.В., Праншвили И.В. Цифровые автоматы с настраиваемой структурой, М., энергия, 1974, С.195, ФИГ..6-7 (прототип).

- - --1

т

I HF

u1

-JI

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения интеграль-НыХ уРАВНЕНий | 1979 |

|

SU817726A1 |

| Устройство для решения системлиНЕйНыХ уРАВНЕНий | 1979 |

|

SU830396A1 |

| Устройство для решения систем линйныхАлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU824217A1 |

| Устройство для решения системлиНЕйНыХ уРАВНЕНий | 1978 |

|

SU798862A1 |

| Многоканальное устройство для реше-Ния иНТЕгРАльНыХ уРАВНЕНий | 1979 |

|

SU840921A1 |

| Устройство для решения интегральных уравнений Фредгольма второго порядка | 1985 |

|

SU1295413A1 |

| Вычислительное устройство для решениязАдАчи ВыпРАВКи жЕлЕзНОдОРОжНОгО пуТи | 1977 |

|

SU802967A2 |

| Устройство для решения интегральных уравнений Фредгольма | 1982 |

|

SU1108444A1 |

| Многоканальное устройство дляРЕшЕНия СиСТЕМ лиНЕйНыХ АлгЕбРАичЕС-КиХ уРАВНЕНий | 1978 |

|

SU807318A1 |

| Устройство для решения интегральных уравнений Фредгольма второго рода | 1988 |

|

SU1617438A1 |

Авторы

Даты

1981-03-15—Публикация

1978-12-05—Подача