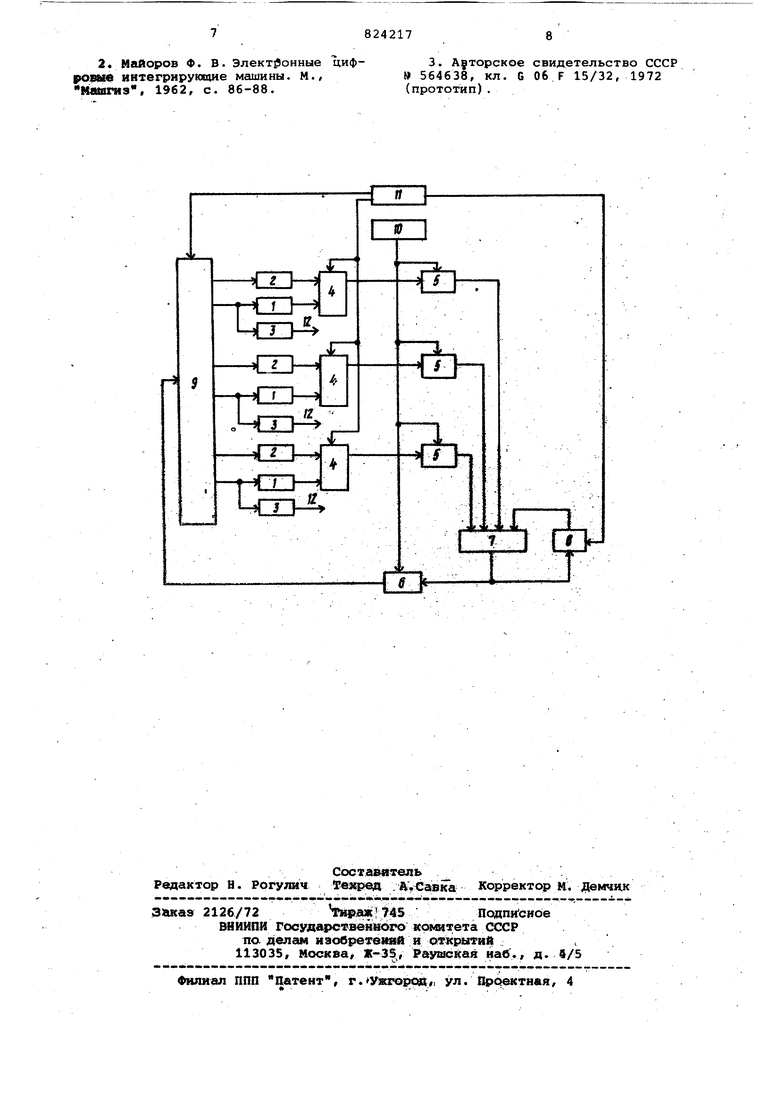

...... . Изобретение относится к .вычислите льно.й технике и может быть использовало при построении специализиро-ванных и проблемно-ориентированных вычиелительн з1Х машин и. комплексов. Известно устройство для моделироВания обыкновенных дифференциальных уравневий-, содержащее цифровой блок аналоговые запоминающие устройства, два суммирунидих .усилителя с цифровы ми уйрабляёмиии сопротивлениями во входййк цепях/Это устройство исполь зуют для рещения систем линейных алребраичёских: .уравненнй (СЛАУ), которые, предварятель но преобразуются в эквивалентну систему линейных дифференциаяьн1лх уравнений ul Недостача .этого устройства является визкая ;тОчнос ь решения СЛАУ, обусловлевная ограниченной то ностью аналоговых блоков, и большое время решения задач- из-за большой инерционности интеграторов, нео ходимой для обеспечения .устойчивости процесса решения. Известно устройство для решения СЛАУ, содержащее группы суьшаторов приращений, регистров приращений |и сумматор, групп входов которого (соединена с выходами- соответс.твуМда регистров приращения, входы Которых соединены со входами сумматоров П риращения, выходы которых соединены с выходами устройства И. Недостаткаида этого устройства являются большой объем оборудования, поскольку при решении СЛАУ п-го порядка в устройстве используется узлов умножения приращений, п интеграторов и п сумматоров На п+1 входах, большое время решения из-за инерционности, вносимой интеграторами, и трудность автоматизации ввода в устройство коэффициентов решаемой си.стекнл из-за наличия большого количества узлое умножения, автома,тизация ввода информации в которые существенно усложняет блок управления устройства. Наиболее близким по технической сущносаги к предлагаемому, изобретению является устройство, содержание группы cy e iatC4poB приращений, регистров приращений неизвестных и блоков.умнхжения приращени и, сумма тор, группа входов которого соединена с выходами блоков умножения приращений, вшсод сулнлатора через блок памяти невязок , -соединен со своим входом и через блок .умножения невязок - с первым входом коммутатора, выходы которого соедине на со входами регистра приращений не известных и входами сумматоров приращений, выходы которых соединены с выходами устройства, выходы- блока управления соединены сО вторыми входами коммутатора и. блока памяти невя зок, а также со входом блока памяти коэффициентов, выходы которого соеди нены со вторыми входами блоковумнож ния приращений и вторым входом блока угдножения невязок-, Устройство работает следуккцим Образом. В исходного состоянии коэффициенты а системы управлений a..t,,. у it-t.n записаны в блоке памяти коэффициентов, а значения свободных членов Ьсодержатся с блоке- памяти невязок. Начальные значения неизвестны x;j (йЬ: sO заносятся в сумматоры приращений. Каждая К-ая итерация вычислений состоит из циклов по числу строк решаемой системы уравнений (1). В цикле осуществляется выда-ча коэффициентов а( Г7гГ) из блока памяти коэффициентов на вторые входы блоков умножения приращений, на первые входы которых прступают приращения неизвестных4х П с ре|гистров .приращений. Результаты произведений С выходов j-тых блоков умножения приращений поступают на выхо да сумматора 5, на другой вход которого подается значение 1-ой навязки на предьздуией итерации с выхода блока памяти невязок. На-выходе сумматора формируется новое значение 1-ой невязки Е , которое запоминается в блоке памяти невязок, и пос тупает на второй вход блока умнржекия невязок, на первый вход котороп с выхода блока памяти коэффициентов подается значение Hj , определяющее абсолютную величину приращения неиз вестной , знак которого соответствует знаку невязки Ef . По..лученное на выходе блока умножения иевязок значение приращения неизвест ного подается через коммутатор 8 на вход -го регистра ириращеНИИ 1, где запоминаетея, и на вход i-ro сумматора приращения 2, в ко-TQpoM форми-руетея полное значение ис комой неизвестной . В рассматриваемом устройстве реа.п лизуется одна из модификаций метода простой итерации, который сходится в том случае, если коэффиод1енты матрищл решаемой СЛйУ удовлетворяют еле дукядим УСЛОВИЯМ I , т.е. диагональные коэффициенты по аб солютной величине больше суммы модулей всех остальных коэффициентов в строке или в столбце Гз} ... Однако имеется широкий класс важных научно-технических задач, которые сводятся к СЛАУ с матрицей, коэффициентов, не удовлетворяющие привед-енным ограничениям. Такие задачи, не возможно решить с.помощью язнестного .устройства. Цель изобретения - расширение функциональных возможностей за счет обеспечейия решения класса задач, не удовлетворяющих условию, когда диагональные коэффйциенты по абсолютной величине не больше суммы модулей всех остальных коэффициентов в строке или столбце. Поставленная цель дост гается тем, что в устройство, содержащее сумМаторы приращений, регистры прираще.ний неийвестны.х, блоки умножения приращений, сумматор, группа входов которого Соединена с выходами блоков умножения приращений, выход.сумматора .через блок памяти невязок- соединен со своим входом и через блок умножеяия невязок,- подключен ко.входу коммутатора, выходы которого соединены соответственно со входами регистров приращений неизвестных и с входами сумматоров приращений, вЭходы к.отоPfjx являются выходами устройс тва, упра влякмаие входы коммутатора и блока памяти невязок соединены соответственно с первым и вторым-выходами блока управления, третий выход которого соединен С; входом блока памяти коэффициентов, выход которого подключен к первым входам блоков умножения прирайений и к входу блока умножения невязок, введены переключатели и регистры приращений невязок, входы которых соединены соответственно с выходами коммутатора, .информационные входы каяедого переключателя соединены с выходами соответствующих регистров приращений неизвестных и приращений иеряэок, управляклций вход каждого переключателя соединен с четвертым ааходом блока управления, а выход .-« подклюнен ко второму входу соответствующего блокс1 умножения приращеиий. - .. На чертеже представлена схема предлагаемого устройства. Устройство содержит регистры 1 приращений неизвестных« регистры 2 приращений невязок, суАшаторы 3 приращений, пербшоочатели 4, блоки 5. умножения приращений, блок 6 умножения невязок, сумматор 7, блок 8 памяти невязок, коммутатор 9, блок 10 памяти коэффициентов, блок 11 управления и выходы 12 устройства. . Устройство работает следующим образом. В исходном состоянии коэффициенты решаемой системы уравнений записаны в блоке Ю памяти коэффициентов, а значения свободных членов содержатся я -8 памяти невязок.

Начальные значения искомых неизвестных х(0)0 заносятся в сумматор 3 приращений.

Каждая итерация вычислений состоит из числа циклов, в два раза больших числа строк решаемой СЛАУ. В -том цикле первой группы циклов () осуществляется выдача коэффициентов из блока 10 памяти коэффициентов на входы блоков 5 умножения .приращений, на другие входы которых через переключатели 4 поступают приращения неизвес.тных с регистров 1 приращенийнеизвестных. Резу/1ьтаты произведений с выходов блоков 5 умножения приращений поступают на входы сумматора 7,. на другой вход которого подается значение i-той невязки на предьщущей итерации Е . с выхода блока 8 памяти невязок. На выходе сумматора 7 формируется новое значение t-той невязки, которое запоминается в .блоке 8 памяти невязок и поступает на вход блока б умножения невязок, на другой вход которого с выхода блока 10 памяти коэффициентов подается значение Hj, определяющее.абсолютную величину приращения Невязки , знак которого равен знаку соответствующей невязки . В зависимости от значения шага приращения, в блоке б умножения невязок производится формирование одноразрядного или несколькоразрядного приращения у( . Значение шага приращения зависит .от класса решаемых устройством задач и от реализуемого в устройстве метода решения СЛАУ.

Полученное на выходе блока б умножения невязок значение прирасдение невязки подается через коммутатор 9 на вход i-го регистра 2 приращений невязок, где оно запоминается Аналогично в i+1 цикле формируется приращение невязки .

В п+ i цикле второй группы циклов (,n) осуществляется выдача коэф фицие нтов из блока 10 памяти- коэффициентов на входы блоков 5 умножения приращений, на другие входы которых через переключатели 4 поступают приращения невязок с регистров 2 приращений невязок. Результаты произведений с выходов -тых блоков 5 умножения приращений поступают на входы сумматора 7f на выходе которого фсмируется значение Yi+t-oft невязк которое поступает на вход блока б умножения невязок. На другой вход блока б умножения невязок . подается значение шага приращения, в соответствии с которым производится формирование приращения неизвестной, которое подается через коммутатор 9 на вход i-ro регистра 1 приращений неизвестных/ где оно запоминается, и на вход i-ro сумматора 3 приращений, в котором формируется полное значение искомой неизвестной и выдается на выходы 12 устройства. Обычно функция формирования приргицения Н () в.ыбирается такой, чтобы упростить устройство и повысить е его быстродействие.,Так, например, если выбрать H.j (Е.) , где р - разрядность представления .чисел в устройстве) , то блоки умножения приращений значительно упрощаются

«и 1 ревращаются в группы элементов И, через которые, в зависимости от знаков соответствующих невязок, передаются коэффициенты на входы сложения или вычитания сумматора 7. Однако для некоторых специальных

5 классов задач приращения л х. и,

выбираются двух- и более разрядными, что несколько усложняет блоки 5 умножения приращений и снижает бы. стродействие устройства.

0

Формула изобретения

Устройство для решения систем

5 линейных алгебраических уравнений, содержащее сумматору приращений, регистры приращений нейзв.естных, блоки умножения приращений, сумматор, входы которого соединены соответственно с выходами блоков умножения

0 приращений, сумматора через блок памяти невязок соединен со своим входом и через блок умножения невязок - подключен ко входу коммутатора, выходы которого соединены со5ответственно со входами регистров приращений неизвестных и с входами сумматоров приращений, выходы которых являются выходами устройства, управляющие входы коммутатора и блока памяти навязок-соединены соответственно с первым и вторым выходами блока управления, третий выход которого соединен со входом блока памяти коэффициентов, выход которого подклю5 ,чен к первым входам блоков умножения приращений и к входу блока умно1жения невязок, отличающее с я тем, что, с целью расширения :класса решае1 й1х задач, в него введеQ ны переключатели и регистры приращений невязок, входы которых соедине,ны соответственно с выходами коммутатора, информационные входы каждого переключателя соединены с выходами соответствующих регистров приращений

неизвестных и приращений невязок, управляющий вход каждого переключателя соединен с четвертым выходом блока управления, а выход - подключен ко второму входу соответствующего блока умножения приращений.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР 5 307404, кл. G 06 F 15/32, 1969.

2. Майоров Ф. В. Электронные цифивтегрирукхцие машины. М.,

М«югиз, 1962, с. 86-88.

3. Авторское свидетельство СССР 564638, кл. G 06 F 15/32, 1972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения систем линейных алгебраических уравлений | 1972 |

|

SU564638A1 |

| Устройство для решения систем ли-НЕйНыХ уРАВНЕНий | 1978 |

|

SU813446A1 |

| Устройство для решения системлиНЕйНыХ уРАВНЕНий | 1979 |

|

SU830396A1 |

| Многоканальное устройство для реше-Ния иНТЕгРАльНыХ уРАВНЕНий | 1979 |

|

SU840921A1 |

| Многоканальное устройство дляРЕшЕНия СиСТЕМ лиНЕйНыХ АлгЕбРАичЕС-КиХ уРАВНЕНий | 1978 |

|

SU807318A1 |

| Устройство для решения системлиНЕйНыХ уРАВНЕНий | 1978 |

|

SU798862A1 |

| Устройство для решения интегральных уравнений Фредгольма | 1982 |

|

SU1108444A1 |

| Устройство для решения интеграль-НыХ уРАВНЕНий | 1979 |

|

SU817726A1 |

| Устройство для решения интегральных уравнений Фредгольма второго рода | 1988 |

|

SU1617438A1 |

| Устройство для решения системы ли-НЕйНыХ АлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU811276A1 |

Авторы

Даты

1981-04-23—Публикация

1978-11-16—Подача