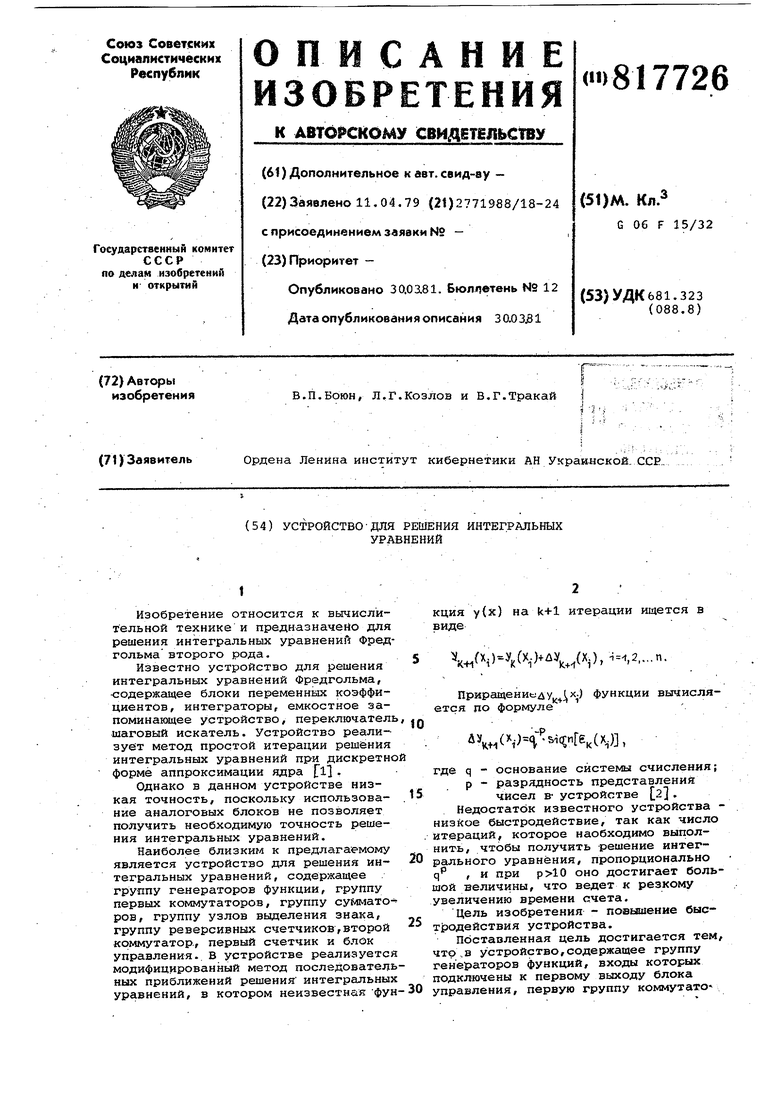

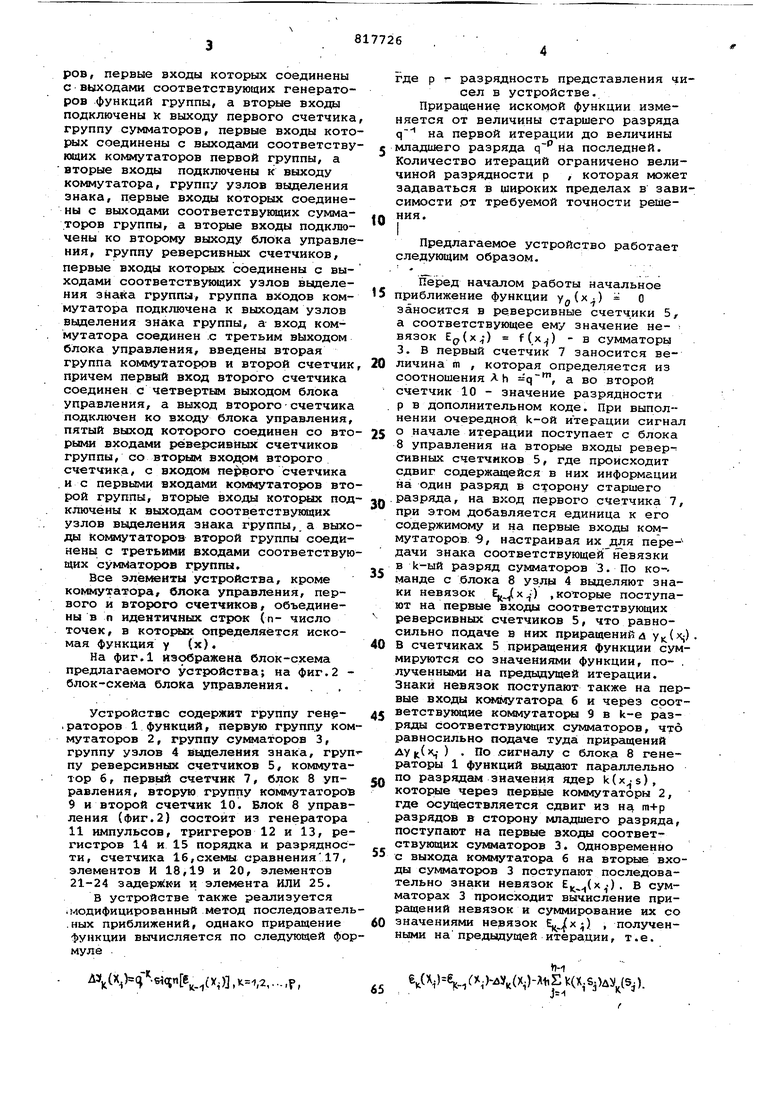

. . Изобретение относится к вычислительной технике и предназначено для решения интегральных уравнений Фредгольма второго рода. Известно устройство для решения интегральных уравнений Фредгольма, -содержащее блоки переменных коэффициентов, интеграторы, емкостное запоминающее устройство, переключатель шаговый искатель. Устройство реализует метод простой итерации решения интегральных уравнений при дискретно форме аппроксимации ядра Д1. Однако в данном устройстве низкая точность, поскольку использование аналоговых блоков не позволяет получить необходимую точность решения интегральных уравнений. Наиболее близким к предлагаемому является устройство для решения интегральных уравнений, содержащее группу генераторов функции, группу первых коммутаторов, группу суммато ров, группу узлов выделения знака, группу реверсивных счетчиков,второй коммутатор., первый счетчик и блок управления.. В устройстве реализуется модифицированный метод последователь ных приближений решения интегральных уравнений, в котором неизвестная фун кция у(х) на k+1 итерации ищется в виде )-yKfN 4.) 2-- Приращение;дУ| |Х) функции вычисляется по формуле л,/х.)-% с5пГе(х.), где q - основание системы счисления; р - разрядность представления чисел в- устройстве 2 J . Недостаток известного устройства низкое быстродействие, так как число итераций, которое наобходимо выполнить, чтобы получить решение интегрального уравнения, пропорционально q , и при оно достигает большой величины, что ведет к резкому увеличению времени счета. Цель изобретения - повышение быстродействия устройства. поставленная цель достигается тем, что .в устройство,содержащее группу генераторов функций, входы которых подключены к первому выходу блока управления, первую группу коммутато ров, первые входы которых соединены с выходами соответствующих генераторов функций группы, а втоЕиле входы подключены к выходу первого счетчика группу сумматоров, первые входы кото рых соединены с выходами соответству кядих коммутаторов первой группы, а вторые входы подключены к выходу коммутатора, группу узлов выделения знака, первые входы которых соединены с выходами соответствунэдих сумматоров группы, а вторые входы подключены ко второму выходу блока управле ния, группу реверсивных счетчиков, первые входы которых соединены с выходами соответствующих узлов выделения знака группа, группа входов коммутатора подключена к выходам узлов вьщеления знака группы, а вход коммутатора соединен .с третьим выходом блока управления, введены вторая группа коммутаторов и второй счетчик причем первый вход второго счетчика соединен с четвертым выходом блока управления, а вых:од второго счетчика подключен ко входу блока управления, пятый выход которого соединен со вто рыми входами реверсивных счетчиков группы, со вторым входом второго счетчика, с входом первого счетчика .и с первыми входами коммутаторов вто рой группы, вторые входы которых под ключены к выходам соответствующих узлов вьзделения знака группы, а выхо ды Колмутаторов второй группы соединены с третьими входами соответствую щих сумматоров группы. Все элементы устройства, кроме коммутатора, блока управления, первого и второго счетчиков, объединены в п идентичных строк (п- число точек, в которак определяется искомая функция у (х). На фиг.1 изображена блок-схема предлагаемого устройства; на фиг.2 блок-схема блока управления. Устройстве содержит группу гене.раторов 1 функций, первую группу ком мутаторов 2, группу сумматоров 3, группу узлов 4 выделения знака, груп пу реверсивных счетчиков 5, коммутатор 6, первый счетчик 7, блок 8 управления, вторую группу коммутаторов 9 и второй счетчик 10. Блок 8 управления (фиг.2) состоит из генератора 11 импульсов, триггеров 12 и 13, ре гистров 14 и 15 порядка и разряднос ти, счетчика 16,схемы сравнения17, элементов И 18,19 и 20, элементов 21-24 Зсщержки и элемента ИЛИ 25. В устройстве также реализуется .модифицированный метод последовател .ных приближений, однако приращение функции вычисляется по следующей фо муле A(X,).(X.),,...,f, де р г разрядность представления чисел в устройстве. Приращение искомой функции измеяется от величины старшего разряда на первой итерации до величины ладшего разряда q На последней. оличество итераций ограничено велииной разрядности р , которая может задаваться в широких пределах в зависимости от требуемой точности решеНИЯ. Предлагаемое устройство работает следующим образом. Перед началом работы начальное риближение функции у.(х-) о заносится в реверсивные счетч.ики 5,. а соответствующее ему значение невязок Ер() f(x) - в сумматоры 3. В первый счетчик 7 заносится величина m , которая определяется из соотношения Я h , а во второй счетчик 10 - значение разрядности р в дополнительном коде. При выполнении очередной k-ой итерации сигнал о начале итерещии поступает с блока 8 управления на вторые входы реверсивных счетчиков 5, где происходит сдвиг содержащейся в них информации на один разряд в С орону старшего разряда, на вход первого счетчика 7, при этом добавляется единица к его содержимому и на первые входы коммутаторов. 9, настраивая их передачи знака соответствующейневязки в k-ый разряд сумматоров 3. По ко-. манде с блока 8 узлы 4 выделяют знаки невязок ЕК-/ .которые поступают на первые входы соответствующих реверсивных счетчиков 5, что равносильно подаче в них приращений д у (х;) . В счетчиках 5 приращения функции суммир5ются со значениями функции, по- . лученными на предыдущей итерации. Знаки невязок поступают также на первые входы кс шутатора б и через соответствующие коммутаторы 9 в k-e разряды соответствующих сумматоров, что равносильно подаче туда приращений ду ц( S ° .сигналу с блока 8 генераторы 1 функций выдают параллельно по разрядам значения ядер k(x. s), которые через первые коммутаторы 2, где осуществляется сдвиг из на т+р разрядов в сторону младшего разряда, поступают на первые входы соответствующих сумматоров 3. Одновременно с выхода кс««мутатора б на вторые входы сумматоров 3 поступают последовательно знаки невязок Е,(х.). в сумматорах 3 происходит вычисление приращений невязок и суммирование их со значениями невязок Е.х;;) , полученными напредыдущей итерации, т.е. &к(().S.)дy5). После окончания k-ой итерации в реверсивных счетчиках 5 содерйсатся зн чения функции У(;.(), а на выходах сумматоров 3 - значения соответствующих невязок Е,(х). Последующие итерации выполняются аналЬг-ично.После выполнения р-ой, последней итерации, сигнал переполнения второго счетчика 10 поступает в блок 8 управ ления, который выдает команду на окончание работы. Блок 8 управления работает следующим образом. Сигнал Начальная устй11овка, поступающий на элемент И 20, осуществляет передачу дополнительного кода величины разрядности р с регистра 15 на первый вход второго счетчика 10 и устанавливает триггер 13 в состояние, открывающее элементИ 19, подготавливая схему к работе. Сигнал Запуск (начало первой итерации) через элементы ИЛИ 25, И 1 поступает на вторые входы реверсивных счетчиков 5, вход первого счетчика 7, первые входы кo 1yтaтopoв 9 и второй вход счетчика 10. Через эле мент 21 задержки задержанный сигнал поступает на вторые входы узлов 4 выделения знака и через элемент 22 задержки на триггер 12, которлй открывает элемент И 18. Сигналы от генератора 11 импульсов поступают-на входы генераторов 1 функций, счетчик 16 .и через элемент 23 задержки на второй вход коммутатора 6 до тек пор пока схема 17 сравнения, которая сра внивает величину порядка п , содер-: жащуюся в регистре 14, с количеством поступивших на счетчик 16 импульсов, не выдает сигнал на триггер 12, кото рый закрывает элемент И 18, тем самым заканчивая итерацию. Сигнал со схемы 17 сравнения через элемент задержки 24 поступает на элемент ИЛИ 25, начиная следуницую итерацию, и т.д. После выполнения р-ой, последней, итерации сигнал переполнения второго счетчика 10 поступает на три гер 13, который запирает элемент И 1 останавливая работу блока управления и всего устройства. Многообразие практических задач, опис ывае1лых интегральньйви уравневида и, определяет актугшьность предлагаемого устройства. Оно можеФ работать как сшлостоятельное вычислительное устройство, так и в комплексе с универсальной циф ЕЮвой вычислитель ной Мсцщзной. Устройство может найти ширюкое применение в научных исследованиях, в электро-и радиотехнической промышленности, строительной механике и Оборонной промышленности страны. Формула изобретения Устройство для решения интегральных уравнений, содержащее группу генераторов функций, входы которых подключены к первому выходу блока управления, первую группу коммутаторов, первые входы которых соединены с выг ходами соответствующих ге,нераторов функций группы, а вторые входы подключены к выходу первого счетчика, руппу сумматоров, первые входы которых соединены с выходами соответствукщих коммутаторов первой группы, а вторые входы подключены к выходу коммутатора,группу узлов выделения знака,первые входы которых соединены с выходами соответствующих сумматоров группы, а вторые входы подключены ко второму выходу блока управления, группу реверсивных счетчиков,первые входы которых соединены с выходами соответствукмцих узлов выделения знака группы, группа входов коммутатора подключена .к выходам узлов вьщеления знака групгал, а вход коммутатора соединен с третьим выходом блока управления, отличающееся тем, что, с целью повьппения быстродействия, в него введены вторая группа коммутаторов и второй счетчик, причем первый вход второго счетчика соединен с четвертым выходом блока управления, а выход второго счетчика подключен ко входу блока управления, пятый выход которого соеди-нен со вторыми входами реверсивных счетчиков группы, со вторым входом второго счетчика, с входом первого счетчика и с первыми входами коммутаторов второй Группы, вторые входы которых подключены к выходам соответствуюих узлов выделения знака группы, а выходы коммутаторов второй группы соединены с третьими входами соответствующих сумматоров группы. Источники информации принятые во внимание при экспертизе 1.Верлань А.Ф. Методы решения интегральных уравнений на ангшоговых вычислительных машинах. К., Наукова думка, 1972, с.161,163, рис.111, 112. 2.Авторское свидетельство СССР о заявке № 2599160/18-24, л.б 06 J 1/02, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для реше-Ния иНТЕгРАльНыХ уРАВНЕНий | 1979 |

|

SU840921A1 |

| Устройство для решения интегральных уравнений Фредгольма второго рода | 1988 |

|

SU1617438A1 |

| Устройство для решения интегральных уравнений Фредгольма | 1982 |

|

SU1108444A1 |

| Устройство для решения интегральных уравнений Фредгольма второго порядка | 1985 |

|

SU1295413A1 |

| Устройство для решения интегральных уравнений | 1978 |

|

SU687452A1 |

| Устройство для решения систем линйныхАлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU824217A1 |

| Устройство для решения систем ли-НЕйНыХ уРАВНЕНий | 1978 |

|

SU813446A1 |

| Резервированное устройство для решения интегральных уравнений | 1981 |

|

SU1092511A1 |

| Многоканальное устройство дляРЕшЕНия СиСТЕМ лиНЕйНыХ АлгЕбРАичЕС-КиХ уРАВНЕНий | 1978 |

|

SU807318A1 |

| Устройство для решения системлиНЕйНыХ уРАВНЕНий | 1979 |

|

SU830396A1 |

Авторы

Даты

1981-03-30—Публикация

1979-04-11—Подача