(54) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ИНТЕГРАЛЬНЫХ УРАВНЕНИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство дляРЕшЕНия СиСТЕМ лиНЕйНыХ АлгЕбРАичЕС-КиХ уРАВНЕНий | 1978 |

|

SU807318A1 |

| Устройство для решения интегральных уравнений Фредгольма второго порядка | 1985 |

|

SU1295413A1 |

| Устройство для решения интегральных уравнений Фредгольма второго рода | 1988 |

|

SU1617438A1 |

| Устройство для решения интеграль-НыХ уРАВНЕНий | 1979 |

|

SU817726A1 |

| Устройство для решения интегральных уравнений Фредгольма | 1982 |

|

SU1108444A1 |

| Устройство для решения систем ли-НЕйНыХ уРАВНЕНий | 1978 |

|

SU813446A1 |

| Устройство для решения системлиНЕйНыХ уРАВНЕНий | 1979 |

|

SU830396A1 |

| Устройство для решения системлиНЕйНыХ уРАВНЕНий | 1978 |

|

SU798862A1 |

| Устройство для решения систем линйныхАлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU824217A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1978 |

|

SU746534A1 |

I

Изобретение относится к вычислительной технике и предназначено для решения интегральных уравнений Фредгольма второго рода.

Известно устройство для решения интегральных уравнений редгольма второго рода, состоящее из интеграторов и следящих интеграторов и решающее интегральные уравнения методом последовательных итераций иЗ

Недостатками устройства являются низкое быстродействие из-за обхода области интегрирования посыледовательно по одной переменной, затем по другой переменной и большое количество тактов, необходимых для образования приращения функции в следящих интеграторах.

Известно устройство для решения интегральных уравнений Фредгольма, содержащее блоки переменных коэффициентов, интеграторы, емкостное запоминающее устройство, переключатель, шаговый искатель и реализующее метод простой итерации решения интегральных уравнений при дискретной форме аппроксимации ядра 2.

Недостатком устройства является низкая точность, поскольку использование аналоговых блоков не позволяет получить необходимую точность решения интегральных уравнений. При реализации алгоритма с использованием цифровых блоков интегрирования, умножения и суммирования устройство обладает большим обьемом аппаратурных затрат, обусловленным наличием сложных блоков интегрирования, умножения и блока памяти, и ограниченным классом решаемых задач, так как простые итерации сходятся к решению интегрального уравнения Лредгольма второго рода ToJibKo в том случае, если численный параметр отвечает необходимому условию.

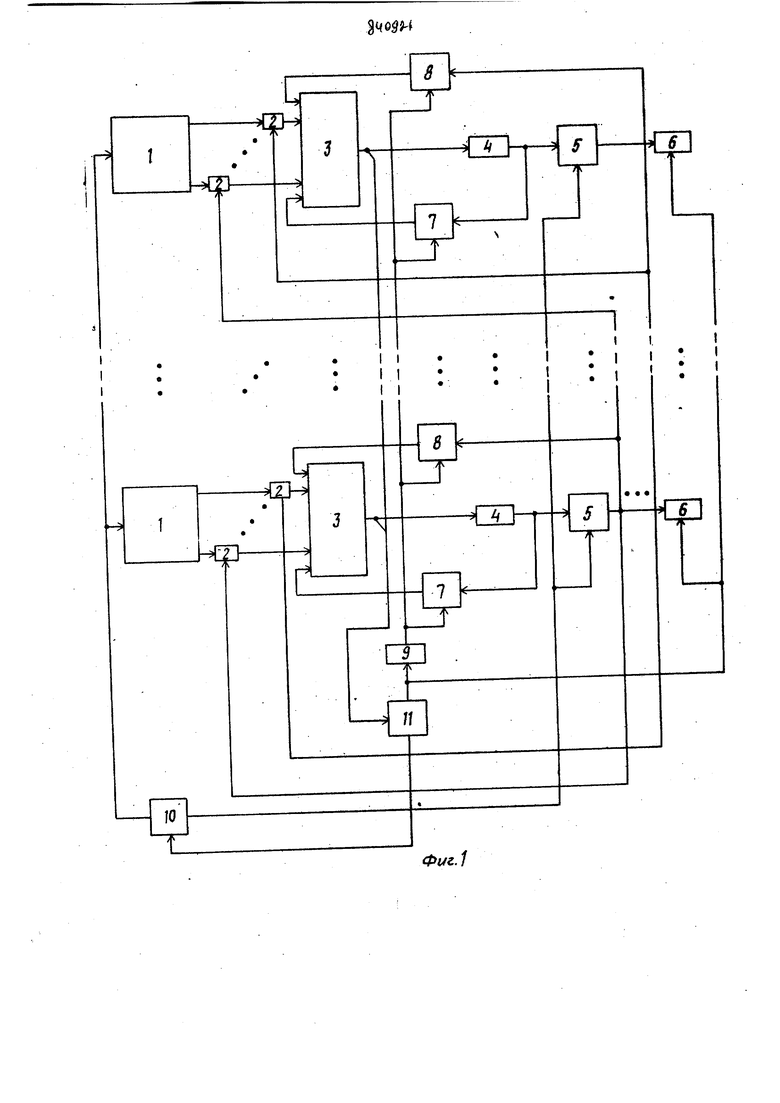

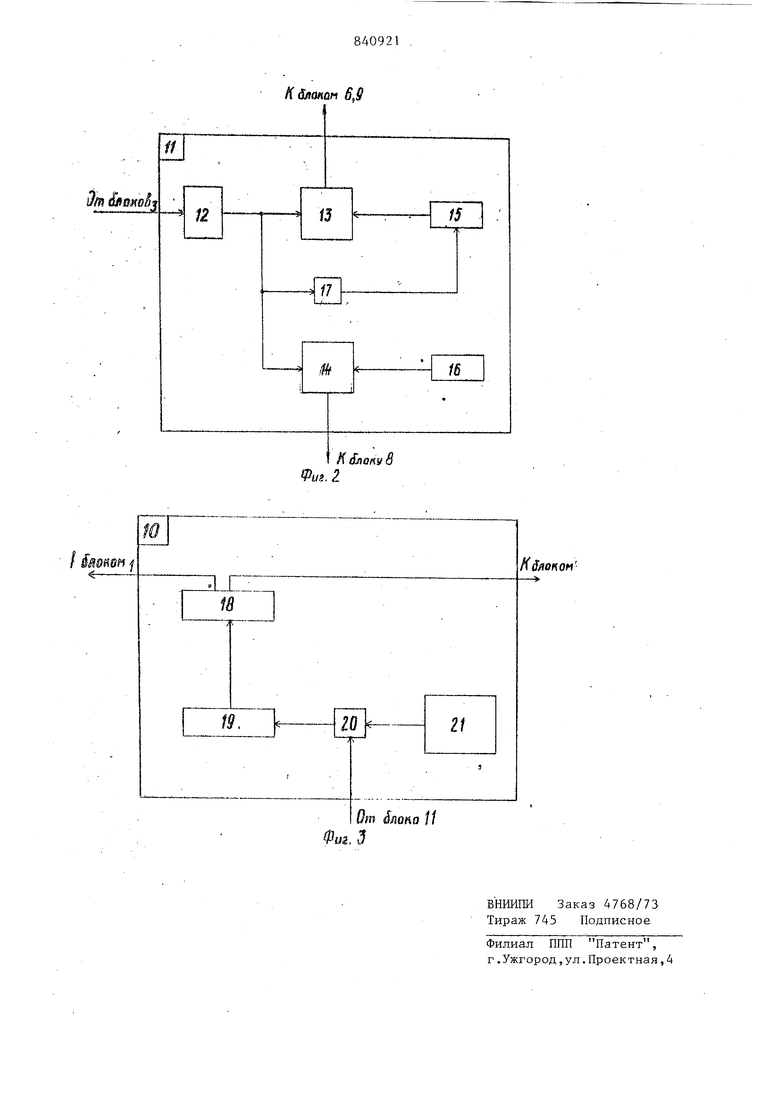

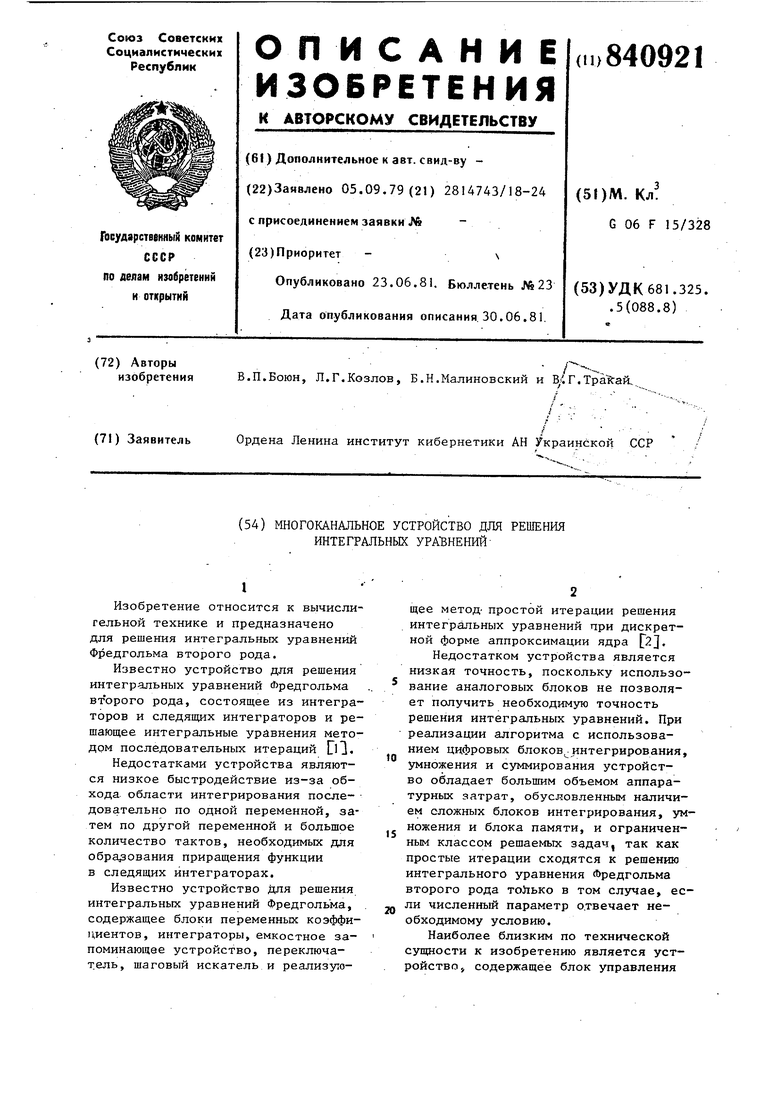

Наиболее близким по технической сущности к изобретению является устройство, содержащее блок управления .3 и в каждой .строке генератор, функции, выходы которого через группу преобразователей кода соединены с первыми входами сумматора, выход которого по ключен ко тзходу регистра иевязки, выход которого соединен с первым входо первого элемента задержки и с первым входом узла выделения знака, выход которого подключен к первому входу второго элемента задержки, к первому входу реверсивного счетчика и к управляющим входам преобразователей кода всех строк, вход генератора фун ции каждой строки соединен с первым выходом блока управления, второй выход которого соединен со вторым вход узла выделения знака каждой строки, выход первого элемента задержки соединен со вторым входом сумматора, третий вход которого подключен к выходу второго элемента задержки. В устройстве реализуется модифицированный метод последовательных приближений решения интегральных уравнений, в котором неизвестная функция на к+1 итераций ищется в дискретных точках (j3j. Недостатком известного устройства является низкое быстродействие, так как число итераций, которое необходимо вьтолнить, чтобы получить решение интегрального уравнения, пропорционально , и при р )10 оно может достигать большой величины, что ведёт .к резкому уве- лиуению времени счета, где д- - основание системы счисления, р - разрядность представления чисел. Цель изобретения - п; овьппение быст :родействия устройства. Поставленная цель достигается тем, что в многоканальное устройство для решения интегральных уравнени содержащее блок упрайления и в каждом канале генератор функции, выходы которого подключены соответственно к входам шифраторов кода, выходы которых соединены с первой группой входов сумматора, выход которого под ключен ко входу регистра невязки, выход которого соединен с первыми вх дами первого элемента задержки и узла вьщеления знака, выход которого подключен к первым входам второго элемента задержки и реверсивного сче чика и к управляющим входам соответ ствукяцих шифраторов кода каждого ка нала, вход генератора функции каждого канала соединен с первым выходом 1 блока управления, второй выход которого соединен со вторым входом узла вьщеления знака каждого канала, выходы первого и второго элементов задержки каждого канала соединены соответственно со вторым и третьим входами сумматора каждого канала, введены счетчик и блок сравнения невязок, вход которого соединен с Выходом сумматора каждого канала, первый выход . блока сравнения невязок подключен к входу блока управления, второй выходсоединен со вторым входом реверсивного счетчика каждого канала и со входом- счетчика, выход которого подключен ко вторым входам первого и второго элементов задержки каждого канала. Блок сравнения невязок в устройстве содержит регистры, узлы сравнения, элемент задержки, и сумматор невязок, выход которого соединен с первыми входами первого и второго узлов сравнения и через элемент задержки подключен к входу первого регистра, выход которого подключен к второму входу первого узла сравнения, ВЫХОД которого является вторым выходом блока, выход второго регистра подключен ко второму входу второго узла сравнения, выход которого является первым выходом блока, вход сумматора невязок является входом блока. Блок управления содержит счетчик, дешифратор, элемент И;, генератор импульсов, выход которого соединен с первьм входом элемента И, второй вход которого является входом блока, выход элемента И соединен с входом счетчика, выход которого подключен к входу дешифратора, первый и второй выходы которого являются соответственно первым и вторым выходами блока. На фиг. 1 представлена блок-схема устройства; на фиг. 2 - схема блока сравнения невязок; на фиг. 3 в качестве примера показана схема блока управления. .Устройство содержит генераторы функции 1, шифраторы 2 кода, сумматор 3, регистр 4 невязки, узел 5 вьщеления знака, реверсивный счетчик 6, элементы 7 и 8 задержки, счетчик 9, блок 10 управления, блок 11 сравнения невязок, сумматор 12 невязок, узлы 13 и 14 сравнения, регистры 15 и 16, элемент 17 задержки, дешифратор 18, счетчик 19, элемент И 20 генератор 21 импульсов, В устройстве реализуется модифицированный метод последовательных приближений. Приращение функции вычисляется по формуле ,(. И,Ч H,ecAnCt a),(X)l, к pl U rv l : V Icr (Ч М ,..t.|t)l , 1, 2, ... ЕХ,(Х,-)Величина невязки. Начальное значение величины- приращения искомой функции равно едини це старшего разряда, В дальнейшем . на каждой итерации вычисляется сумма модулей невязок для всех точек, где вычисляется функция. Эта сумма сравнивается с такой же суммой, полученной на предьщущей итерации. Ве личина приращения в зависимости от результата сравнения этих сумм.или остается неизменной, или уменьшаетс в 9- раз. Итерационный процесс закан чивается, если выполняется условие П ..(Х,)| 4 Г , где г. - заданная точность решения и тегрального уравнения. - Устройство работает следующим об разом,. Перед началом работы начальное приближение функции заносится в реверсивные счетчики 6, а соответству ющее ему значение невязок -.в регистры невязок 4, которые имеют раз рядность 2р.В счетчик 9 заносится веЛичина т, которая определяется из соотношения g ЯН (h - шаг интегрирования) , В блок сравнения невязок 11 зaнocяtcя величины Е r3/f (х.)/ и г. При выполнении очередной итерации по сигналу с блока 10 управления узел 5 каждого канала выделяет знак невязки, которьй поступает на первый вход реверсивного счетчика 6, что равносительно подаче в не го приращения. В счетчике 6 каждого канала приращение функции суммирует ся со значением функции, полученным 16 на предыдущей итерации. Знак невязки в каждом канапе поступает через г лемент 8 задержки, на вход сумматора 3 и на управляющие входы соответствующих шифраторов 2 кода; По поманде с блЪка 10 генераторы функции 1 в каждом канале начинают выдавать параллельно значения младшими разрядами вперед. Эти значения поступают, на входы сумматоров 3 через шифраторы 2, где учитьгоаются знаки невязок, В зависимости от этих знаков значения суммируют(я или вычитаются в сумматорах 3, На вторые входы сумматоров З поступают с задержкой значения невязок, а на третьи входы - знаки Tek же невязок с задержкой. .Этим -достигается получение на выходе сумматоров 3 значений невязок, которые заносятся для хранения в соответствующие регистры невязки 4. С выхода сумматоров 3 невязки поступают также в блок 11 сравнения невязок, где происходит вычисление величины Е и сравнение ее с величинами г и Е..Если Е|,г, то итерационный процесс решения интегрального уравнения на этом заканчивается. Сигнал с блока 1I поступает в блок 10 управления, который останавливает работу устройства. При EJ, сигнал с блока 11 поступает в реверсивный счетчик 6 каждого канала, где происх®дит сдвиг содержащейся в нем информации на один разряд в сторону старшего разряда, и на счетчик 9, при этом добавляется единица к его содержимому. Соответственно увеличится на один такт величина задержки, осуществляемой элементами 7 и 8. После выполнения к-ой итерации в реверсивных счетчиках 6 содержатся значения функции, а в регистрах 4 невязок - значения соответствующих невязок. Последующие итерации выполняются аналогич но. Блок 11 сравнения невязок работает следуюш им образам. Перед началом работы в регистр 15 заносится начальная величина Е, а во второй 16 - величина г. При выполнении очередной итерации значения невязок поступают на сумматор 12, где вычисляется величина Е. Эта величина сравниваетсяв узле 14 сравнения с величиной г, которая характеризует точность решения интегрального уравнения. Если Е, г, то процесс счета заканчивается, С выхода узла 14 сигнал поступает в блок 10 ynpasления, который останавливает работу устройства.В первом узле 13 сравнения величина Е (« сравнивается с велич ной Ец, которая была вычислена на предыдущей итерации и занесена для хранения в регистр 15. При Е -, с выхода узла 13 сигнал поступает в счетчик 9 и на реверсивный счетчик 6 каждого канала, при ,игнал с выхода узла 13 не поступает. После сравнения величина Е через элемент i7 задержки заносится для хранения в регистр 15. На последующих итераци ях блок 11 работает аналогично. В блоке управления генератор 21 импульсов постоянно вырабатывает импульсы, которые через элемент И 20 поступают на счетчик 19. При нулевом состоянии счетчика 19 сигнал с д шифратора 18 поступает к узлам 5 выделения знака каждого канала, когда же в счетчике 19 код числа от 1 до р, сигналы с дешифратора 18 поступают к генераторам функции . При поступлении сигнала от блока 11 сравнения невязок на элемент И 20, последний запрещает прохождение импуль сов с генератора 21 импульсов, останавливая работу всего устройства. Формула изобретения 1. Многоканальное устройство для решения интегральных, уравнений, содержащее блок управления и в каждом канале генератор фукнции, выходы ко торого подключены соответственно к входам шифраторов кода, выходы кото рых соединены с первой группой входов сумматора, выход которого подключен ко входу регистра невязки, в ход которого соединен с первыми вхо ми первого элемента задержки и узла выделения знака, выход которого под ключен к первым входам второго элемента задержки и реверсивного счетч ка и к управляющим входам соответст ющих шифраторов кода каждого канала вход генератора функции каждого кан ла соединен с первым выходом блока управления, второй выход которого соединен со вторым входом узла выделения знака каждого каняпа, выход первого и второго элементов задержки каждого канала соединены соответ 21 ственно со вторым и третьим входами сумматора каждого канала, отличающееся тем, что, с целью повьшения быстродействия, в него введены счетчик и блок сравнения невязок, вход .которого соединен с выходом сумматора каждого канала, первый выход блока сравнения невязок подключен к входу блока управления, второй выход - соединен со вторым входом реверсивного счетчика каждого канала и со входом счетчика, выход которого подключен ко вторым входам первого и второго элементов задержки каждого канала. 2. Устройство по п. 1, отличающееся тем, что блок сравнения невязок содержит регистры, узлы сравнения, элемент задержки, и сумматор невязок, выход которого соединен с первыми входами первого и второго узлов сравнения и через элемент задержки подключен к входу первого регистра, выход которого подключен к второму входу первого узла сравнения, выход которого является вторым выходом блока, выход второго регистра подключен ко второму входу второго узла сравнения, выход которого является первым выходом блока, вход сумматора невязок является входом блока. 3. Устройство по п. 1, отличающееся тем, что блок управления содержит счетчик, дешифратор, элемент И, генератор импульсов выход которого соединен с первым входом эле мента И, второй вход которого является входом блока, выход элемента И соединен с входом счетчика, выход которого подключен к входу дешифратора, первый и второй выходы которого являются соответственно первым и вторым выходами блока. Источники информации, принятые во внимание при экспертизе 1.Майоров Ф.В. Электронные цифровые интегрирующие машины. М., Машгиз,1962, с. 105. 2.Верлань А.Ф. Методы решения интегральных -уравнений на аналоговых вычислительных машинах. Киев, 1972, с. 161, 163. 3.Авторское свидетельство СССР по заявке К 2614987/18-24, кл. G 06 F 15/32, 1978.

Фиг.1

К S/iOKuM 6,§

12

/f Апаку 6

nxz:.

/ГЛюяом

Авторы

Даты

1981-06-23—Публикация

1979-09-05—Подача