(54) ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1980 |

|

SU868973A1 |

| Цифровой синтезатор частот | 1983 |

|

SU1190457A1 |

| Цифровой генератор многочастотного сигнала | 1987 |

|

SU1499441A1 |

| СИНТЕЗАТОР ЧАСТОТ | 1997 |

|

RU2137287C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТЫ | 2022 |

|

RU2793776C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Синтезатор частот | 1983 |

|

SU1243090A1 |

| Генератор синусоидальных сигналов | 1990 |

|

SU1734189A1 |

| Цифровой синтезатор частот | 1984 |

|

SU1188845A1 |

| СИНТЕЗАТОР ЧАСТОТ | 1991 |

|

RU2007843C1 |

1

Изобретение относится к радиотехнике и может использоваться в радиопередающих и радиоприемных устройствах.

Известен синтезатор частот, содержащий последовательно соединенные первый регистр частоты, накопительный сумматор, преобразователь кодов, преобразователь код-напряжени и фильтр нижних частот, а также источник импульсов синхЕ2)низации, выход которого подключен к входу синхронизации накопительного сумматора 1.

В данном синтезаторе частот велик шаг перестройки выходной частоты.

Цель изобретения - уменьшение шага перестройки выходной частоты.

Для этого в цифровой синтезатор частот, содержаиций Последовательно соединенные первый регистр частоты, накопительный сумматор, преобразователь кодов, преобразователь код-напряжение и фильтр нижних частот, а также источник импульсов синхронизации, выход которого подключен к входу синхронизации накопительного сумматора, введены устройство вычитания кодов, компаратор кодов и второй регистр частоты, поразрядные выходы

которого соединены с первыми поразрядными входами устройства вычитания кодов и компаратора кодов, выход последнего подключен к установочному входу накопительного сумматора, поразрядные выходы которого соединены со вторыми поразрядными входами компаратора кодов и устройства вычитания к-одов, поразрядные выходы которо0го подсоединены к другим поразрядньом входам накопительного сумматора.

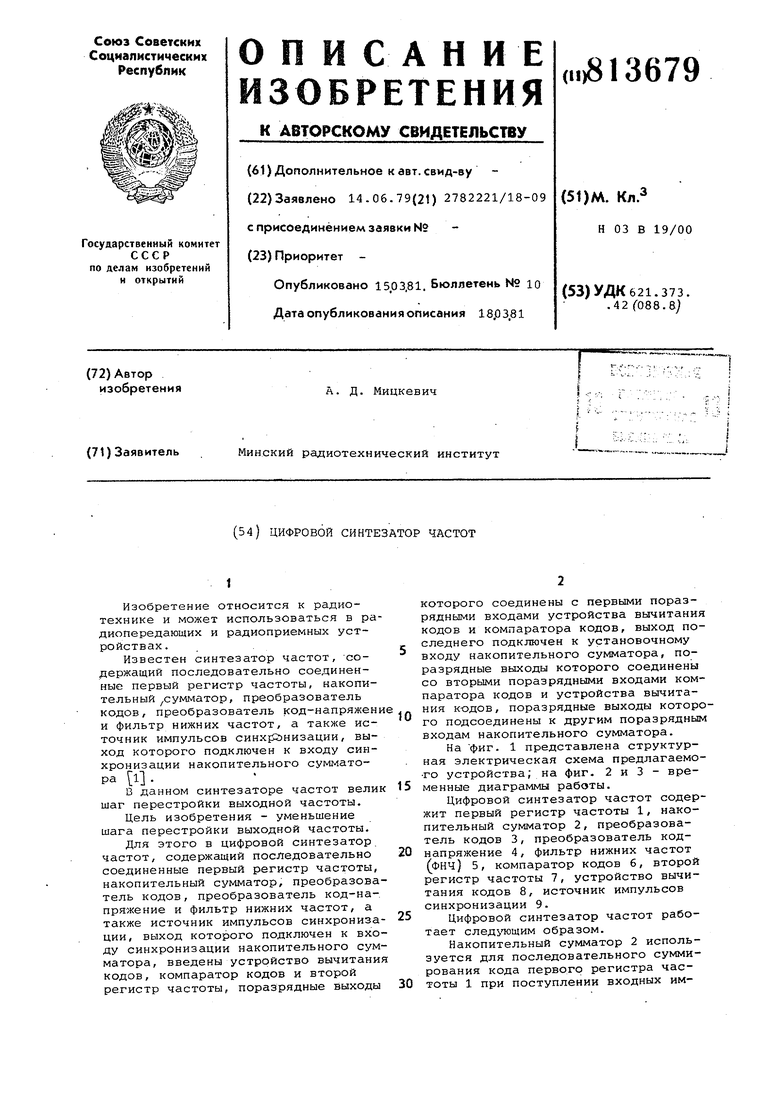

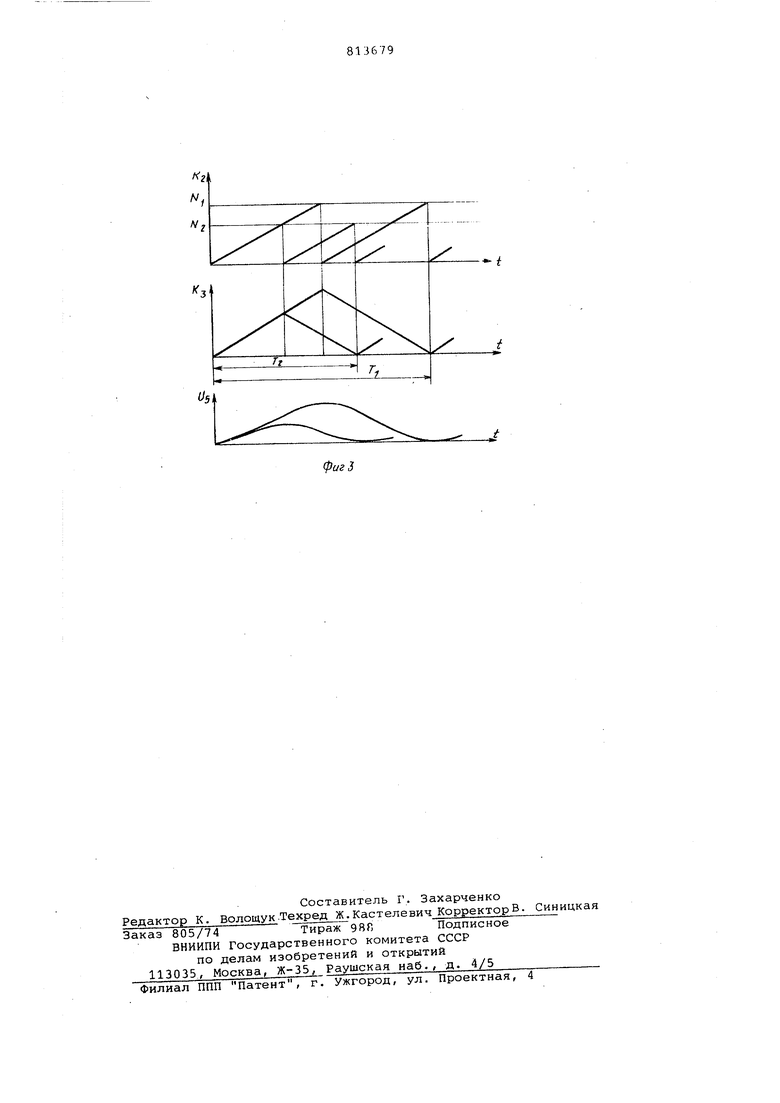

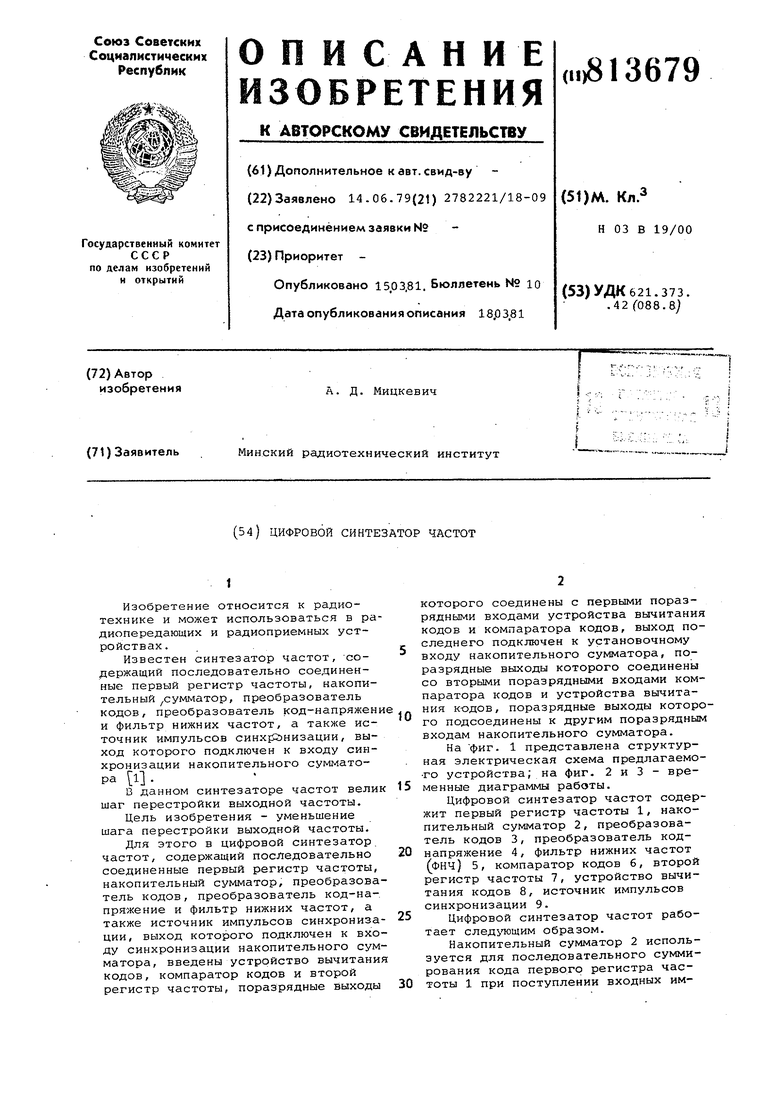

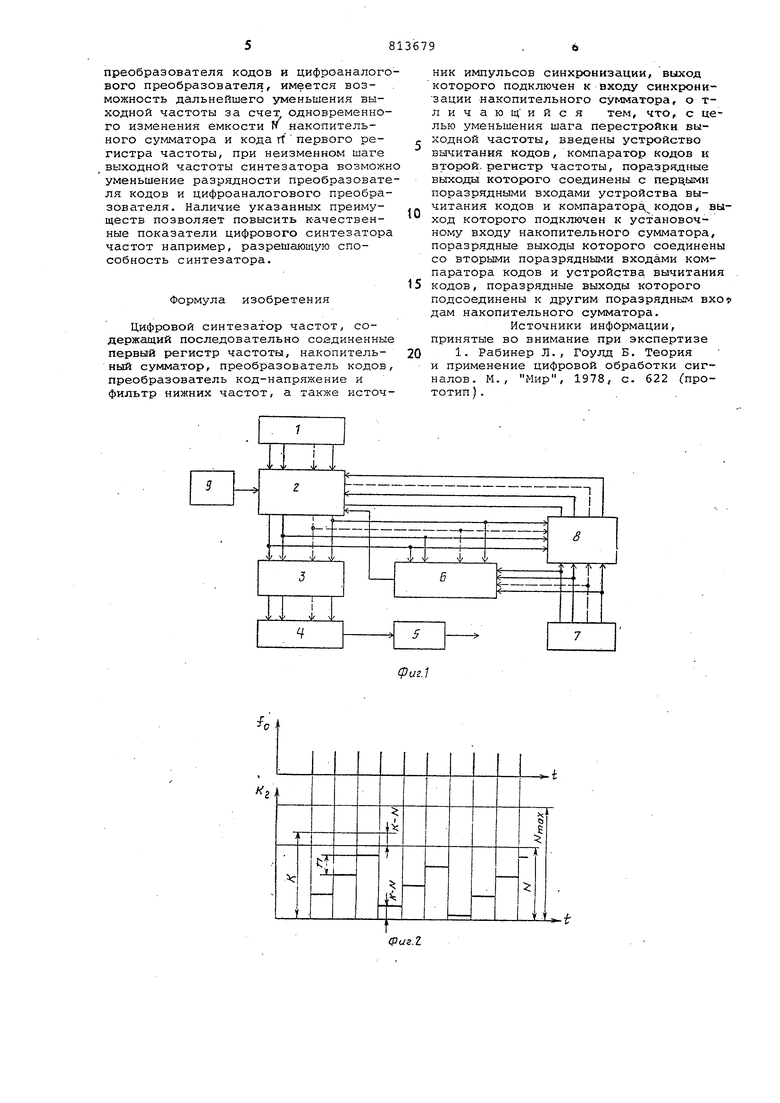

На фиг. 1 представлена структурная электрическая схема предлагаемого устройства; на фиг. 2 и 3 - вре5менные диаграммы работы.

Цифровой синтезатор частот содержит первый регистр частоты 1, накопительный сумматор 2, преобразователь кодов 3, преобразователь код0напряжение 4, фильтр нижних частот (ФНЧ) 5, компаратор кодов 6, второй регистр частоты 7, устройство вычитания кодов 8, источник импульсов синхронизации 9.

5

Цифровой синтезатор частот работает след тощим образом.

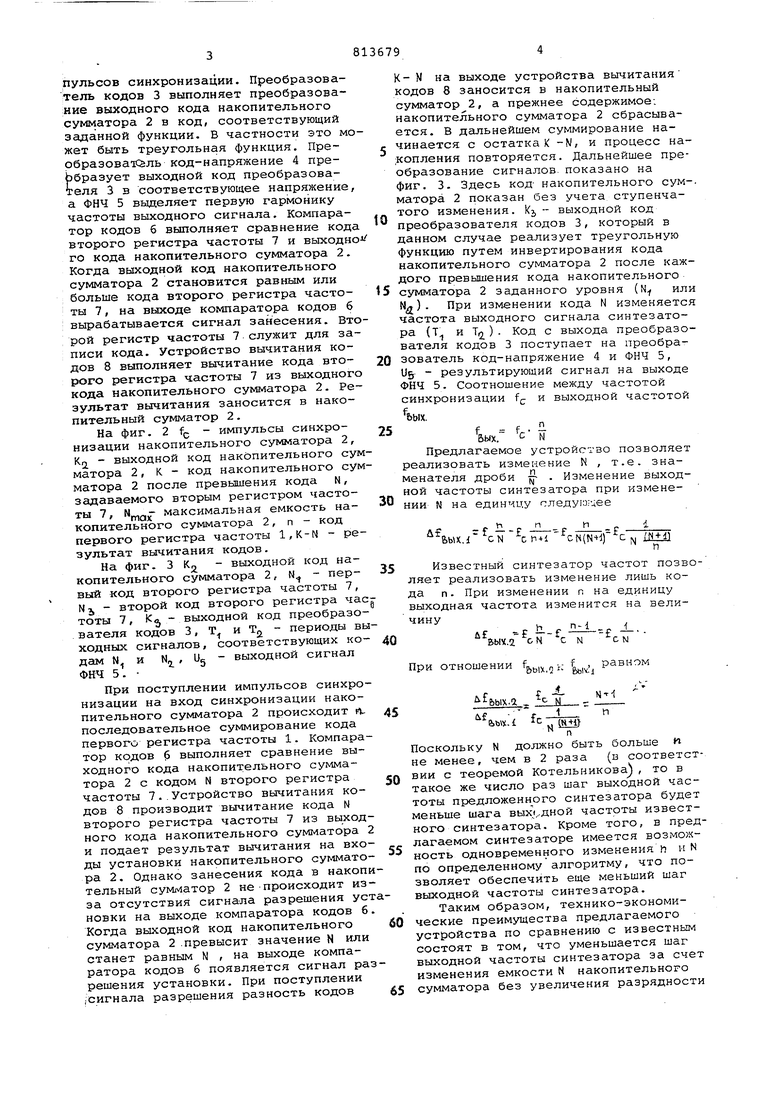

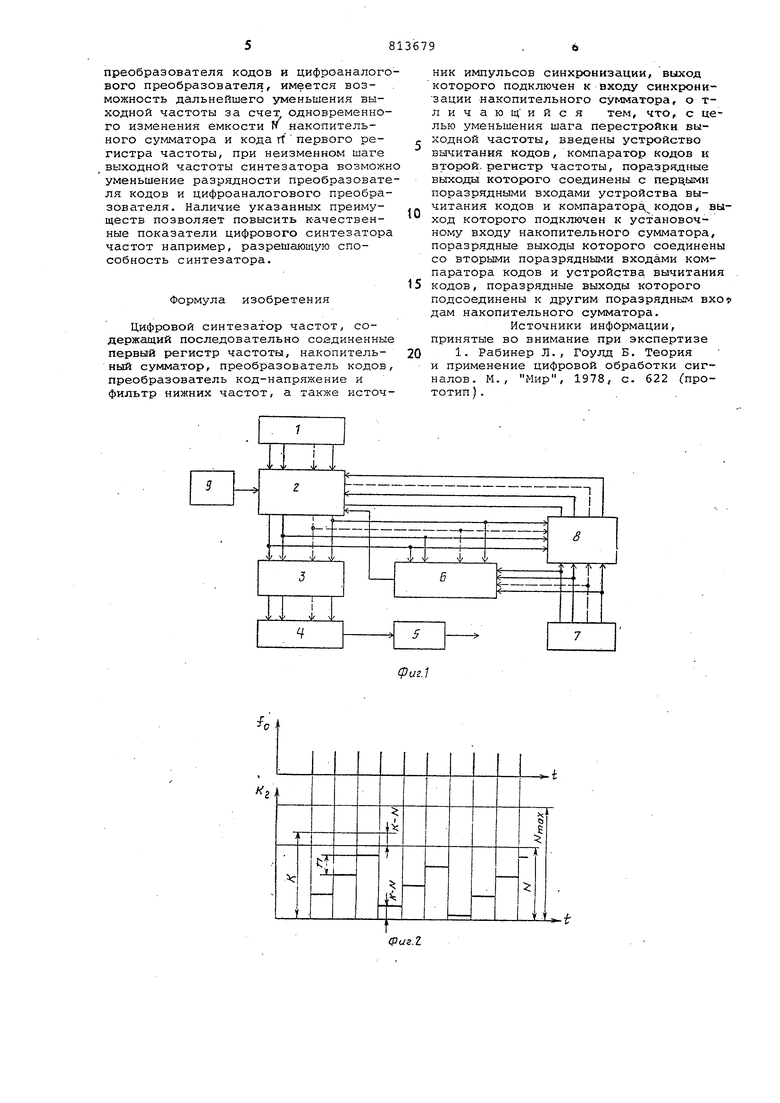

Накопительный сумматор 2 используется для последовательного суммирования кода первого регистра час0тоты 1 при поступлении входных импульсов синхронизации. Преобразователь кодов 3 выполняет преобразование выходного кода накопительного сумматора 2 в код, соответствующий заданной функции. В частности это мо жет быть треугольная функция. Преобразоватк ль код-напряжение 4 преЬбразует выходной код преобразователя 3 в соответствующее напряжение, а ФНЧ 5 выделяет первую гармонику частоты выходного сигнала. Компаратор кодов б выполняет сравнение кода второго регистра частоты 7 и выходно го кода накопительного сумматора 2. Когда выходной код накопительного сумматора 2 становится равным или больше кода второго регистра частоты 7, на выходе компаратора кодов 6 вырабатывается сигнал занесения. Вто рой регистр частоты 7 служит для записи кода. Устройство вычитания кодов 8 выполняет вычитание кода второго регистра частоты 7 из выходного кода накопительного сумматора 2. Результат вычитания заносится в накопительный сумматор 2. На фиг. 2 fp - импульсы синхронизации накопительного сумматора 2, Krj - выходной код накопительного сум матора 2, К - код накопительного сум матора 2 после превышения кода N, задаваемого вторым регистром частоты 7, Nfnar максимальная емкость накопительного сумматора 2, п - код первого регистра частоты 1,К-М - ре зультат вычитания кодов. На фиг. 3 Krj - выходной код накопительного сумматора 2, N - первый код второго регистра частоты 7, NJ - второй код второго регистра ча тоты 7, о выходной код преобразо вателя кодов 3, Т и Tj, - периоды в ходных сигналов, соответствующих ко дам N, и Ug - выходной сигнал ФНЧ 5. При поступлении импульсов синхро низации на вход синхронизации накопительного сумматора 2 происходит iv последовательное суммирование кода первого регистра частоты 1. Компара тор кодов 5 выполняет сравнение выходного кода накопит:ельного сумматора 2 с кодом N второго регистра частоты 7..Устройство вычитания кодов 8 производит вычитание кода N второго регистра частоты 7 из выход ного кода накопительного сумматора и подает результат вычитания на вхо ды установки накопительного суммато ра 2. Однако занесения кода в накоп тельный сумматор 2 не происходит из за отсутствия сигнала разрешения ус новки на выходе компаратора кодов б Когда выходной код накопительного сумматора 2 .превысит значение N или станет равным N , на выходе компаратора кодов б появляется сигнал ра решения установки. При поступлении (Сигнала разрешения разность кодов К- N на выходе устройства вычитания кодов 8 заносится в накопительный сумматор 2, а прежнее содержимое: накопительного сумматора 2 сбрасывается. В дальнейшем суммирование начинается с остатка К -N, и процесс накопления повторяется. Дальнейшее преобразование сигналов, показано на фиг. 3. Здесь код- накопительного сум-. матора 2 показан без учета ступенчатого изменения. Kj - выходной код преобразователя кодов 3, который в данном случае реализует треугольную функцию путем инвертирования кода накопительного сумматора 2 после каждого превышения кода накопительного сумматора 2 заданного уровня (N., или N). При изменении кода Н изменяется частота выходного сигнала синтезатора (Т и TQ ) . Код с выхода преобразователя кодов 3 поступает на преобразователь код-напряжение 4 и ФНЧ 5, % результирующий сигнал на выходе ФНЧ 5. Соотношение между частотой синхронизации и выходной частотой f f - БЫХ. с м Предлагаемое устройство позволяет реализовать изменение N , т.е. знаменателя дроби . Изменение выходной частоты синтезатора при изменении N на единицу пледую;-дее Чм. П + 1 CN() с JU (N + 11 Известный синтезатор частот позволяет реализовать изменение лишь кода п. При изменении п на единицу выходная частота изменится на величинуИ -( -- . &ЫЧ..1 &N С При отношении IX.Q к LivJi Равном Поскольку N должно быть больше и не менее, чем в 2 раза (в соответствии с теоремой Котельникова, то в такое же число раз шаг выходной частоты предложенное го синтезатора будет меньше шага вых...дной частоты известного синтезатора. Кроме того, в предлагаемом синтезаторе имеется возможность одновременного изменения h nN по определенному алгоритму, что позволяет обеспечить еще меньший шаг выходной частоты синтезатора. Таким образом, технико-экономические преимущества предлагаемого устройства по сравнению с известным состоят в том, что уменьшается шаг выходной частоты синтезатора за счет изменения емкости N накопительного сумматора без увеличения разрядности преобразователя кодов и цифроаналого вого преобразователя, имеется возможность дальнейшего уменьшения выходной частоты за счет, одновременного изменения емкости К накопительного сугчматора и кода rf первого регистра частоты, при неизменном шаге выходной частоты синтезатора возможн уменьшение разрядности преобразовате ля кодов и цифроаналогового преобразователя. Наличие указанных преимуществ позволяет повысить качественные показатели цифрового синтезатор частот например, разрешающую способность синтезатора. Формула изобретения Цифровой синтезатор частот, содержащий последовательно соединенны первый регистр частоты, накопительный сумматор, преобразователь кодов преобразователь код-напряжение и фильтр нижних частот, а также источ ник импульсов синхронизации, выход которого подключен к входу синхронизации накопительного сумматора, о тличающийся тем, что, с целью уменьшения шага перестройки выходной частоты, введены устройство вычитания кодов, компаратор кодов и второй, регистр частоты, поразрядные выходы которого соединены с пердьгми поразрядными входами устройства вычитания кодов и компараторга, кодов, выход которого подключен к установочному входу накопительного сумматора, поразрядные выходы которого соединены со вторыми поразрядными входами компаратора кодов и устройства вычитания кодов, поразрядные выходы которого подсоединены к другим поразрядным вхо дам накопительного сумматора. Источники информации, принятые во внимание при экспертизе 1. Рабинер Л., Гоулд Б. Теория и применение цифровой обработки сигналов. М., Мир, 1978, с. 622 (прототип) .

Авторы

Даты

1981-03-15—Публикация

1979-06-14—Подача