(54) УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ п ОДНОРАЗРЯДНЫХ

ДВОИЧНЫХ чисел

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1977 |

|

SU769539A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1234831A1 |

| Устройство для суммирования @ одноразрядных двоичных чисел | 1981 |

|

SU1068932A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU932489A1 |

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| Устройство для умножения | 1978 |

|

SU763897A1 |

| Делительное устройство | 1984 |

|

SU1239711A1 |

| Делительное устройство | 1986 |

|

SU1335980A1 |

| Устройство для формирования информативных признаков при распознавании изображений | 1986 |

|

SU1361591A1 |

| ОДНОТАКТНЫЙ УМНОЖИТЕЛЬ ДВОИЧНЫХ ЧИСЕЛ | 1988 |

|

RU2012039C1 |

Изобретение относится к вычислительной технике и может найти применение в средствах связи, автоматики и телемеханике.

Известны устройства для суммирования одноразрядных двоичных чисел (параллельные счетчики), построенные с помощью одноразрядных двоичных полусумматоров или сумматоров Щ .

Наиболее близким к предлагаемому является устройство для суммирования п одйоразрядных двоичных чисел, применяемое при ускоренном умножени и представлякицее собой многокаскадную суммирующую схему из трехвходовых одноразрядных двоичных сумматоров н.

Недостатком известных устройств является невысокое быстродействие.

Цель изобретения - повышение быастродействия.

Поставленная цель достигается тем, что устройство для суьвяировани п одноразрядных двоичных чисел содержит m преобразователей двоичных кодов в унитарные коды количества единиц (т п|к,где k - количества входных шин устройства, образующих одну группу; m - количество групп входных шин устройства), блок сумми

рованйя представляет собой узел суммирования п) унитарных кодов и двоичный шифратор, выходы которого подключены к выходным шинам устройства, а.входы подключены к выходам узла , суммирования унитарных кодов, входы которого подключены к выходам соответствующих преобразователей двоичных кодов в унитарные коды, входы каждого из которых соединены с k входными шинаьш устройства.

Кроме того, узел суммирования унитарных кодов содержит сумматоры уни. тарных кодов, образующих пирамиду 5 из 1092 m рядов, причем сумматЬры

унитарных кодов первого ряда, соединены со входами узла суммирования унитарных кодов, взятыми попарно, сумматор каждого последующего ряда соеди0нен входами с выходами попарно взятых сумматоров предьщущего ряда, выход сумматора последнего ряда является выходом узла суммирования m унитарных кодов.

5

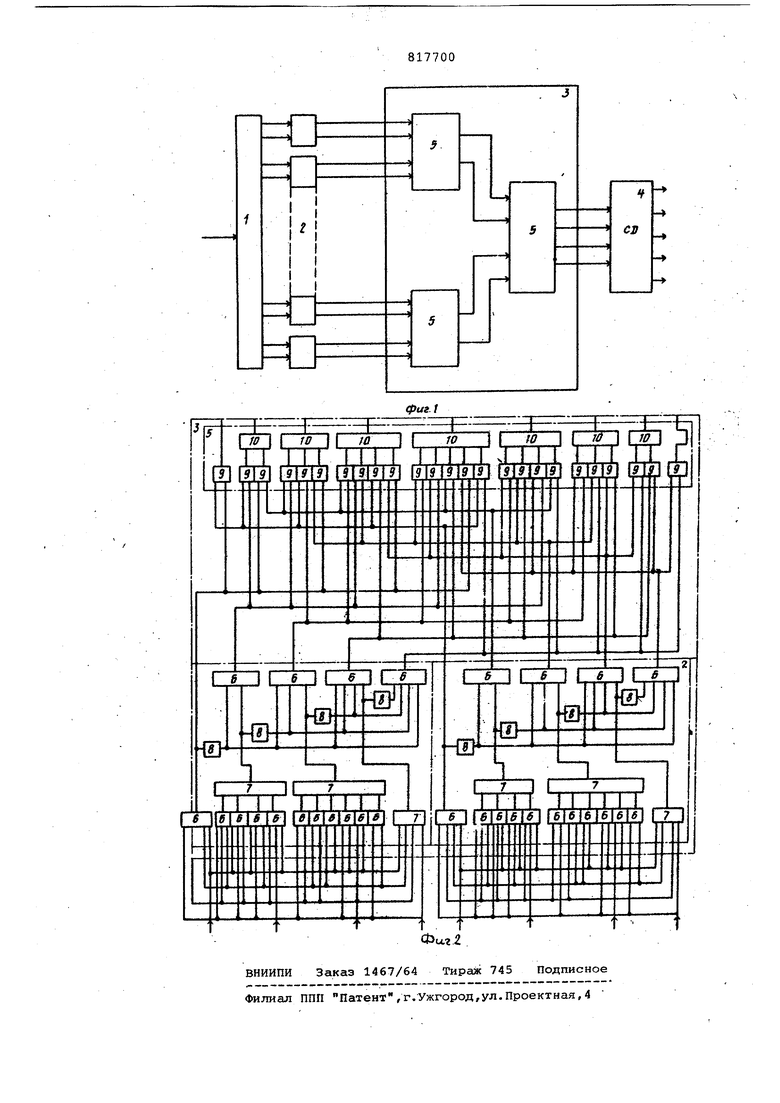

На фиг. 1 представлена схема устройства, на фиг. 2 - пример выполнения преобразователей двоичных кодов в унитарные коды и узла суммирования унитарных кодов при m « 2, k

0 . 1 (узел суммирования в этсял случае

содержит единственный сул1матор унитарных кодов).

Устройство содержит регистр 1, в котором записано исходное п-разрядно двоичное слово (п одноразрядных двоичных чисел), и собственно образующие устройство преобразователи 2 двоичных кодов в унитарные коды,узел 3 суммирования унитарных кодов и шифратор 4 . Узел 3 суммирования унитарных кодов выполнен в виде пирамиды сумматоров 5 унитарных кодов,

Приме р.При выполнении преобразователей 2 и узла 3 для случая m 2, k , n m.k 8, устройство содержит два преобразователя 2 двоичных кодов в унитарные коды, выполненные на элементах И 6, ИЛИ 1, НБ 8, ив состав узла 3 суммирования унитарных кодов входит в этом случае единственный сумматор 5 унитарных кодов, выполненный в виде матрицы двухвходовых элементов И 9, выходы элементов И 9, кавдой диагонали матрицы объединены одним элементом ИЛИ 10. Каждый из двух преобразователей 2 преобразует двоичную четырехразрядную комбинацию на своем входе в сигнал на одном из своих пяти выходов, наличие которого указывает, сколько единиц содержится во . входной комбинации.

Устройство работает следующим образом.

Перед началом суммирования п одноразрядные двоичные числа в виде п-разрядного двоичного слова зацесены в регистр 1. Разряды регистра 1 разбиты на m групп по k разрядов в каждой (т k п). Выходы каждой группы разрядов регистра 1 подключены ко входам соответствукяцего преобразователя 2 двоичного кода в унитарный, который преобразует двоичное предста ление данной группы двоичных разрядов в сигнал на одном из своих выходов. Образованные таким образом m унитарных кодов суммируются узлом 3 (построенным, например, по пирамидальной схеме). Результат образованный на выходе узла 3 в унитарном коде, преобразуется двоичным шифратором 4 в параллельный двоичный код, значение которого показывает число разрядов регистра 1, в которых было

Входами устзаписано значение

ройства являются входы преобразователей 2, а выходами - зыходы шифратора 4 .

Используя для построения преобразователей 2, узла 3 и шифратора 4 логические элементы с згщержкой наносекундного диапазона, быстродействие для подсчета количества единиц в 816-, 32,-64-, и 128-разрядных словах составляет соответственно 12, 16,. 20, 24 и 28 НС, что примерно в 2-3 раза выше, чем в известном устройстве, одноразрядные сумматоры которого, образукяцие многокаскадную схему, выполнены на таких же элементах. Объем оборудования предлагаемого и известного устройств примерно одинаков.

формула изобретения

i 1. Устройство для суммирования п одноразрядных двоичных чисел, содержащее блок суммирования, о т л и чаюс ееся тем, что с целью повышения быстродействия, оно содержит m преобразователей двоичных кодов в унитарные коды количества единиц (т п(к, где k - количество входных шин устройства, образующих одну группу, m - количество групп входных

5 шин устройства), блок суммирования представляет собой узел суммирования m унитарных кодов и двоичный шифратор, выходы которого подключены к выходным шинам устройства, а входы подключены к выходам узла суммирования унитарных кодов, входы которого подключены к выходам соответствующих преобразователей двоичных кодов в унитарные коды входы каждого из которых соединены с k входными шинами устройства.

0 пирамиду из log 2 in РЯДОВ, причем сумматоры унитарных кодов первого ряда соединены со входами узла суммирования унитарных кодов, взятыми попарно, .сумматор каждого последующего ряда соединен входами с выходами попарно взятых сумматоров предыдущего ряда, выход.сумматора последнего ряда является выходом узла суммирования m унитарных кодов.

Источники информации, принятые во внимание при экспертизе

5 1974, вып. 9, с. 94-98.

Авторы

Даты

1981-03-30—Публикация

1979-05-28—Подача