ванием Р 2. Перестройка основания системы счисления осуществляется подачей кода основания, записанного ,в двоично-Р-ичном коде. Делимое и делитель выражены в прямом Р-ичном коде. В каждом такте определяется одна Р-ичная цифра частного. Для этого одновременно вычисляются Р - кратных делителю в дополнительном коде и Р - 1 сумма этих кратных с положительным значением предыдущего остатка, .выраженного в виде двух чисел. Результатом вычисления сумм являются остатки в виде двух чисел, по знакам которых определяются очередная цифра частного и очередной

1

Изобретение относится к области вычислительной техники и предназначено для деления чисел, представленных в любой Р-ичной системе счисления с основанием больше двух.

Целью изобретения чт ляется расширение функционапьных возможностей за счет возможности выполнения операции деления с любым основанием системы счисления.

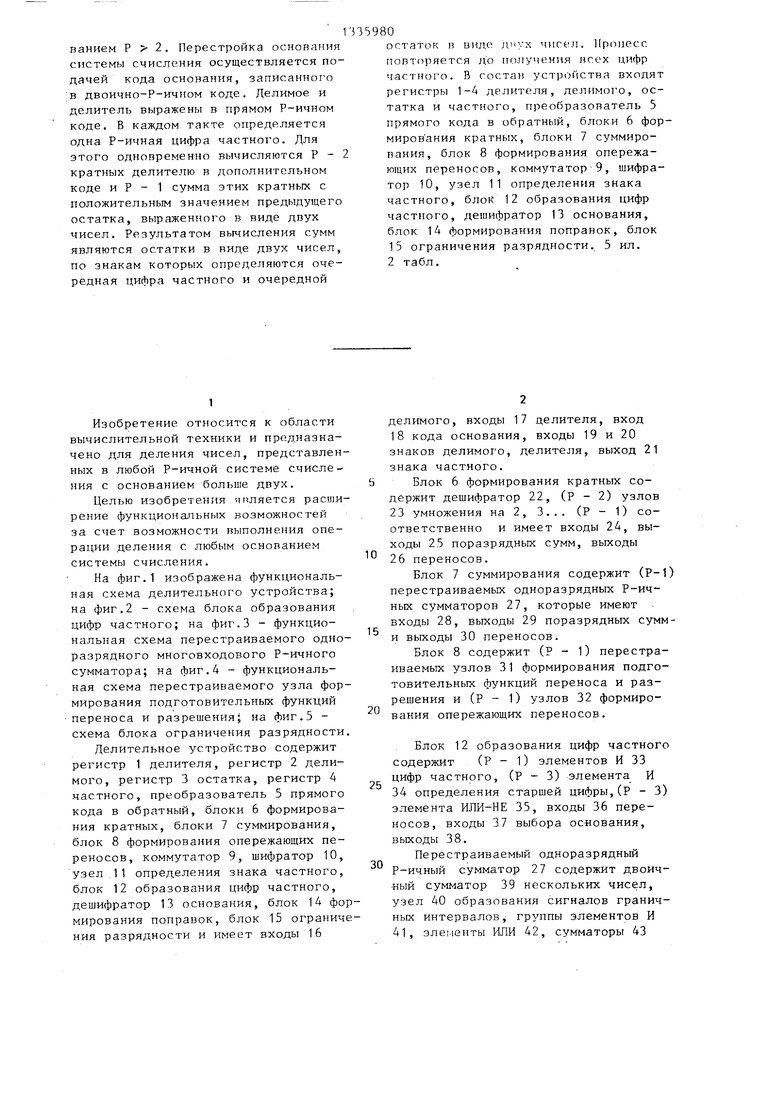

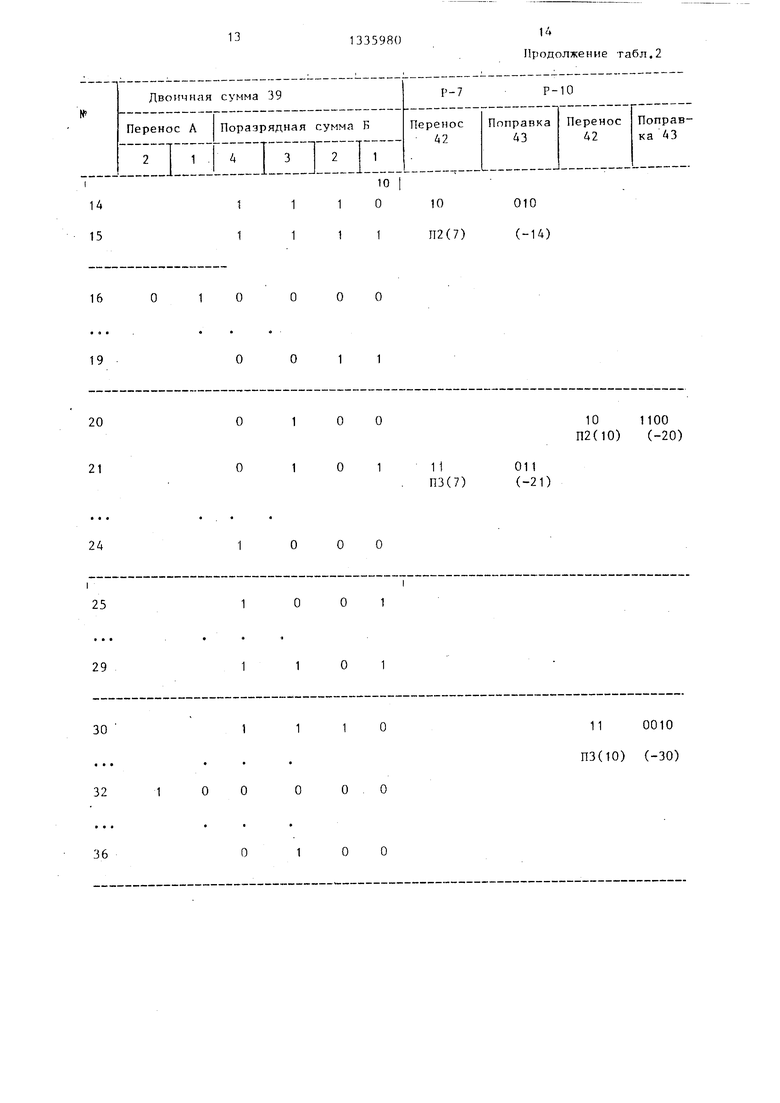

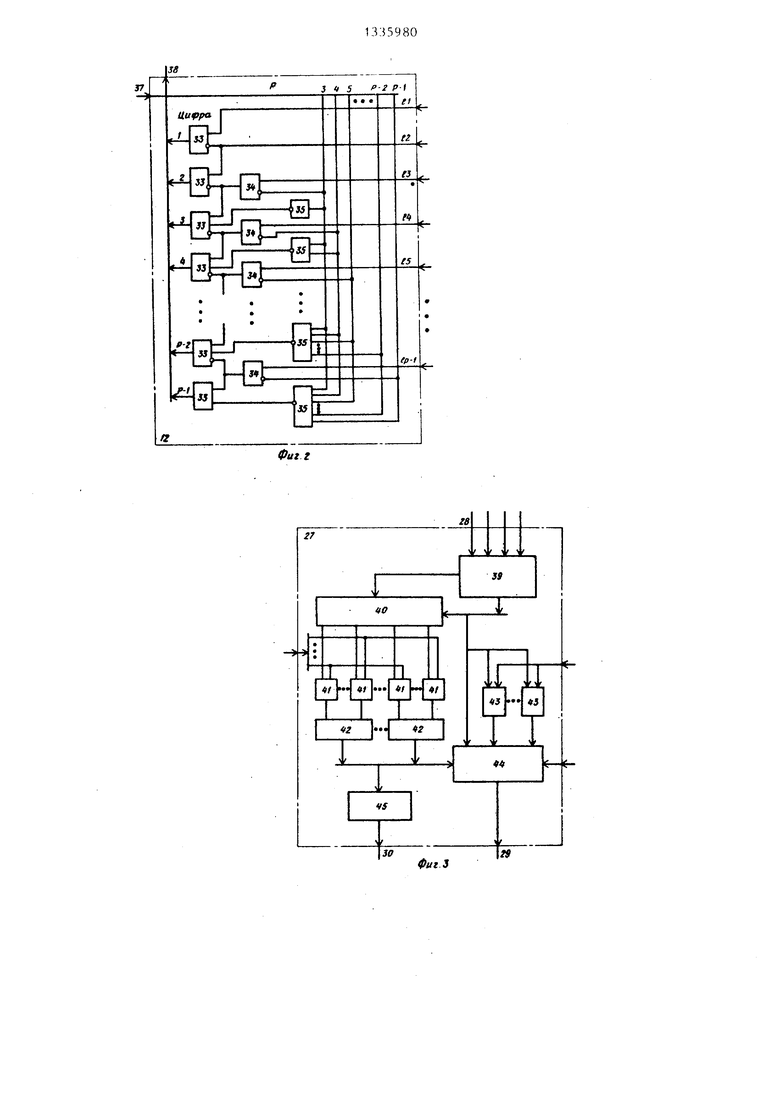

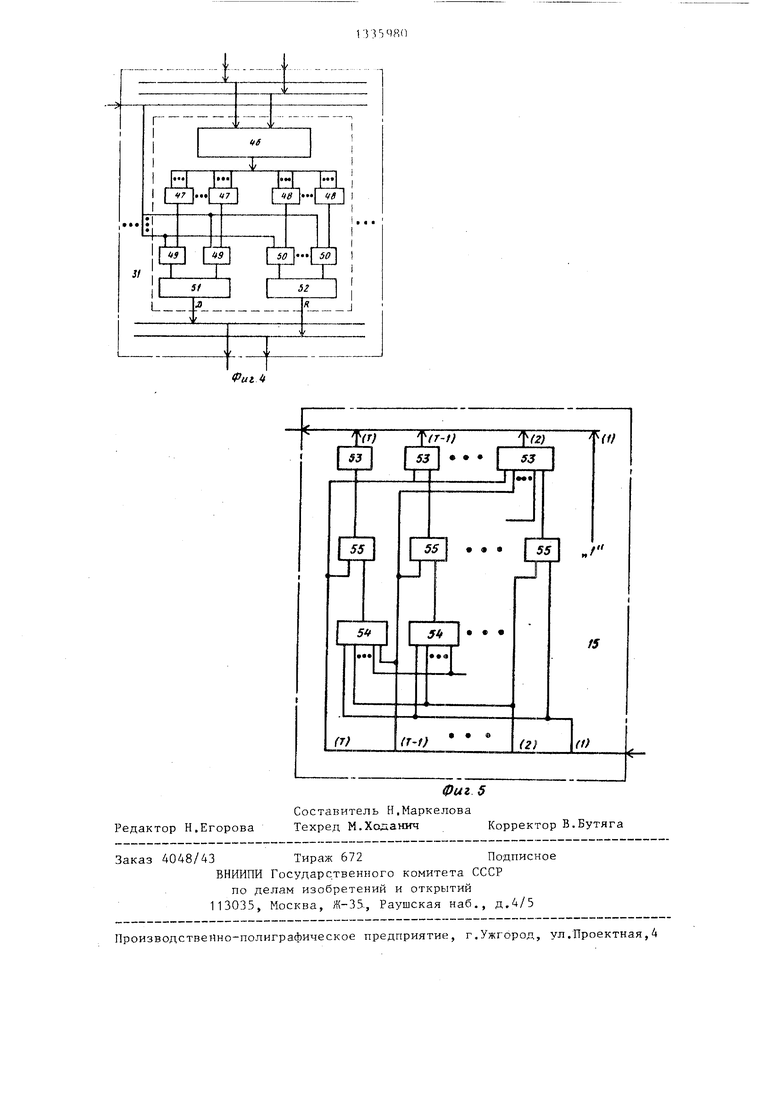

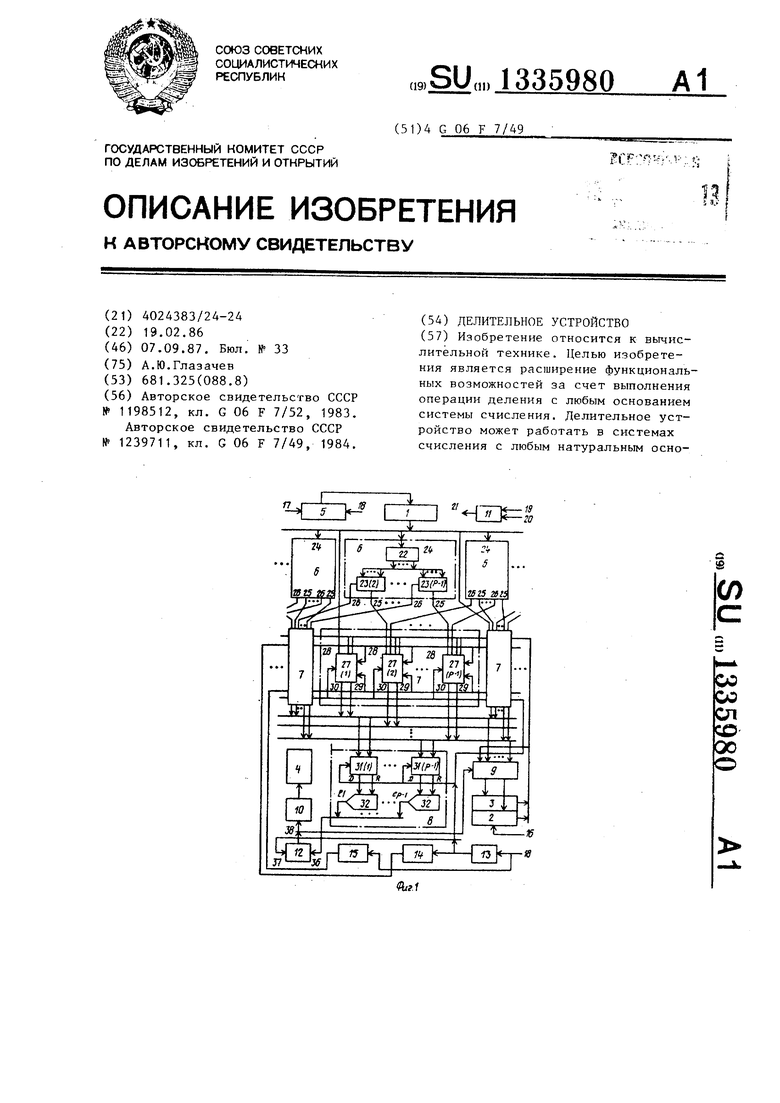

На фиг.1 изображена функциональная схема делительного устройства; на фиг.2 - схема блока образования цифр частного; на фиг.З - функциональная схема перестраиваемого одноразрядного многовходового Р-ичного сумматора; на фиг.4 - функциональная схема перестраиваемого узла формирования подготовительных функций переноса и разрешения; на фиг.З - схема блока ограничения разрядности

Делительное устройство содержит регистр 1 делителя, регистр 2 делимого, регистр 3 остатка, регистр 4 частного, преобразователь 5 прямого кода в обратный, блоки 6 формирования кратных, блоки 7 суммирования, блок 8 формирования опережающих переносов, коммутатор 9, шифратор 10, узел ,11 определения знака частного, блок 12 образования цифр частного, дешифратор 13 основания, блок 14 фомирования поправок, блок 15 ограничния разрядности и имеет входы 16

35980

остаток в виде диух чпсел. Процесс повторяется до гтолучения tjcex цифр частного. В состав устройства входят регистры 1-А делителя, делимого, остатка и частного, преобразователь 5 прямого кода в обратный, блоки 6 фор- миров ания кратных, блоки 7 суммирования, блок 8 формирования опережающих переносов, коммутатор9, шифратор 10, узел 11 определения знака частного, блок 12 образования цифр частного, дешифратор 13 основания, блок 14 формирования поправок, блок 15 ограничения разрядности. 5 ил. 2 табл.

делимого, входы 17 делителя, вход 18 кода основания, входы 19 и 20 знаков делимого, делителя, выход 21 знака частного.

Блок 6 формирования кратных содержит дешифратор 22, (Р - 2) узлов 23 умножения на 2, 3... (Р - 1) соответственно и имеет входы 24, выходы 25 поразрядных сумм, выходы

26 переносов.

Блок 7 суммирования содержит (Р-1) перестраиваемых одноразрядных Р-ич- ных сумматоров 27, которые имеют . входы 28, выходы 29 поразрядных сумм- и выходы 30 переносов.

Блок 8 содержит (Р - 1) перестраиваемых узлов 31 формирования подготовительных функций переноса и разрешения и СР - 1) узлов 32 формирования опережающих переносов.

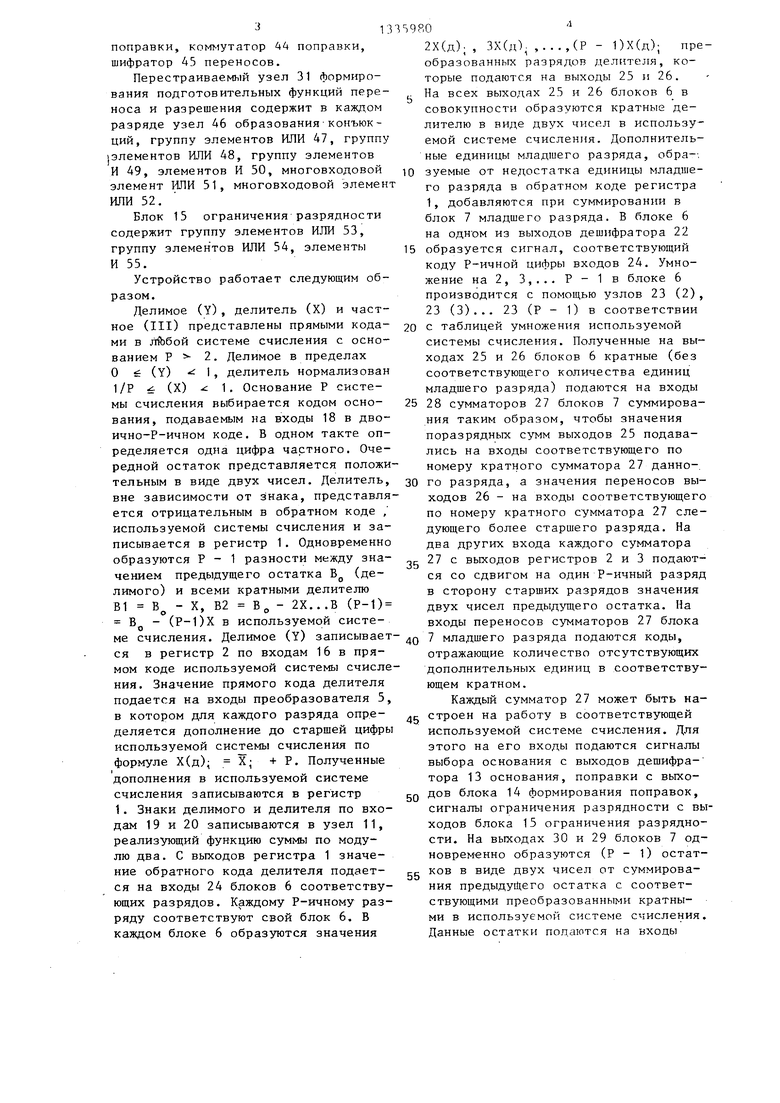

Блок 12 образования цифр частного содержит (Р - 1) элементов И 33 цифр частного, (Р - 3) элемента И 34 определения старшей цифры,(Р - 3) элемента ИЛИ-НЕ 35, входы 36 переносов, входы 37 выбора основания, выходы 38.

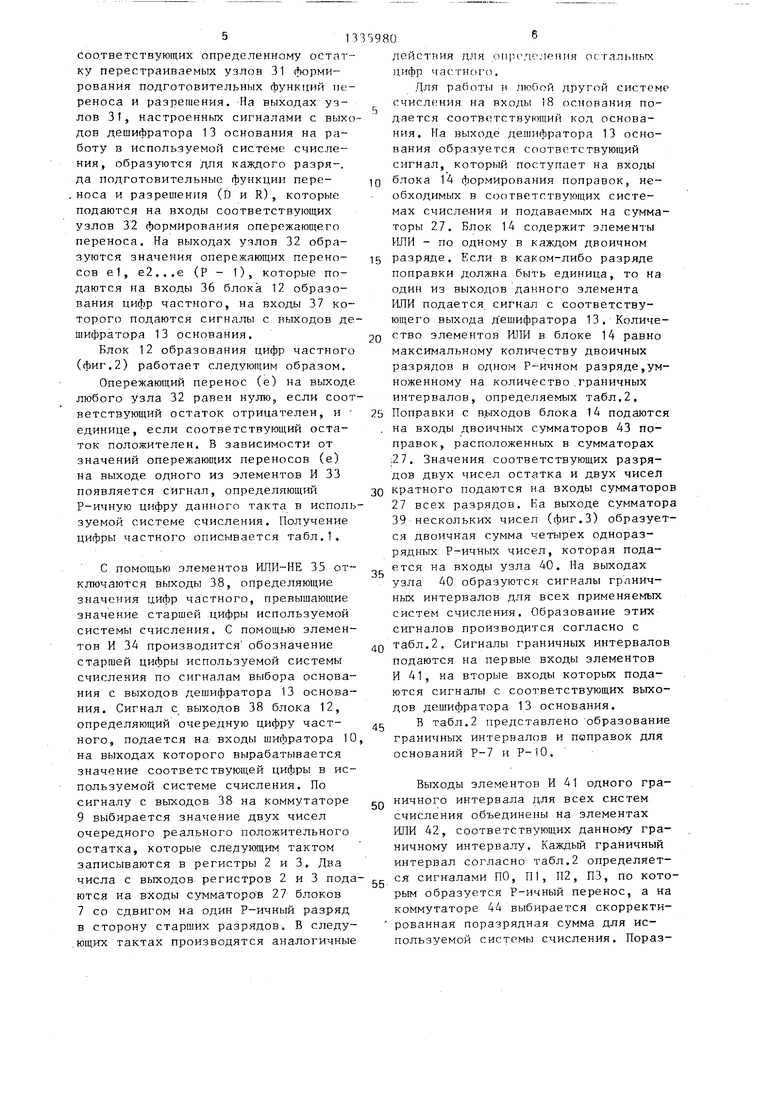

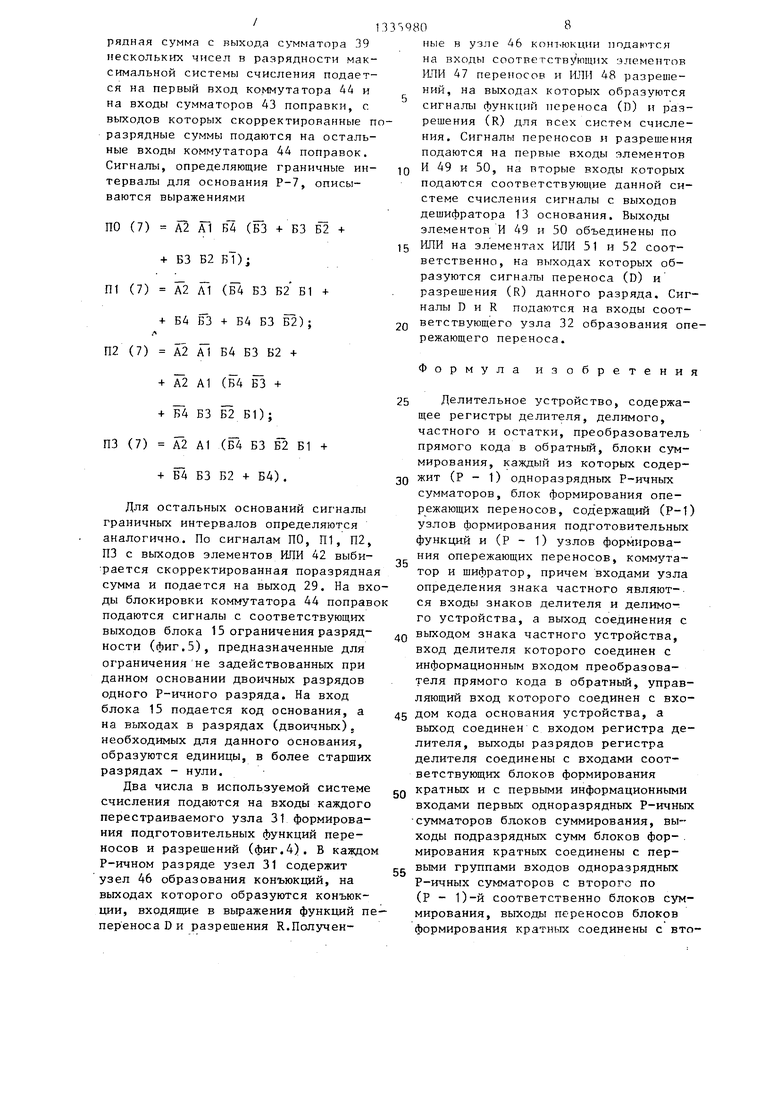

Перестраиваемый одноразрядный Р-ичный сумматор 27 содержит двоичный сумматор 39 нескольких чисел, узел 40 образования сигналов граничных интервалов у группы элементов И 41, эле -1енты ИЛИ 42, сумматоры 43

3

поправки, коммутатор 44 поправки, шифратор 45 переносов.

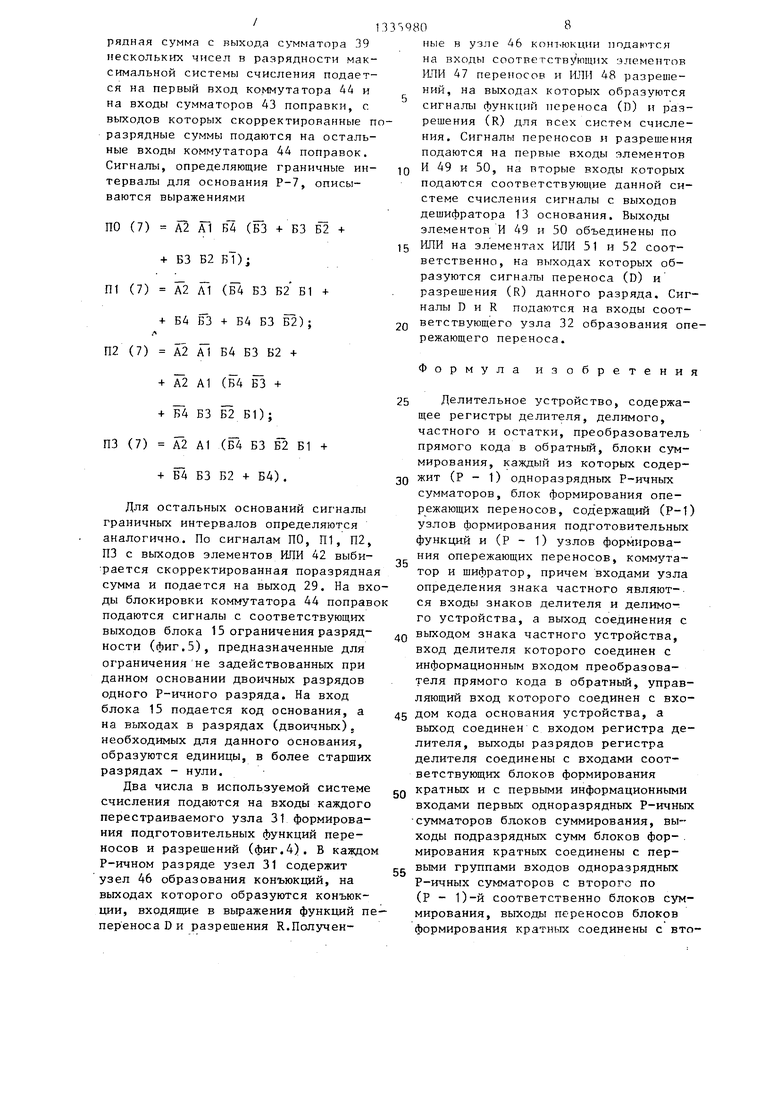

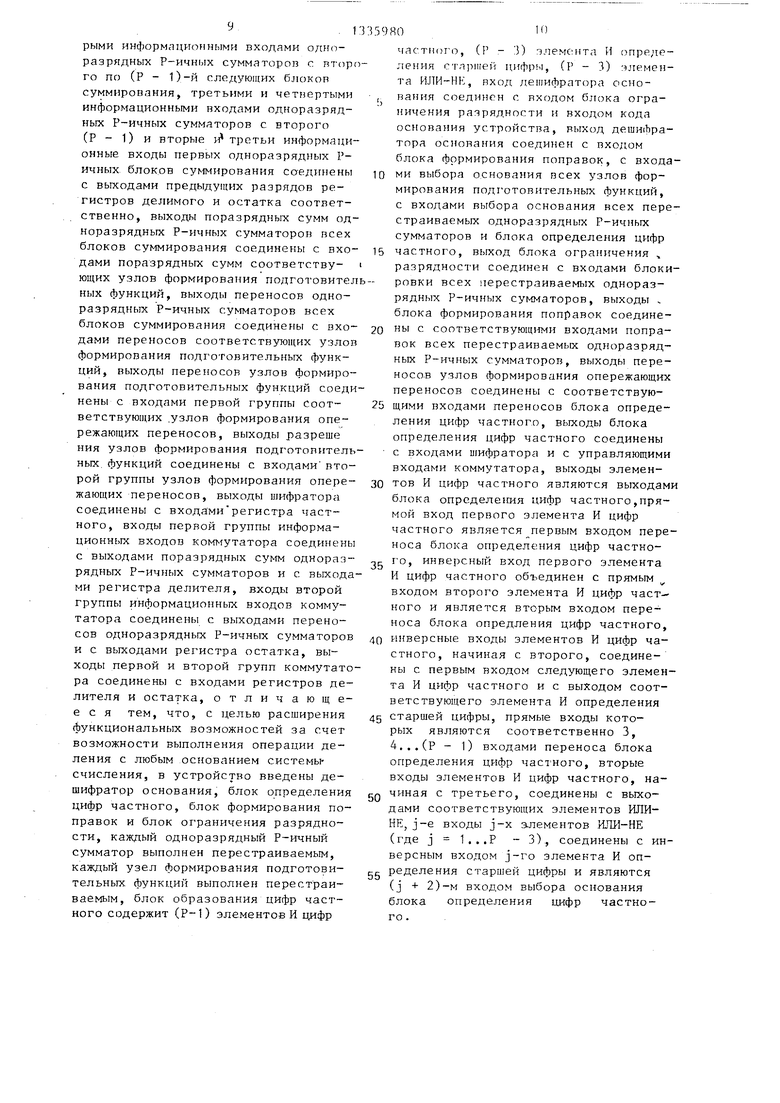

Перестраиваемый узел 31 формирования подготовительных функций переноса и разрешения содержит в каждом разряде узел 46 образования-конъюк- ций, группу элементов ИЛИ 47, группу |элементов ИЛИ 48, группу элементов И 49, элементов И 50, многовходовой элемент ИЛИ 51, многовходовой элемен ИЛИ 52.

Блок 15 ограничения разрядности содержит группу элементов ИЛИ 53, группу элементов ИЛИ 54, элементы И 55.

Устройство работает следующим образом.

Делимое (Y), делитель (Х) и частное (III) представлены прямыми кодами в лЙ)бой системе счисления с основанием Р 2. Делимое в пределах О (Y) I , делитель нормализован 1/Р (X) 1, Основание Р системы счисления выбирается кодом основания, подаваемым на входы 18 в дво- ично-Р-ичном коде. В одном такте определяется одна цифра частного. Очередной остаток представляется положительным в виде двух чисел. Делитель, вне зависимости от знака, представляется отрицательным в обратном коде , используемой системы счисления и записывается в регистр 1. Одновременно образуются Р - 1 разности между значением предыдущего остатка Б, (делимого) и всеми кратными делителю В1 В - X, В2 В„ - 2Х...В (Р-1) В - (Р-1)Х в используемой системе счисления. Делимое (Y) записывается в регистр 2 по входам 16 в прямом коде используемой системы счисления. Значение прямого кода делителя подается на входы преобразователя 5, в котором для каждого разряда определяется дополнение до старшей цифры используемой системы счисления по формуле Х(д); X; + Р. Полученные дополнения в используемой системе счисления записываются в регистр 1. Знаки делимого и делителя по входам 19 и 20 записываются в узел 11, реализующий функцию суммы по модулю два. С выходов регистра 1 значение обратного кода делителя подается на входы 24 блоков 6 соответствующих разрядов. Каждому Р-ичному разряду соответствуют свой блок 6, В каждом блоке 6 образуются значения

Tsg80

2Х(д),

10

ЗХ(д), ,...,( - 1)Х(д); прея11

образованных разрядов делителя, которые подаются на выходы 25 и 26. На всех выходах 25 и 26 блоков 6 в совокупности образуются кратные делителю в виде двух чисел в используемой системе счисления. Дополнительные единицы младшего разряда, обра--, зуемые от недостатка единицы младшего разряда в обратном коде регистра 1, добавляются при суммировании в блок 7 младшего разряда. В блоке 6 на одн-ом из выходов дешифратора 22

15 образуется сигнал, соответствующий коду Р-ичной цифры входов 24. Умножение на 2, 3,...Р-1в блоке 6 производится с помощью узлов 23 (2), 23 (3)... 23 (Р - 1) в соответствии

20 с таблицей умножения используемой системы счисления. Полученные на выходах 25 и 26 блоков 6 кратные (без соответствующего количества единиц младшего разряда) подаются на входы

25 28 сумматоров 27 блоков 7 суммирования таким образом, чтобы значения поразрядных сумм выходов 25 подавались на входы соответствующего по номеру кратного сумматора 27 данно-,

30 го разряда, а значения переносов выходов 26 - на входы соответствующего по номеру кратного сумматора 27 следующего более старшего разряда. На два других входа каждого сумматора 27 с выходов регистров 2 и 3 подаются со сдвигом на один Р-ичный разряд в сторону старших разрядов значения двух чисел предыдущего остатка. На входы переносов с-умматоров 27 блока 7 младшего разряда подаются коды, отражающие количество отсутствующих дополнительных единиц в соответствующем кратном.

Каждый сумматор 27 может быть на45, строен на работу в соответствующей используемой системе счисления. Для этого на его входы подаются сигналы выбора основания с выходов дешифра- тора 13 основания, поправки с выхоgQ дов блока 14 формирования поправок, сигналы ограничения разрядности с выходов блока 15 ограничения разрядности. На выходах 30 и 29 блоков 7 од- новрем-енно образуются (Р - 1) остатков в виде двух чисел от суммирования предыдущего остатка с соответствующими преобразованными кратными в используемой системе счисления. Данные остатки подаются на входы

35

40

55

5133

соответствующих определенному остатку перестраиваемых узлов 31 формирования подготовительных функций переноса и разрешения. На выходах узлов 31, настроенных сигналами с выходов дешифратора 13 основания на работу в используемой системе счисления, образуются для каждого разря-, да подготовительные функции пере- носа и разрешения (Ь и R), которые подаются на входы соответствующих узлов 32 формирования опережающего переноса. На выходах узлов 32 образуются значения опережающих переносов e1, е2...е (Р - 1), которые поаются на входы 36 блока 12 образования цифр частного, на входы 37 которого подаются сигналы с выходов деифратора 13 основания.

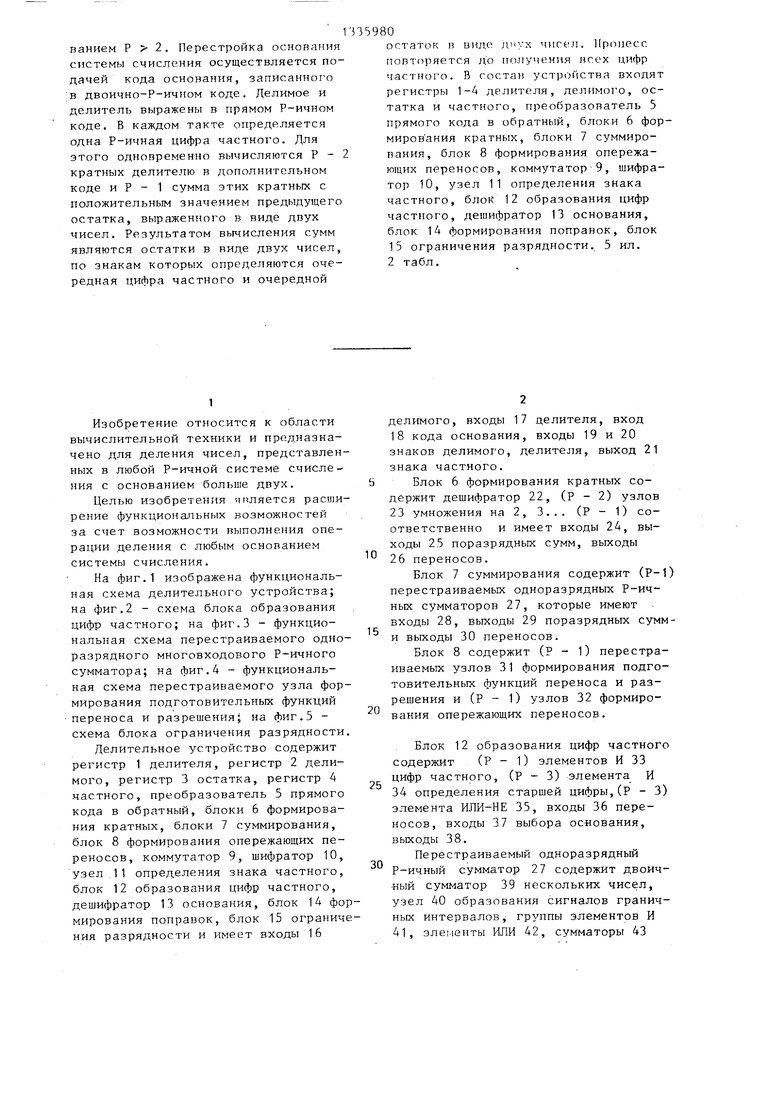

Блок 12 образования цифр частного (фиг.2) работает следующим образом.

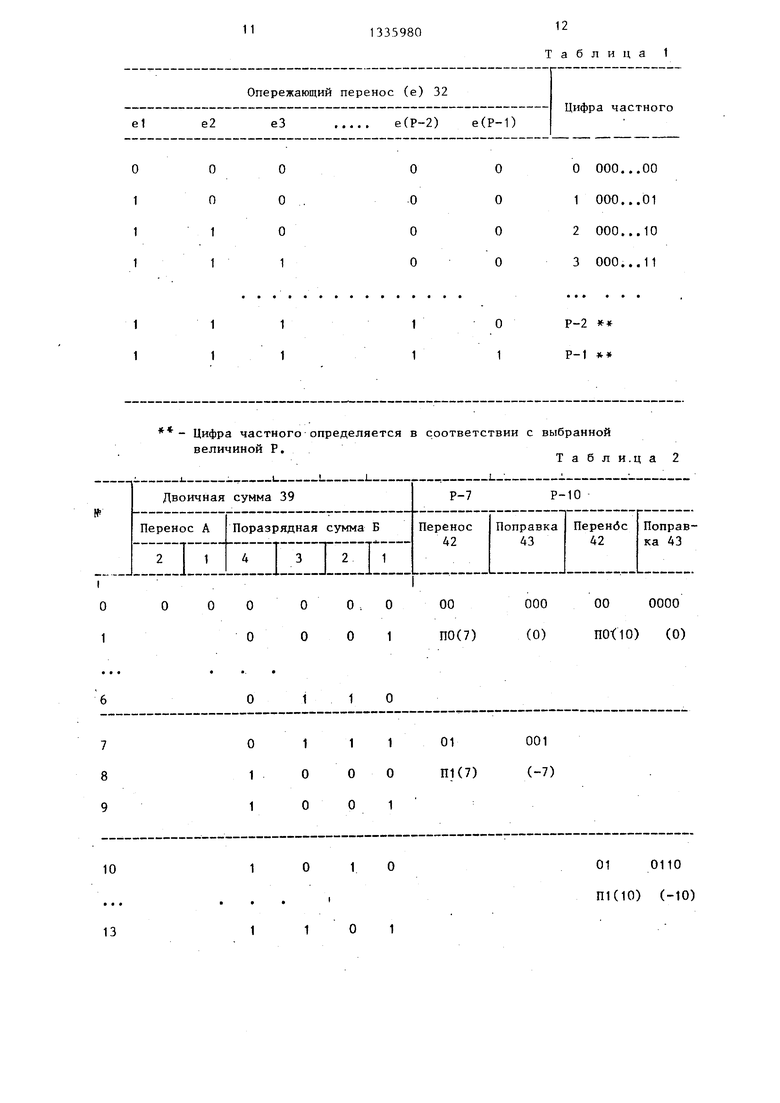

Опережающий перенос (е) на выходе любого узла 32 равен нулю, если соответствующий остаток отрицателен, и единице, если соответствующий остаток положителен. В зависимости от значений опережающих переносов (е) на выходе одного из элементов И 33 появляется сигнал, определяющий Р-ичную цифру данного такта в используемой системе счисления. Получение цифры частного описывается табл.1,

С помощью элементов ИЛИ-НЕ 35 отключаются выходы 38, определяющие значения цифр частного, превышающие значение старшей цифры используемой системы счисления. С помощью элементов И 34 производится обозначение старшей цифры используемой системы счисления по сигналам выбора основания с выходов дешифратора 13 основания. Сигнал с выходов 38 блока 12, определяющий очередную цифру частного, подается на входы шифратора 10, на выходах которого вырабатывается значение соответствующей цифры в исользуемой системе счисления. По игналу с выходов 38 на коммутаторе 9 выбирается значение двух чисел очередного реального положительного остатка, которые следующим тактом записываются в регистры 2 и 3. Два исла с выходов регистров 2 и 3 податся на входы сумматоров 27 блоков 7 со сдвигом на один Р-ичный разряд сторону старших разрядов. В следу- щих тактах производятся аналогичные

действия для опрелеления остальных цифр частнс)го.

Для работы н любой другой системе

счисления на входы 18 г)снования по

дается соответствующий код основания. На выходе дешифратора 13 основания образуется соответствующий сигнал, который поступает на входы

блока 14 формирования поправок, необходимых в соответствующих системах счисления и подаваемых на сумматоры 27. Блок 14 содержит элементы ШШ - по одному в каждом двоичном

разряде. Если в каком-либо разряде поправки должна быть единица, то на один из выходов данного элемента ИЛИ подается сигнал с соответствующего выхода Дешифратора 13. Количество элементов РИТИ в блоке 14 равно максимальному количеству двоичных разрядов в одном Р-ичном разряде,умноженному на количество .граничных интервалов, определяемых табл.2,

Поправки с в.ыходов блока 14 подаются на входы двоичных сумматоров 43 поправок, расположенных в сумматорах ;27. Значения соответствующих разрядов двух чисел остатка и двух чисел

кратного подаются на входы сумматоров 27 всех разрядов. Ка выходе сумматора 39 нескольких чисел (фиг.З) образуется двоичная сумма четырех одноразрядных Р-ичных чисел, которая подается на входы узла 40. На выходах узла 40 образуются сигналы граничных интервалов для всех применяемых систем счисления. Образование этих сигналов производится согласно с

табл.2. Сигналы граничных интервалов подаются на первые входы элементов И 41, ка вторые входы которых подаются сигналы с соответствующих выходов дешифратора 13 основания.

45

В табл.2 представлено образование граничных интервалов и поправок для оснований Р-7 и Р-10.

0

Выходы элементов И 41 одного граничного интервала для всех систем счисления объединены на элементах ИЛИ 42, соответствующих данному граничному интервалу. Каждый граничный интервал согласно табл.2 определяется сигналами ПО, П1, П2, ПЗ, по которым образуется Р-ичный перенос, а на коммутаторе 44 выбирается скорректи- рованная поразрядная сумма для используемой системы счисления. Пораз/

рядная сумма с выхода сумматора 39 нескольких чисел в разрядности максимальной системы счисления подается на первый вход коммутатора А4 и на входы сумматоров 43 поправки, с выходов которых скорректированные празрядные суммы подаются на остальные входы коммутатора 44 поправок. Сигналы, определяющие граничные интервалы для основания Р-7, описываются выражениями

ПО (7) А2 П Б4 (БЗ + БЗ Б2 +

+ БЗ Б2 вТ); П1 (7) А2 М (Б4 БЗ Б2 Б1 +

+ Б4 БЗ + Б4 БЗ Б2);

л

П2 (7) А2 А Б4 БЗ Б2 +

+ А2 А1 (Б4 БЗ +

f Б4 БЗ Б2 Б1); ПЗ (7) А2 А1 (Б4 БЗ Б2 Б1 +

+ Б4 БЗ Б2 + Б4).

Для остальных оснований сигналы граничных интервалов определяются аналогично. По сигналам ПО, П1, 02, ПЗ с выходов элементов ИЛИ 42 выби- рается скорректированная поразрядна сумма и подается на выход 29. На вхды блокировки коммутатора 44 поправ подаются сигналы с соответствующих выходов блока 15 ограничения разрядности (фиг.5), предназначенные для ограничения не задейетвованньк при данном основании двоичных разрядов одного Р-ичного разряда. На вход блока 15 подается код основания, а на выходах в разрядах (двоичных). необходимых для данного основания, образуются единицы, в более старших разрядах - нули.

Два числа в используемой системе счисления подаются на входы каждого перестраиваемого узла 31 формирования подготовительных функций переносов и разрешений (фиг.4). В каждо Р-ичном разряде узел 31 содержит узел 46 образования конъюкций, на выходах которого образуются конъюкций, входящие в выражения функций п переноса D и разрешения К.Получен0

ные в узле 46 кош.юкции подаются на входы соответствующих элементов ИЛИ 47 переносов и ИЛИ 48 разрешений, на выходах которых образуются сигналы функций переноса (D) и разрешения (R) для всех систем счисления. Сигналы переносов и разрешения подаются на первые входы элементов

И 49 и 50, на вторые входы которых подаются соответствующие данной системе счисления сигналы с выходов дешифратора 13 основания. Выходы элементов И 49 и 50 объединены по

ИЛИ на элементах ИЛИ 51 и 52 соответственно, на выходах которых образуются сигналы переноса (D) и разрешения (R) данного разряда. Сигналы D и R подаются на входы соответствующего узла 32 образования опережающего переноса.

Формула изобретения

Делительное устройство, содержащее регистры делителя, делимого, частного и остатки, преобразователь прямого кода в обратный, блоки суммирования, каждый из которых содер- жит (Р - 1) одноразрядных Р-ичньгх сумматоров, блок формирования опережающих переносов, сод ержащий (Р-1) узлов формирования подготовительных функций и (Р - 1) узлов формирования опережающих переносов, коммутатор и шифратор, причем входами узла определения знака частного являют-, ся входы знаков делителя и делимого устройства, а выход соединения с выходом знака частного устройства, вход делителя которого соединен с информационным входом преобразователя прямого кода в обратный, управляющий вход которого соединен с вхо- дом кода основания устройства, а

выход соединен с входом регистра делителя, выходы разрядов регистра делителя соединены с входами соответствующих блоков формирования кратных и с первыми информационными входами первых одноразрядных Р-ичньгх сумматоров блоков суммирования, выходы подразрядных сумм блоков формирования кратных соединены с первыми группами входов одноразрядных Р-ичных сумматоров с второго по (Р - 1)-й соответственно блоков суммирования, выходы переносов блоков формирования кратных соединены с вто

. t

рыми информационными входами одноразрядных Р-ичных сумматоров с второго по (Р - 1)-и следующих блокоп суммирования, третьими и четвертыми информационными входами одноразрядных Р-ичных сумматоров с второго (Р - 1) и вторые и третьи информационные входы цервых одноразрядных Р- ичных, блоков суммирования со еди 1ены с выходами предыдущих разрядорз регистров делимого и остатка соответственно, выходы поразрядных сумм одноразрядных Р-ичных сумматоров всех блоков суммирования соединены с входами поразрядных сумм соответству- ющих узлов формирования подготовител ных функций, выходы переносов одноразрядных Р-ичных сумматоров всех блоков суммирования соединены с входами переносов соответствующих узлов формирования подготовительных функций, выходы переносов узлов формирования подготовительных функций соединены с входами первой группы соответствующих .узлов формирования опережающих переносов, выходы разреше ния узлов формирования подготовительных, функций соединены с входами второй группы узлов формирования опережающих переносов, выходы шифратора соединены с входами регистра частного, входы первой группы информа- ционнЕ гх входов коммутатора соединены с выходами поразрядных cyt-m одноразрядных Р-ичных сумматоров и с выходами регистра делителя, входы второй группы информационных входов коммутатора соединены с выходами переносов одноразрядных Р-ичных сумматоров и с выходами регистра остатка, выходы первой и второй групп коммутатора соединены с входами регистров делителя и остатка, отличающееся тем, что, с целью расширения функциональных возможностей за счет возможности выполнения операции деления с любым основанием системы- счисления, в устройство введены дешифратор основания, блок определения цифр частного, блок формирования поправок и блок ограничения разрядности, каждый одноразрядный Р-ичный сумматор выполнен перестраиваемым, каждый узел формирования подготовительных функций выполнен перестраиваемым, блок образования цифр частного содержит (Р-1) элементов И цифр

59ЯО

частнпг о, (Р - 3) з.пемс:кта Н определения стл 1111ей цифры, (Р - 3) элемента ИЛИ-НЕ, вход дешифратора осноJ вания соединен с входом блсзка ограничения разрядности и входом кода основания устройства, выход деши||1ра- тора основания соединен с входом блока формирования поправок, с входа10 ми выбора основания всех узлов формирования подг отовительных функций, с входами выбора основания всех перестраиваемых одноразрядных Р-ичных сумматоров и блока определения цифр

15 частного, блока ограничения , разрядности соединен с входами блокировки всех перестраиваемь х одноразрядных Р-ичных сумматоров, выходы . блока формирования поправок соедине0 ны с соответствующими входами поправок всех перестраиваемых одноразрядных Р-ичных сумматоров, выходы переносов узлов формирования опережающих переносов соединены с соответствую25 щими входами переносов блока определения цифр частного, выходы блока определения цифр частного соединены с входами шифратора и с управляющими входами коммутатора, выходы элемен30 тов И цифр частного являются выходами блока определе гия цифр частного , прямой вход первого элемента И цифр частного является первым входом переноса блока определения цифр частно.,(- г о, инверсный вход первого элемента И цифр частного объединен с прямым входом второго элемента И цифр частного и является вторым входом переноса блока опредления цифр частного,

40 инверсные входы элементов И цифр частного, начиная с второго, соединены с первым входом следующего элемента И цифр частного и с выходом соответствующего элемента И определения

45 старшей цифры, прямые входы которых являются соответственно 3, 4...(Р - 1) входами переноса блока определения цифр частного, вторые входы элементов И цифр частного, начиная с третьего, соединены с выходами соответствующих элементов ИЛИ- НЕ, j-e входы J-X элементов ИЛИ-НЕ (где j 1...Р - 3), соединены с инверсным входом j-ro элемента И опсс ределения старшей цифры и являются (J + 2)-м входом выбора основания блока определения цифр частного .

50

Опережающий перенос (е) 32

el

е2

еЗ

О П 1 1

О О О

1

- Цифра частного определяется в соответствии с выбранной

величиной Р.

Табли.ца2

10

Таблица 1

е(Р-2)е(Р-1)

Цифра частного

О О О О

О

1

0000...00

1000...01

2000...10

3000... 11

р-2

1 О

010110

П1(10) (-10)

15

111П2(7)(-14)

16010000

19

О011

20

О100

21

О101

24

1000

25

1001

29

1101

30

11

32100О00

36

о100

101100

П2(10) (-20)

11 П3(7)

011 (-21)

110010

П3(10) (-30)

| название | год | авторы | номер документа |

|---|---|---|---|

| Делительное устройство | 1984 |

|

SU1239711A1 |

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| Устройство для деления | 1980 |

|

SU928344A1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Устройство для деления десятичных чисел | 1984 |

|

SU1241235A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| Матричное устройство для деления | 1985 |

|

SU1247863A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1234831A1 |

| Арифметическое устройство | 1985 |

|

SU1550510A1 |

Изобретение относится к вычислительной технике. Целью изобретения является расширение функциональных возможностей за счет выполнения операции деления с любым основанием системы счисления. Делительное устройство может работать в системах счисления с любым натуральным осно 41: 1 (Л

фиг 3

19

I I t7 ... Ц7

31

Sf

0

L

Редактор Н.Егорова

Фиг 5

Составитель Н.Маркелова Техред М.Ходанич

Заказ А048/43 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35., Раушская наб,, д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

Корректор В.Бутяга

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Делительное устройство | 1984 |

|

SU1239711A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-07—Публикация

1986-02-19—Подача